一种宽输入范围的时间放大器的制作方法

1.本发明涉及模拟集成电路技术领域,特别是涉及一种宽输入范围的时间放大器。

背景技术:

2.tdc(timeto digital converter,时间数字转换器)在集成电路中有着广泛的应用,是数字电路中用于同步和测量的重要单元,测量精度与量程是时间数字转换器的一个重要指标,随着集成电路的飞速发展,设计一款高性能的时间数字转换器至关重要。

3.流水线型时间数字转换器以其高分辨被广泛应用,因其“求商取余,放大余量”的工作原理成为一种广泛应用的结构,而ta(time amplifier,时间放大器)作为其中的关键模块,其增益与线性范围将直接决定流水线型时间数字转换器的性能,目前,时间放大器的结构主要分为三种,一种是基于sr锁存器的时间放大器,一种是基于闭环增益控制的时间放大器,另一种是基于二倍时间放大器2x-ta。

4.其中,基于sr锁存器的时间放大器电路利用亚稳态实现时间放大效果,其增益不可预测也不够精确,因此必须额外引入校准电路,这就增加了电路的功耗和面积,并且时间放大器的线性范围太窄,对第一级时间数字转换器的分辨率要求比较高,而且时间放大器的增益也不可调整;而基于二倍时间放大器2x-ta的增益可以较好地控制,但是其输入时间范围很小,当输入时间差增大时,增益精度就会变差,导致线性度下降;虽然基于闭环增益控制的时间放大器相比于前两种时间放大器,其增益的精确度更高,可以根据需要改变增益控制模块中缓冲器的级数来改变增益,但是同样需要采用延迟锁相环dll进行增益校准,增大了电路的面积和功耗。

技术实现要素:

5.为了解决以上技术问题,本发明提供一种宽输入范围的时间放大器,包括时间放大延迟线、时间补偿延迟线以及脉冲合并电路,时间放大延迟线的一个输入端连接有输入时间信号stop,时间放大延迟线和时间补偿延迟线的输入端均连接有输入时间信号start,时间放大延迟线和时间补偿延迟线的输出端分别与脉冲合并电路的两个输入端相连接,脉冲合并电路在感应输入时间信号stop和输入时间信号start的延迟差距之后,输出对应脉冲宽度的信号ta_out,从而对输入时间进行放大。

6.本发明进一步限定的技术方案是:进一步的,时间放大延迟线包括1个反相器inv和n个可变延迟单元,分别为可变延迟单元d1_1~可变延迟单元d1_n,其中n设置为不小于2的偶数,除可变延迟单元d1_1外每一可变延迟单元的输入端in均与上一相邻序号的可变延迟单元的输出端out相连。

7.前所述的一种宽输入范围的时间放大器,反相器inv的输入端和每个可变延迟单元的en端均分别与输入时间信号stop连接,反相器inv的输出端分别连接于每个可变延迟单元的en_n端;输入时间信号start连接于可变延迟单元d1_1的输入端in,可变延迟单元d1_n的输出端out作为整个时间放大延迟线的输出端。

8.前所述的一种宽输入范围的时间放大器,时间补偿延迟线包括n个可变延迟单元,分别为可变延迟单元d2_1~可变延迟单元d2_n,n设置为等于时间放大延迟线中可变延迟单元的数量,除可变延迟单元d2_1外每一可变延迟单元的输入端in均与上一相邻序号的可变延迟单元的输出端out相连。

9.前所述的一种宽输入范围的时间放大器,可变延迟单元d2_1的输入端in与输入时间信号start连接,可变延迟单元d2_n的输出端out作为整个时间补偿延迟线的输出端;每个可变延迟单元的en端与电源连接,en_n端则接地。

10.前所述的一种宽输入范围的时间放大器,脉冲合并电路设置为异或门电路,异或门电路的两个输入端作为脉冲合并电路的输入端,且分别与可变延迟单元d1_n的输出端out和可变延迟单元d2_n的输出端out连接;异或门电路的输出端作为脉冲合并电路的输出端。

11.前所述的一种宽输入范围的时间放大器,可变延迟单元包括8个pmos管和8个nmos管,8个pmos管分别为pmos管pm1~pmos管pm8,8个nmos管分别为nmos管nm1~nmos管nm8;其中,可变延迟单元输入端in的输入信号分别接pmos管pm1、pmos管pm2、nmos管nm1、nmos管nm2的栅极;pmos管pm1的源极与pmos管pm3的漏极相连接,pmos管pm1的漏极分别与nmos管nm1、pmos管pm2、nmos管nm2的漏极以及pmos管pm5、nmos管nm5、pmos管pm6、nmos管nm6的栅极相连接;pmos管pm2的源极与pmos管pm4的漏极相连接;pmos管pm3的栅极接地,源极接电源;pmos管pm4的栅极接可变延迟单元en端的输入信号,源极接电源;pmos管pm5的源极接pmos管pm7的漏极,漏极与nmos管nm5、pmos管pm6、nmos管nm6的漏极相连接,并作为可变延迟单元的输出端out;pmos管pm6的源极与pmos管pm8的漏极相连接;pmos管pm7的栅极接地,源极接电源;pmos管pm8的栅极接可变延迟单元en端的输入信号,源极接地;nmos管nm1的源极与nmos管nm3的漏极相连接;nmos管nm2的源极与nmos管nm4的漏极相连接;nmos管nm3的栅极接电源,源极接地;nmos管nm4的栅极接可变延迟单元en_n端的输入信号,源极接地;nmos管nm5的源极与nmos管nm7的漏极相连接;nmos管nm6的源极与nmos管nm8的漏极相连接;nmos管nm7的栅极接电源,源极接地;nmos管nm8的栅极接可变延迟单元en_n端的输入信号,源极接地。

12.前所述的一种宽输入范围的时间放大器,pmos管pm3与pmos管pm7的宽长比相同,pmos管pm1与pmos管pm5的宽长比相同,nmos管nm1与nmos管nm5的宽长比相同,nmos管nm3与nmos管nm7的宽长比相同;pmos管pm4与pmos管pm8的宽长比相同,且为pmos管pm3宽长比的k倍;pmos管pm2与pmos管pm6的宽长比相同,且为pmos管pm1宽长比的k倍;nmos管nm2与nmos管nm6的宽长比相同,且为nmos管nm1宽长比的k倍;nmos管nm4与nmos管nm8的宽长比相同,且为nmos管nm3宽长比的k倍;k即为时间放大器的增益。

13.本发明的有益效果是:本发明中,通过时间放大延迟线、时间补偿延迟线以及脉冲合并电路的设置,基于

可变延迟控制,采用时间放大感应与时间做差方案,能够实现对输入时间差的感应与放大;同时通过调整可变延迟单元级数n,能够改变时间输入范围,通过改变可变延迟单元中mos管的宽长比k,能够改变时间放大器的增益,从而在保证紧凑面积无需额外校准电路的前提下,具有更宽的输入范围与较更好的线性度,同时增益也可以方便的进行调整。

附图说明

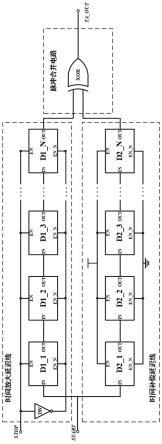

14.图1为本发明的整体结构框图;图2为本发明的电路结构图;图3为本发明中可变延迟单元的电路结构图;图4为本发明实施例1在实现4倍时间放大时的仿真图;图5为本发明实施例2的输入时间与增益关系仿真图。

具体实施方式

15.实施例1:本实施例提供的一种宽输入范围的时间放大器,如图1所示,包括时间放大延迟线、时间补偿延迟线以及脉冲合并电路,时间放大延迟线的一个输入端连接有输入时间信号stop,时间放大延迟线和时间补偿延迟线的输入端均连接有输入时间信号start,时间放大延迟线和时间补偿延迟线的输出端分别与脉冲合并电路的两个输入端相连接,脉冲合并电路在感应输入时间信号stop和输入时间信号start的延迟差距之后,输出对应脉冲宽度的信号ta_out,从而对输入时间进行放大。

16.如图2所示,时间放大延迟线包括1个反相器inv和n个可变延迟单元,分别为可变延迟单元d1_1~可变延迟单元d1_n,其中n设置为不小于2的偶数,除可变延迟单元d1_1外每一可变延迟单元的输入端in均与上一相邻序号的可变延迟单元的输出端out相连;反相器inv的输入端和每个可变延迟单元的en端均分别与输入时间信号stop连接,反相器inv的输出端分别连接于每个可变延迟单元的en_n端;输入时间信号start连接于可变延迟单元d1_1的输入端in,可变延迟单元d1_n的输出端out作为整个时间放大延迟线的输出端。

17.如图2所示,时间补偿延迟线包括n个可变延迟单元,分别为可变延迟单元d2_1~可变延迟单元d2_n,n设置为等于时间放大延迟线中可变延迟单元的数量,除可变延迟单元d2_1外每一可变延迟单元的输入端in均与上一相邻序号的可变延迟单元的输出端out相连;可变延迟单元d2_1的输入端in与输入时间信号start连接,可变延迟单元d2_n的输出端out作为整个时间补偿延迟线的输出端;每个可变延迟单元的en端与电源连接,en_n端则接地。

18.如图2所示,脉冲合并电路设置为异或门电路,异或门电路的两个输入端作为脉冲合并电路的输入端,且分别与可变延迟单元d1_n的输出端out和可变延迟单元d2_n的输出端out连接;异或门电路的输出端作为脉冲合并电路的输出端。

19.如图3所示,可变延迟单元包括8个pmos管和8个nmos管,8个pmos管分别为pmos管pm1~pmos管pm8,8个nmos管分别为nmos管nm1~nmos管nm8;其中,可变延迟单元输入端in的输入信号分别接pmos管pm1、pmos管pm2、nmos管

nm1、nmos管nm2的栅极;pmos管pm1的源极与pmos管pm3的漏极相连接,pmos管pm1的漏极分别与nmos管nm1、pmos管pm2、nmos管nm2的漏极以及pmos管pm5、nmos管nm5、pmos管pm6、nmos管nm6的栅极相连接;pmos管pm2的源极与pmos管pm4的漏极相连接;pmos管pm3的栅极接地,源极接电源;pmos管pm4的栅极接可变延迟单元en端的输入信号,源极接电源;pmos管pm5的源极接pmos管pm7的漏极,漏极与nmos管nm5、pmos管pm6、nmos管nm6的漏极相连接,并作为可变延迟单元的输出端out;pmos管pm6的源极与pmos管pm8的漏极相连接;pmos管pm7的栅极接地,源极接电源;pmos管pm8的栅极接可变延迟单元en端的输入信号,源极接地;nmos管nm1的源极与nmos管nm3的漏极相连接;nmos管nm2的源极与nmos管nm4的漏极相连接;nmos管nm3的栅极接电源,源极接地;nmos管nm4的栅极接可变延迟单元en_n端的输入信号,源极接地;nmos管nm5的源极与nmos管nm7的漏极相连接;nmos管nm6的源极与nmos管nm8的漏极相连接;nmos管nm7的栅极接电源,源极接地;nmos管nm8的栅极接可变延迟单元en_n端的输入信号,源极接地。

20.pmos管pm3与pmos管pm7的宽长比相同,pmos管pm1与pmos管pm5的宽长比相同,nmos管nm1与nmos管nm5的宽长比相同,nmos管nm3与nmos管nm7的宽长比相同;pmos管pm4与pmos管pm8的宽长比相同,且为pmos管pm3宽长比的k倍;pmos管pm2与pmos管pm6的宽长比相同,且为pmos管pm1宽长比的k倍;nmos管nm2与nmos管nm6的宽长比相同,且为nmos管nm1宽长比的k倍;nmos管nm4与nmos管nm8的宽长比相同,且为nmos管nm3宽长比的k倍;k即为时间放大器的增益。

21.本实施例的一种宽输入范围时间放大器,在实现4倍时间放大时输入与输出波形仿真结果如图4所示,在输入时间信号start与输入时间信号stop的时间差为100ps时,时间放大器增益k取4 ,宽输入范围时间放大器的输出信号ta_out脉冲宽度为400.347ps,实现了对输入信号的4倍放大。

22.实施例2:本实施例的一种宽输入时间放大器,在输入时间范围变化时,时间增益的仿真结果如图5所示,时间放大器增益k取4,可变延迟单元级数n(即个数)设置为64时,针对50ps-2ns的输入时间范围,均能实现4倍时间放大,且增益误差小于0.427%。

23.通过时间放大延迟线、时间补偿延迟线以及脉冲合并电路的设置,基于可变延迟控制,采用时间放大感应与时间做差方案,能够实现对输入时间差的感应与放大;同时通过调整可变延迟单元级数n,能够改变时间输入范围,通过改变可变延迟单元中mos管的宽长比k,能够改变时间放大器的增益,从而在保证紧凑面积无需额外校准电路的前提下,具有更宽的输入范围与较更好的线性度,同时增益也可以方便的进行调整。

24.除上述实施例外,本发明还可以有其他实施方式。凡采用等同替换或等效变换形成的技术方案,均落在本发明要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1