具有分三层的单元设计的静态随机存取存储器器件的制作方法

本公开一般涉及静态随机存取存储器(sram)器件。具体地,本公开提出了具有分三层的sram单元设计的sram器件。sram单元包括三层结构的堆叠,以及分布在该三层结构之间的存储晶体管和存取晶体管。

背景技术:

1、sram器件是一种类型的随机存取存储器(ram)器件,其使用锁存电路系统(触发器)将每个位存储在sram器件的sram单元(存储器单元)中。sram器件是易失性存储器器件,即当sram器件断电时,所存储的数据丢失。

2、术语“静态”将sram器件与必须定期刷新的动态随机存取存储器(dram)器件区分开来。sram器件比dram器件更快且更昂贵。sram单元通常用于中央处理单元(cpu)高速缓存,因为它们由与逻辑电路系统相同的基本组件(即晶体管)构建,因此它们可以与逻辑电路系统集成在一起。dram器件通常用于计算机的主存储器。

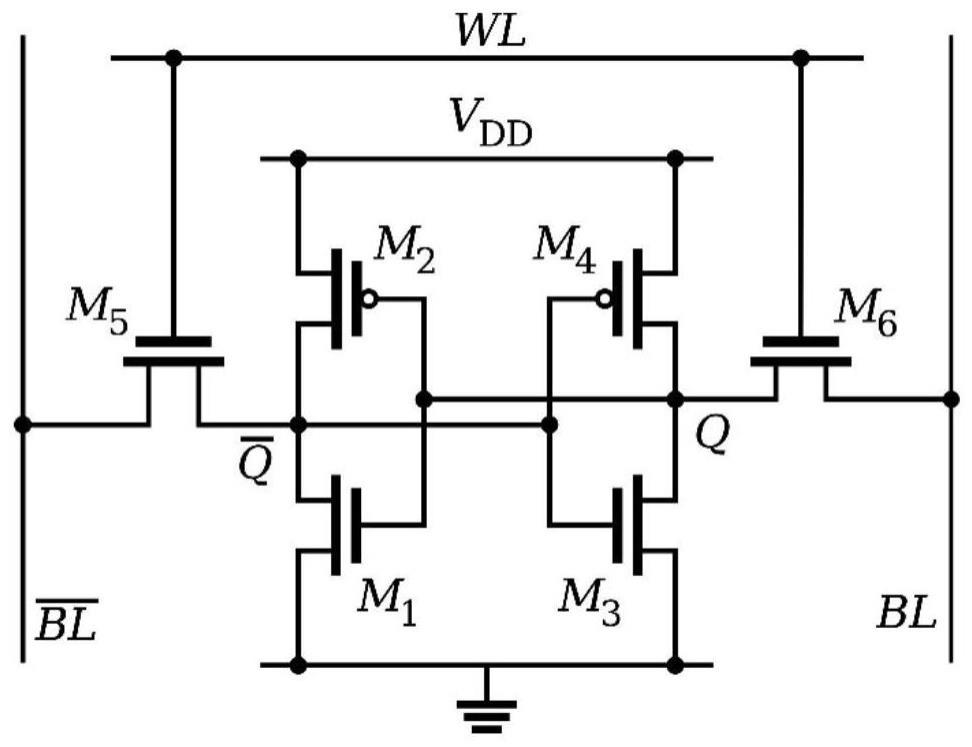

3、归因于实现sram单元所需的晶体管数量(四个存储晶体管和两个存取晶体管),sram器件的存储密度低于dram器件,并且其价格高于dram器件。此外,当数据被主动读取或写入时,sram器件的功耗很高。然而,sram器件比dram器件更快且更易于管理。sram器件可以集成为微控制器中的ram或高速缓存存储器,或者作为功能强大的微处理器(诸如x86系列和其他许多微处理器)中的主高速缓存来存储寄存器和某些微处理器中使用的状态机的各部分。sram器件的典型sram单元设计如图1所示。如上所述,sram单元由六个晶体管组成,例如金属氧化物半导体场效应晶体管(mosfet)。每个位由sram器件存储在一个sram单元中,并且特别是在包括四个存储晶体管m1、m2、m3和m4的存储单元中。如可在图1中看到的,这四个存储晶体管m1、m2、m3和m4形成两个交叉耦合的反相器。该晶体管配置具有两个稳定状态,其可被用于表示所存储的位的“0”和“1”。两个附加的存取晶体管m5和m6用于在读和写操作期间控制对存储单元的存取。

4、因为sram器件的每一sram单元中有六个晶体管,所以sram单元的占地面积相对较大。

技术实现思路

1、鉴于上述,本公开的目的是降低sram单元的占地面积。降低sram单元的占地面积将允许整体上减小sram器件的尺寸,并从而进一步增加微处理器芯片中的sram区域的密度。相应地,本公开的另一目的是提供更小的sram器件,并减小用于相同功能性的芯片的尺寸。然而,sram单元的占地面积的降低不应对经典逻辑电路系统设计产生任何影响。这些以及其他目的是通过在独立权利要求中提供的解决方案来达成的。附加实现在从属权利要求中限定。

2、本公开的解决方案基于在三层结构的堆叠中堆叠sram单元的六个晶体管,并且基于使用不同类型的半导体材料来制造该三层结构中的至少两层。

3、本公开的第一方面提供了一种sram器件,包括:用于存储一个位的存储单元,该存储单元包括四个存储晶体管;两个存取晶体管,被配置成控制对存储单元的存取以存储或读取位;以及包括三层结构的层结构堆叠;其中四个存储晶体管中的两个存储晶体管形成在堆叠的第一层结构中;其中四个存储晶体管中的两个其他存储晶体管形成在堆叠的与第一层结构相邻的第二层结构中;其中两个存取晶体管形成在该堆叠的与第二层结构相邻的第三层结构中。其中三层结构中的每一层结构包括半导体材料,并且层结构中的晶体管基于半导体材料;以及其中三层结构中的至少两层包括不同类型的半导体材料。

4、通过将六个晶体管分布在三层结构的堆叠上,并且通过在三层结构中的至少两层中使用不同类型的半导体材料,可以显著降低sram单元的占地面积。此外,降低sram单元的占地面积允许整体上减小sram器件的尺寸。本公开提出的sram单元的占地面积的降低有利地对经典逻辑电路系统设计没有影响。该堆叠的每一层结构可以基于单个半导体材料,其是特定类型的半导体材料。在这种情况下,三层结构中的一个层结构基于与三层结构中的至少一个其他层结构不同的半导体材料。层结构中的一些或每一者还可以基于一个以上的半导体材料,其可以是相同类型的或可以是不同类型的半导体材料。在这种情况下,三层结构中的一个层结构基于与其他层结构中的至少一者不同类型的半导体材料。例如,如果每一层结构基于两种半导体材料,则一个层结构可以包括与其他两个层结构中的至少一者不同的两种半导体材料。

5、在sram器件的一实现中,半导体材料的类型包括:硅基半导体材料,或二维2d半导体材料,或半导体氧化物材料。

6、该实现将不同类型的半导体材料区分开,如可被用在第一方面的sram器件的三层结构中的半导体材料。三层结构中的至少两层可包括这些特定类型中

7、的不同类型的半导体材料。值得注意的是,在一种类型的半导体材料中,也可5存在差异。例如,掺杂浓度或导电类型可以不同,或者某些材料浓度或比率可

8、以不同。然而,这不足以在本公开中表示不同类型的半导体材料。本公开中的不同类型的半导体意味着不同的材料系统。

9、例如,在本公开中,硅、硅锗和氮化硅将属于相同类型的半导体材料。同

10、样,例如,二硫化钼(mos2)、二硒化钨(wse2)和二硫化铪(hfs2)将属于0相同类型的2d半导体材料。同样,例如,氧化铟镓锌(igzo)、氧化铟锡(ito)和氧化铟锌(izo)将属于相同类型的半导体氧化物材料。

11、在sram器件的一实现中,第一层结构和第二层结构各自包括硅基半导体材料;并且第三层结构包括2d半导体材料和/或半导体氧化物材料。

12、换言之,第一层结构和第二层结构包括相同类型的半导体材料,而第三层5结构包括不同类型的半导体材料。第一和第二层结构不包括2d半导体材料和/

13、或半导体氧化物材料,并且第三层结构不包括硅基半导体材料。

14、在sram器件的一实现中,关于该堆叠的层结构的堆叠方向:第二层结构被形成在第一层结构上方,并且第三层结构被形成在第一层结构和第二层结构上方。

15、0例如,第一层结构可以形成在基板之上或上方,且第二层结构和第三层结

16、构可以在第一层结构之上或上方。值得注意的是,在本公开中,“形成在……

17、之上”是指直接形成在其上,而“形成在……上方”是指通过在它们之间设置的一个或多个其他层间接地形成在其上面。

18、在sram器件的一实现中,第一层结构和第二层结构各自包括2d半导体5材料和/或半导体氧化物材料;并且第三层结构包括硅基半导体材料。

19、换言之,同样地,第一层结构和第二层结构包括相同类型的半导体材料,而第三层结构包括不同类型的半导体材料。第一和第二层结构不包括硅基半导体材料,而第三层结构不包括2d半导体材料和/或半导体氧化物材料。

20、在sram器件的一实现中,关于该堆叠的层结构的堆叠方向:第二层结构0被形成在第三层结构上方,并且第一层结构被形成在第三层结构和第二层结构

21、上方。

22、例如,第三层结构可被形成在基板之上或上方,且第二层结构和第一层结构可被形成在第三层结构之上或上方。

23、在sram器件的一实现中,第一层结构是第一导电类型的经掺杂层结构,而第二层结构是第二导电类型的经掺杂层结构。

24、值得注意的是,第一和第二层结构由此可以是相同类型的半导体材料,或者可以是不同类型的半导体材料。

25、在sram器件的一实现中,第一存储晶体管和第二存储晶体管构成第一互补场效应晶体管cfet;和/或第三存储晶体管和第四存储晶体管构成第二cfet。

26、这允许进一步减小sram单元的尺寸,并从而整体上减小sram器件的尺寸。

27、在sram器件的一实现中,第一cfet和/或第二cfet是集成硅基纳米片晶体管。

28、在sram器件的一实现中,sram器件还包括第一垂直元件和/或第二垂直元件,第一垂直元件将第一层结构中的两个存储晶体管中的第一存储晶体管的栅极电连接到第二层结构中的两个其他存储晶体管中的第二存储晶体管的栅极;第二垂直元件将第一层结构中的两个存储晶体管中的第三存储晶体管的栅极电连接到第二层结构中的两个其他存储晶体管中的第四存储晶体管的栅极。

29、在sram器件的一实现中,sram器件还包括:第三垂直元件和/或第四垂直元件,第三垂直元件电连接第一存储晶体管的源极/漏极、第二存储晶体管的源极/漏极以及两个存取晶体管中的第一存取晶体管的源极/漏极;第四垂直元件电连接第三存储晶体管的源极/漏极、第四存储晶体管的源极/漏极以及两个存取晶体管中的第二存取晶体管的源极/漏极。

30、在sram器件的一实现中,第一垂直元件被电连接到第四垂直元件;和/或第二垂直元件被电连接到第三垂直元件。

31、上述实现的垂直元件使得能够连接sram单元的不同晶体管,使得sram单元可被形成在三层结构中。通过使用垂直元件,所需的布线大大减少,这从而有助于sram单元的小占地面积。同时,经降低的占地面积对sram单元的电路设计没有影响。

32、在sram器件的一实现中,第一存储晶体管的源极/漏极和第三存储晶体管的漏极/源极被连接到接地线;而第二存储晶体管的源极/漏极和第四存储晶体管的漏极/源极被连接到供电电压线。

33、在sram器件的一实现中,sram器件还包括被布置在堆叠上方并被电连接到两个存取晶体管的栅极的字线;或被布置在第二层结构和第三层结构之间并被电连接到两个存取晶体管的栅极的字线;并且sram器件还包括:被布置在第三层结构中并被连接到第一存取晶体管的源极/漏极的位线,以及被布置在第三层结构中并被连接到第二存取晶体管的源极/漏极的互补位线。

34、接地线、供电电压线、位线、互补位线和字线的布置支持sram单元的占地面积的降低。

35、本公开的第二方面提供了一种用于制造静态随机存取存储器sram器件的方法,该sram器件包括包括三层结构的层结构的堆叠,该方法包括:形成该堆叠的第一层结构,其中sram器件的存储单元的两个存储晶体管被形成在第一层结构中;形成该堆叠的与第一层结构相邻的第二层结构,其中存储单元的两个其他存储晶体管被形成在第二层结构中;形成该堆叠的与第二层结构相邻的第三层结构,其中两个存取晶体管被形成在第三层结构中,两个存取晶体管被配置成控制对存储单元的存取,以用于向存储单元存储位或从存储单元读取位;以及其中三层结构中的每一层结构包括半导体材料,并且层结构中的晶体管基于半导体材料,并且其中三层结构中的至少两层包括不同类型的半导体材料。

36、第二方面的方法实现与第一方面的器件相同的优点,并且可通过如上所述的用于第一方面的器件的相应实现来扩展。

37、总之,本公开提出了一种sram器件,其中一个或多个sram单元的占地面积显著降低。sram单元的设计可以达成几个优点。例如,接地线、供电电压线、位线和字线可以按大大减少所需布线的方式来组织。这也可以降低rc延迟。此外,可以在不改变sram单元的占地面积的情况下调整存取晶体管的尺寸。例如,存取晶体管中的电流可以被选择成不同于存储晶体管中的电流。不同类型的半导体材料,特别是至少一层结构中的2d材料和/或半导体氧化物材料与至少一个层结构中的硅基材料相结合,允许降低sram单元的占地面积,而不会对经典逻辑电路系统设计产生任何影响。事实上,添加到硅基半导体材料中的其他半导体材料可以在后端(beol)加工中带来额外的功能。

- 还没有人留言评论。精彩留言会获得点赞!