一种基于步进LDO校正TDC延迟步进的方法及装置与流程

本发明涉及集成电路,尤其涉及一种基于步进ldo校正tdc延迟步进的方法及装置。

背景技术:

1、在锁相环设计中,特别是数字锁相环设计中,会用到时间数字转换器(tdc,timeto digital converter)。

2、公开号为cn110212912b的发明专利公开了一种具有高精度时间数字转换器的倍数延迟锁相环,包含时间数字转换器处理模块、数模转换器、压控振荡器、分频器、数字控制电路和数据选择器,时间数字转换器处理模块设有依次相连的粗调时间数字转换器、数字时间转换器、减法器和脉冲缩小型时间数字转换器。本发明将高精度时间数字转换器模块应用于倍数延迟锁相环中,通过采样的方式,提高时间数字转换器的精度来改善量化噪声;使用脉冲缩小型时间数字转换器可省略时间放大器的使用以及上升和下降沿的撷取,直接将相位差输入至脉冲缩小型时间数字转换器进行第二次采样,不需要额外使用时间放大器将相位差放大,改善时间数字转换模块的线性度以及其输入范围。

3、公开号为cn110069008b的发明专利公开了一种时间数字转换器系统及包含该系统的倍数延迟锁相环,该系统包括:第一级时间数字转换器、第一级数字时间转换器、第一级时间放大器、第二级时间数字转换器、第二级数字时间转换器、第二级时间放大器、第三级逐次逼近寄存器型的模拟数字转换器及数字模拟转换器。本发明所提供的时间数字转换器系统及具有降低带内量化噪声的倍数延迟锁相环,使用类似于delta sigma的联级算法,有效提高应用于倍数延迟锁相环中的时间数字转换器精度,从而降低量化噪声的大小,并改善倍数延迟锁相环杂散的产生。

4、公开号为cn105897259b的发明专利公开了一种具有频控振荡器(42)、反馈路径、时间数字转换器(10)和存储器的锁相环。频控振荡器(42)包括用于改变频控振荡器(42)的输出(106)的频率以跟踪参考频率(101)的第一控制输入(135,136)和用于调制输出信号(106)以产生啁啾的第二控制输入(139)。反馈路径配置为向时间数字转换器(10)提供输入信号(107),并且包括可操作为从输出信号(106)中移除由第二控制输入(139)得到的频率调制的调制消除模块(14)。存储器存储第二控制输入值,每一个第二控制输入值对应于期望的啁啾频率并补偿频控振荡器对第二控制输入(139)的响应的非线性。锁相环可操作在啁啾模式中,在啁啾模式中,通过基于存储器中存储的第二控制输入值,确定与期望啁啾频率相对应的第二控制输入(139)的值,来产生第二控制输入(139),并且在啁啾模式中,锁相环配置为基于反馈路径确定第一控制输入(135,136)。

5、由于tdc的步进精度(tstep)影响了环路收到的相位差,tdc的分辨率/步进精度直接决定锁相环的最小分辨精度,影响环路锁定和性能。在采用单延迟单元的tdc锁相环路中,延迟大小的绝对值随制造工艺偏差可以达到典型值的±50%,这种偏差可能造成数字锁相环不锁定或者锁定以后的性能变差。

技术实现思路

1、为了解决上述问题,本发明提出一种基于步进ldo校正tdc延迟步进的方法及装置,数字锁相环环路开始之前,提前把tdc的延迟校正到设计值附近5%以内,保证了锁相环的收敛性和性能稳定。

2、本发明采用的技术方案如下:

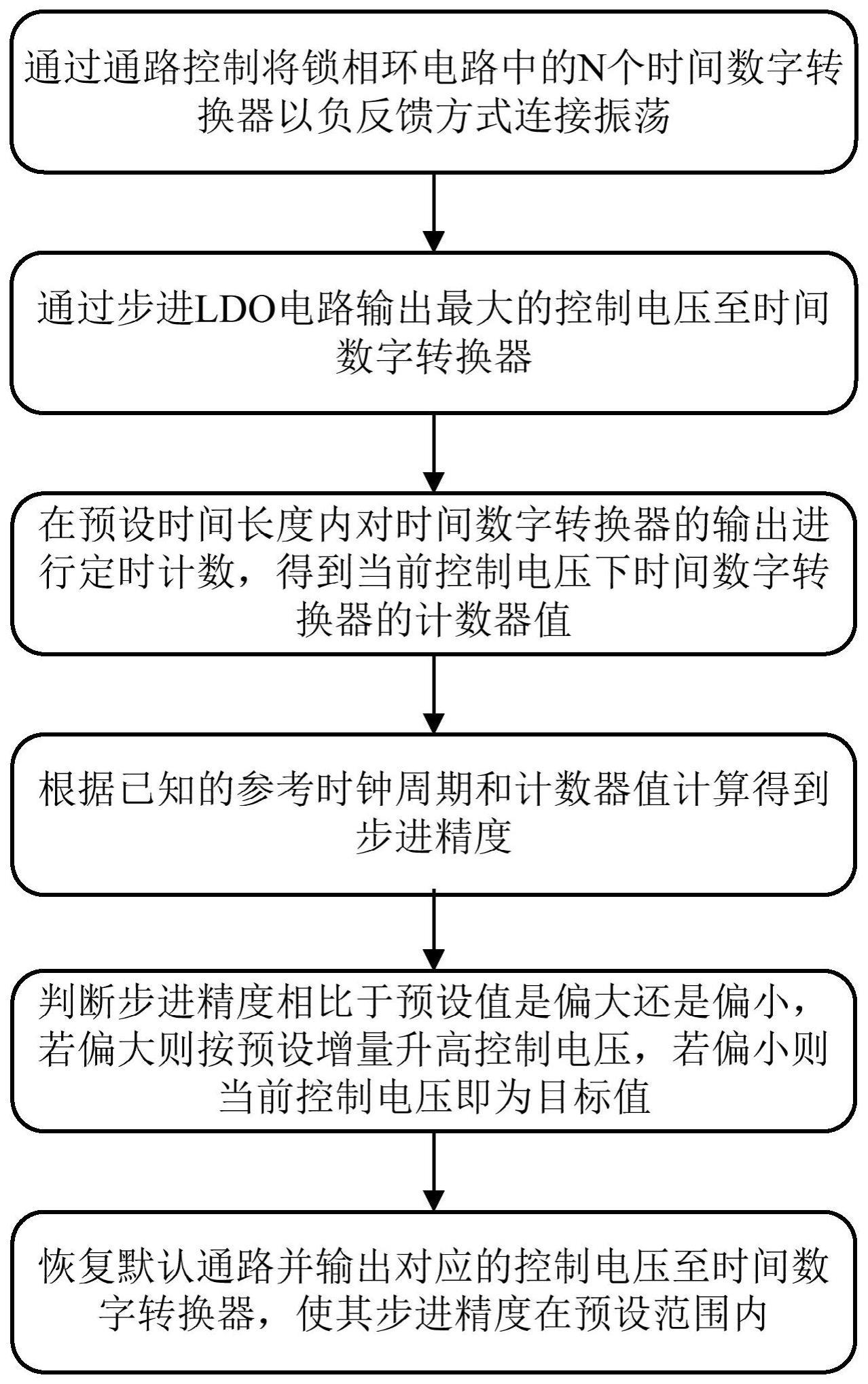

3、一种基于步进ldo校正tdc延迟步进的方法,包括以下步骤:

4、s1.通过通路控制将锁相环电路中的n个tdc即时间数字转换器以负反馈方式连接振荡,则所述时间数字转换器的延迟将在应用范围内随电压或电流单调变化;

5、s2.通过步进ldo电路输出最大的控制电压vcont至所述时间数字转换器;

6、s3.将所述锁相环电路中已知频率的参考时钟作为定时器,在预设时间长度内对所述时间数字转换器的输出进行定时计数,得到当前控制电压vcont下所述时间数字转换器的计数器值k;

7、s4.通过数据处理和计算电路根据已知的参考时钟周期tref和所述计数器值k计算得到所述时间数字转换器的步进精度tstep;

8、s5.通过控制信号生成电路判断所述步进精度tstep相比于预设值是偏大还是偏小,若偏大,则通过所述步进ldo电路按预设增量升高所述控制电压vcont,并跳转至步骤s4;若偏小,则当前控制电压vcont即为目标值;

9、s6.通过通路控制将所述时间数字转换器之间的负反馈连接断开,恢复默认通路,并通过所述步进ldo电路输出对应的控制电压vcont至所述时间数字转换器,使其步进精度tstep在预设范围内。

10、进一步地,所述步进ldo电路包括参考电压产生电路和低压差线性稳压器,所述参考电压产生电路的信号输入端电连接所述控制信号生成电路的信号输出端,所述参考电压产生电路的信号输出端电连接所述低压差线性稳压器的信号输入端,所述低压差线性稳压器的信号输出端电连接所述数字时间转换器的信号输入端。

11、进一步地,步骤s5中,若通过控制信号生成电路判断出所述步进精度tstep相比于预设值偏大,则通过所述参考电压产生电路控制所述低压差线性稳压器按预设增量升高所述控制电压vcont,并跳转至步骤s4;否则,说明当前控制电压vcont即为目标值,保存所述参考电压产生电路的控制值。

12、进一步地,步骤s6中,通过通路控制将所述数字时间转换器之间的负反馈连接断开,恢复默认通路后,利用所述参考电压产生电路的控制值控制所述低压差线性稳压器输出对应的控制电压vcont至所述数字时间转换器,使其步进精度tstep在预设范围内。

13、进一步地,步骤s4中,所述步进精度tstep的计算方法包括:

14、tstep=m*tref/(k*2*n)

15、其中,m为计数期间的参考时钟周期个数。

16、一种基于步进ldo校正tdc延迟步进的装置,包括n个时间数字转换器、定时器、数据处理和计算模块、控制信号生成电路和步进ldo电路,所述时间数字转换器、定时器、数据处理和计算模块、控制信号生成电路和步进ldo电路首尾连接;

17、所述n个tdc即时间数字转换器以负反馈方式连接振荡,其延迟将在应用范围内随电压或电流单调变化;

18、所述步进ldo电路被配置为输出最大的控制电压vcont至所述时间数字转换器,并能够按预设增量升高所述控制电压vcont;

19、所述定时器被配置为锁相环电路中已知频率的的参考时钟,并在预设时间长度内对所述时间数字转换器的输出进行定时计数,得到当前控制电压vcont下所述时间数字转换器的计数器值k;

20、所述数据处理和计算电路被配置为根据已知的参考时钟周期tref和所述计数器值k计算得到所述时间数字转换器的步进精度tstep;

21、所述控制信号生成电路被配置为判断所述步进精度tstep相比于预设值是偏大还是偏小,若偏大,则通过所述步进ldo电路按预设增量升高所述控制电压vcont;若偏小,则当前控制电压vcont即为目标值。

22、进一步地,所述步进ldo电路包括参考电压产生电路和低压差线性稳压器,所述参考电压产生电路的信号输入端电连接所述控制信号生成电路的信号输出端,所述参考电压产生电路的信号输出端电连接所述低压差线性稳压器的信号输入端,所述低压差线性稳压器的信号输出端电连接所述数字时间转换器的信号输入端。

23、进一步地,步骤s5中,若通过控制信号生成电路判断出所述步进精度tstep相比于预设值偏大,则通过所述参考电压产生电路控制所述低压差线性稳压器按预设增量升高所述控制电压vcont,并跳转至步骤s4;否则,说明当前控制电压vcont即为目标值,保存所述参考电压产生电路的控制值。

24、进一步地,步骤s6中,通过通路控制将所述数字时间转换器之间的负反馈连接断开,恢复默认通路后,利用所述参考电压产生电路的控制值控制所述低压差线性稳压器输出对应的控制电压vcont至所述数字时间转换器,使其步进精度tstep在预设范围内。

25、进一步地,步骤s4中,所述步进精度tstep的计算方法包括:

26、tstep=m*tref/(k*2*n)

27、其中,m为计数期间的参考时钟周期个数。

28、本发明的有益效果在于:

29、本发明可以在锁相环环路工作之前,精确调整tdc的步进精度tstep,把tstep值的工艺波动的影响tstep_max降低到预设范围内。以目前的40nm cmos工艺来,看这个误差可以从±50%降低到5%。

- 还没有人留言评论。精彩留言会获得点赞!