一种单通道L波段变频装置的制作方法

一种单通道l波段变频装置

技术领域

1.本实用新型涉及l波段变频技术领域,尤其是一种单通道l波段变频装置。

背景技术:

2.l波段是指频率在1-2ghz的无线电波波段,其可被用于dab、卫星导航系统等。随着小型化、集成化的不断发展,l波段变频装置也趋向于小型化发展。但是,现有技术中的变频设备的体型依然较大,其无法实现轻量便携的功能。例如专利公开号为“cn216649624u”、名称为“一种l波段变频组件模块”的中国实用新型,其包括电源单元、接收通道、发射通道和频综单元,电源单元分别与接收通道、发射通道和频综单元连接,接收通道输入端与输入接口连接,接收通道输出端与信号处理模块连接,接收通道以将射频信号下变频至中频信号,信号处理模块输出端与输出接口连接,输出接口与发射通道连接,发射通道以对中频信号上变频至射频信号发送;该技术的结构较为复杂。

3.因此,急需要提出一种结构简单、小型化的单通道l波段变频装置。

技术实现要素:

4.针对上述问题,本实用新型的目的在于提供一种单通道l波段变频装置,本实用新型采用的技术方案如下:

5.一种单通道l波段变频装置,其包括stc系列的微控制器u33,依次连接后并与微控制器u33连接的第一锁相环电路、第一数字衰减器、滤波电路和时钟分频器,与微控制器u33连接的第二锁相环电路,分别与微控制器u33连接的时钟电路、本地时钟电路和射频通道选择电路,与第一数字衰减器连接的晶振u31,与第一锁相环电路连接的第七数字衰减器u30,与第七数字衰减器u30 连接的射频连接器u37,以及与微控制器u33、第一锁相环电路、第一数字衰减器、时钟分频器、第二锁相环电路、时钟电路、本地时钟电路和射频通道选择电路连接的供电电路;所述第二锁相环电路与时钟电路、本地时钟电路和射频通道选择电路连接;所述滤波电路与时钟电路、本地时钟电路、时钟分频器和第二锁相环电路连接。

6.进一步地,所述射频通道选择电路包括依次连接的第一射频接头u40、第一低通滤波器u35、第二数字衰减器u1、第三数字衰减器u3、第四数字衰减器 u4、第五数字衰减器u57和第六数字衰减器u5,以及连接在第四数字衰减器 u4与第六数字衰减器u5之间的增益放大器u6。

7.更进一步地,所述第一低通滤波器u35的型号为lfcg-3500+;所述第二数字衰减器u1和第五数字衰减器u57的型号为pe42422;所述第三数字衰减器 u3的型号为pe4312;第四数字衰减器u4和第六数字衰减器u5的型号为 pe42430;所述增益放大器u6的型号为qpa4563a。

8.优选地,所述第一锁相环电路和第二锁相环电路采用型号为adf4360-9的锁相环芯片;所述第一数字衰减器的型号为pe42422;所述时钟分频器的型号为 mc12080。

9.进一步地,所述滤波电路包括串联后一端与第一数字衰减器的rfc引脚连接、且另

一端接地的电容c57、电感l9和电容c120,一端连接在电容c57与电感l9之间的电容c93,与电容c93的另一端连接第一滤波电路,以及与第一滤波电路连接的第二滤波电路和第三滤波电路;所述第一滤波电路、第二滤波电路和第三滤波电路的结构相同,且第一滤波电路包括一端与电容c93的另一端连接、且另一端接地的电容c139,串联后一端连接在电容c93与电容c139之间、且另一端接地的电感l11和电容c139,串联后一端连接在电容c93与电容c139 之间、且另一端接地的电感l14和电容c140,以及一端连接在电感l11与电容 c139之间、且另一端连接在电感l14与电容c140之间的电阻r58;所述第二滤波电路与电感l11和电容c139连接;所述第三滤波电路与电感l14和电容c140 连接;所述时钟分频器与第三滤波电路连接。

10.进一步地,所述时钟电路包括与滤波电路和微控制器u33连接、且型号为 ltc6948-3的时钟发生频率混频器u7,与时钟发生频率混频器u7连接、且型号为qpa9127的射频放大器u43,与射频放大器u43连接、且型号为mm1-0312hsm 的混频器u10,与混频器u10连接、且型号为qpa9127的射频放大器u8和射频放大器u9,以及与射频放大器u8连接、且型号为rf_conn的射频连接器 j9。

11.进一步地,所述本地时钟电路包括与滤波电路和微控制器u33连接、且型号为ltc6948-2的时钟发生频率混频器u13,与时钟发生频率混频器u13连接、且型号为qpa9127的射频放大器u46,与射频放大器u46连接、且型号为 hmc213bms8e的双平衡混频器u12,串联后输入端与双平衡混频器u12连接的低通滤波器f1和低通滤波器f2,与低通滤波器f2的输出端连接的放大器 u32,以及与放大器u32连接、且型号为rf_conn的射频连接器j7。

12.进一步地,所述单通道l波段变频装置,还包括与微控制器u33连接、且型号为max3232ipwr的通信芯片u23,以及与通信芯片u23连接的通信接口 j500。

13.与现有技术相比,本实用新型具有以下有益效果:

14.(1)本实用新型巧妙地设置第一锁相环电路、第一数字衰减器、滤波电路时钟分频器、晶振u31、第二锁相环电路、第七数字衰减器u30、时钟电路、本地时钟电路和射频通道选择电路,晶振u31作为锁相环的时钟源提供本地时钟参考,锁相环芯片根据其外围的环路滤波器硬件参数结合主控芯片通过spi 总线下发的寄存器控制指令生成内部高频率压控时钟之后分频滤波输出高稳定高相噪的指定频率范围的本地振荡信号供混频器使用。

15.(2)本实用新型的时钟电路通过设置时钟发生频率混频器u7、射频放大器 u43、混频器u10、射频放大器u8、射频放大器u9和射频连接器j9。其中,时钟发生频率混频器u7产生的本振信号经过射频放大器u43进行功率放大,并放大后的信号达到混频器u10的最佳工作条件,从而混频输出高信噪比的第一中频信号,再送给后端的元器件根据实际工作条件的需求按需进行功率放大。

16.(3)本实用新型的本地时钟电路通过设置时钟发生频率混频器u13、射频放大器u46、双平衡混频器u12、低通滤波器f1、低通滤波器f2、放大器u32 和射频连接器j7。其中,时钟发生频率混频器u13产生的第二级本振时钟信号经过射频放大器u46放大,放大后的信号达到双平衡混频器u12的最佳工作条件,双平衡混频器u12混频得到的第二级中频信号经过低通滤波器f1、低通滤波器f2过滤掉漏过来的本振和射频信号的高次谐波之后再送入放大器u32,避免产生不必要的杂散信号。

17.(4)本实用新型通过设置由第一射频接头u40、第一低通滤波器u35、第二数字衰减

器u1、第三数字衰减器u3、第四数字衰减器u4、第五数字衰减器 u57、第六数字衰减器u5和增益放大器u6组成的射频通道选择电路,其作用是根据信号所处频段可能产生的高次谐波进行针对性的滤波和衰减,避免信号失真。

18.综上所述,本实用新型简化了结构构造,并且实现集成化、小型化,其具有结构简单、功能齐全、集成小型化等优点,在l波段变频技术领域具有很高的实用价值和推广价值。

附图说明

19.为了更清楚地说明本实用新型实施例的技术方案,下面将对实施例中所需使用的附图作简单介绍,应当理解,以下附图仅示出了本实用新型的某些实施例,因此不应被看作是对保护范围的限定,对于本领域技术人员来说,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

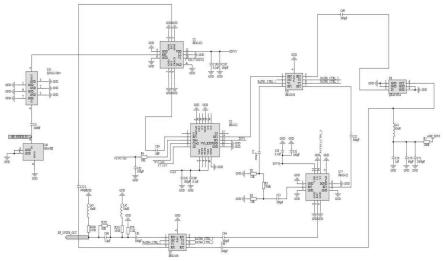

20.图1为本实用新型中微控制器u33的原理图。

21.图2为本实用新型中串口通信电路原理图。

22.图3为本实用新型中第一锁相环电路、第一数字衰减器和晶振u31的原理图。

23.图4为本实用新型中滤波电路、时钟分频器、第七数字衰减器u30的原理图。

24.图5为本实用新型中第二锁相环电路原理图。

25.图6为本实用新型中时钟电路原理图。

26.图7为本实用新型中时钟电路的第一输出电路原理图。

27.图8为本实用新型中时钟电路的第二输出电路原理图。

28.图9为本实用新型中本地时钟电路原理图。

29.图10为本实用新型中射频通道选择电路原理图。

具体实施方式

30.为使本技术的目的、技术方案和优点更为清楚,下面结合附图和实施例对本实用新型作进一步说明,本实用新型的实施方式包括但不限于下列实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本技术保护的范围。

31.实施例

32.如图1至图10所示,本实施例提供了一种单通道l波段变频装置。首先,需要说明的是,本实施例中所述的“第一”、“第二”等序号用语仅用于区分同类部件,不能理解成对保护范围的特定限定。另外,本实施例是基于结构的改进,并未对软件程序进行改进,其采用常规的程序片段组合便能实现,在此就不予赘述其具体内容。

33.在本实施例中,该单通道l波段变频装置,包括stc8a8k64s4a12_lqfp64 微控制器u33、第一锁相环电路、第一数字衰减器、滤波电路、时钟分频器、第二锁相环电路、时钟电路、本地时钟电路、射频通道选择电路、晶振u31、第七数字衰减器u30、射频连接器u37、串口通信电路和供电电路。其中,第二锁相环电路、时钟电路、串口通信电路、本地时钟电路和射频通道选择电路分别与微控制器u33连接。第一数字衰减器与晶振u31连接;第一锁相环电路与第七数字衰减器u30连接;第七数字衰减器u30与射频连接器u37连接。第二锁相环电路与时钟电路、本地时钟电路和射频通道选择电路连接。滤波电路与时钟电路、本地时钟电

路、时钟分频器和第二锁相环电路连接。其中,在本实施例中,串口通信电路包括与微控制器u33连接、且型号为max3232ipwr的通信芯片u23,以及与通信芯片u23连接的通信接口j500。另外,本实施例优选地:第一锁相环电路和第二锁相环电路采用型号为adf4360-9的锁相环芯片;所述第一数字衰减器的型号为pe42422;所述时钟分频器的型号为mc12080。

34.本实施例通过设置滤波电路,并对第一数字衰减器的输出进行过滤,其包括串联后一端与第一数字衰减器的rfc引脚连接、且另一端接地的电容c57、电感l9和电容c120,一端连接在电容c57与电感l9之间的电容c93,与电容 c93的另一端连接第一滤波电路,以及与第一滤波电路连接的第二滤波电路和第三滤波电路;所述第一滤波电路、第二滤波电路和第三滤波电路的结构相同,且第一滤波电路包括一端与电容c93的另一端连接、且另一端接地的电容c139,串联后一端连接在电容c93与电容c139之间、且另一端接地的电感l11和电容 c139,串联后一端连接在电容c93与电容c139之间、且另一端接地的电感l14 和电容c140,以及一端连接在电感l11与电容c139之间、且另一端连接在电感 l14与电容c140之间的电阻r58;所述第二滤波电路与电感l11和电容c139连接;所述第三滤波电路与电感l14和电容c140连接;所述时钟分频器与第三滤波电路连接。在本实施例中电容c57、电感l9、电容c120和电容c93构成一滤波电路,并且与第一滤波电路、第二滤波电路和第三滤波电路组成多阶滤波,保证信号输出更可靠。

35.在本实施例通过设置时钟电路,以获取频率为2800mhz~3100mhz,具体来说,该时钟电路包括与滤波电路和微控制器u33连接、且型号为ltc6948-3的时钟发生频率混频器u7,与时钟发生频率混频器u7连接、且型号为qpa9127 的射频放大器u43,与射频放大器u43连接、且型号为mm1-0312hsm的混频器u10,与混频器u10连接、且型号为qpa9127的射频放大器u8和射频放大器u9,以及与射频放大器u8连接、且型号为rf_conn的射频连接器j9。

36.在本实施例中,该本地时钟电路包括与滤波电路和微控制器u33连接、且型号为ltc6948-2的时钟发生频率混频器u13,与时钟发生频率混频器u13连接、且型号为qpa9127的射频放大器u46,与射频放大器u46连接、且型号为 hmc213bms8e的双平衡混频器u12,串联后输入端与双平衡混频器u12连接的低通滤波器f1和低通滤波器f2,与低通滤波器f2的输出端连接的放大器 u32,以及与放大器u32连接、且型号为rf_conn的射频连接器j7。在本实施例中,利用时钟发生频率混频器u13进行频率发生,在利用射频放大器u46 进行放大,并与双平衡混频器u12的输入进行平衡混频,在利用低通滤波器f1 和低通滤波器f2进行过滤,最后经过放大器u32放大后进行输出。

37.在本实施例中,通过设置射频通道选择电路,以实现分频段进行高次谐波过滤,确保各段原始信号尽可能纯净。具体来说,其包括依次连接的第一射频接头u40、lfcg-3500+第一低通滤波器u35、pe42422第二数字衰减器u1、 pe4312第三数字衰减器u3、pe42430第四数字衰减器u4、pe42422第五数字衰减器u57和pe42430第六数字衰减器u5,以及连接在第四数字衰减器u4与第六数字衰减器u5之间的qpa4563a增益放大器u6。

38.上述实施例仅为本实用新型的优选实施例,并非对本实用新型保护范围的限制,但凡采用本实用新型的设计原理,以及在此基础上进行非创造性劳动而作出的变化,均应属于本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1