结合内部连接的输出集成晶体管放大器器件封装的制作方法

本公开涉及晶体管器件,更具体而言,涉及晶体管放大器和相关器件封装。

背景技术:

1、在高频下操作时要求高功率处置能力的电路,诸如r频带(0.5-1ghz)、s频带(3ghz)、x频带(10ghz)、ku频带(12-18ghz)、k频带(18-27ghz)、ka频带(27-40ghz)和v频带(40-75ghz)变得更加普遍。特别地,现在对用于放大例如500mhz和更高频率(包括微波频率)的rf信号的射频(“rf”)晶体管放大器有很高的需求。这些rf晶体管放大器可能需要表现出高可靠性、高效率、良好的线性度和处置高输出功率电平。

2、一些晶体管放大器用硅或宽带隙半导体材料(诸如碳化硅(“sic”)和iii族氮化物材料)实现。如本文所使用的,术语“iii族氮化物”是指在氮和元素周期表的iii族元素(通常是铝(al)、镓(ga)和/或铟(in))之间形成的那些半导体化合物。该术语还指三元和四元化合物,诸如algan和alingan。这些化合物具有经验式,其中一摩尔氮与总共一摩尔iii族元素结合。

3、基于硅的晶体管放大器常常使用横向扩散金属氧化物半导体(“ldmos”)晶体管来实现。硅ldmos晶体管放大器可以表现出高水平的线性度,并且制造成本可以相对较低。基于iii族氮化物的晶体管放大器常常被实现为高电子迁移率晶体管(“hemt”)并且主要用在要求高功率和/或高频操作的应用中,其中ldmos晶体管放大器可以具有固有的性能限制。

4、晶体管放大器封装可以包括一个或多个放大级,每个放大级通常被实现为晶体管放大器芯片或“管芯”。为了增加输出功率和电流处置能力,晶体管放大器管芯通常以“单位单元”配置实现,其中大量个体“单位单元”晶体管电并联布置。晶体管放大器封装可以被实现为单个管芯,或者可以包括多个管芯。

5、晶体管放大器封装常常与匹配电路集成,诸如(1)阻抗匹配电路,其被设计为改善晶体管管芯和与连接到其的传输线之间的阻抗匹配(对于处于放大器的基本操作频率的信号),以及(2)谐波终端电路,其被设计为至少部分地终止器件操作期间可能生成的谐波(诸如二阶和三阶谐波)。(一个或多个)晶体管管芯以及阻抗匹配和谐波终端电路可以被封在封装中。电引线可以从封装延伸,用于将晶体管管芯电连接到外部电路元件(诸如输入和输出传输线以及偏置电压源)。

6、现代电信系统的设计可能需要以高效率和高线性度递送宽范围的输出功率电平。传统上,此类系统将包括平衡的晶体管放大器,该晶体管放大器被配置为以最大可用效率处置最高功率电平。因此,当系统以小于最大功率操作时(这可以包括操作循环的大部分),系统的整体效率会降低。

7、doherty放大器是一种类型的可以解决这个问题的晶体管放大器封装。通过使用两个放大器电路来适应不同的信号电平,doherty放大器可以适应具有高峰-均功率比的信号。以这种方式,放大器实现了高水平的线性度,同时在一定范围的信号电平上保持良好的功率效率。如本领域中已知的,doherty放大器电路包括第一和第二(或更多)功率组合的放大器。第一放大器被称为“主”或“载体”放大器,并且第二放大器被称为“峰化”放大器。两个放大器可以不同地偏置。例如,在一种常见的doherty放大器实施方式中,主放大器可以包括ab类或b类放大器,而峰化放大器可以是c类放大器。当以从饱和回退的功率电平操作时,doherty放大器可以比平衡放大器更高效地操作。输入到doherty放大器的rf信号被拆分成多个子分量(例如,使用正交耦合器),并且子分量被馈送到相应的放大器。然后放大器的输出被组合。主放大器被配置为首先开启(即,以较低的输入功率电平),因此只有主放大器将以较低的功率电平操作。当输入功率电平朝着饱和增加时,峰化放大器开启,并且输入rf信号在主放大器与峰化放大器之间分离。

8、图1是两路doherty晶体管放大器10的示意图。如图1中所示,doherty晶体管放大器10包括rf输入端11、输入拆分器13、主放大器14、峰化放大器15、输出组合器18以及rf输出端19。doherty晶体管放大器10可以可选地包括输入匹配网络和/或输出匹配网络(未示出)。

9、在一些实施例中,输入拆分器13可以改变提供给主放大器14和峰化放大器15的信号的相对相位。例如,在一些实施例中,提供给主放大器14的信号可以与提供给峰化放大器15的信号异相90度。类似地,在一些实施例中,输出组合器18可以在一些实施例中包括输出定相线并且被配置为调整主放大器14和/或峰化放大器15的输出的相位。

10、在图1中,doherty放大器10仅包括两个放大器,但是doherty放大器可以包括不同数量的(例如,n个)峰化放大器和主放大器。例如,图2是三路doherty放大器30的示意图。将理解的是,仅示出了3个放大器,但是放大器的数量可以更多。如图2中所示,三路doherty晶体管放大器30包括rf输入端31、第一输入拆分器13_1、第二输入拆分器13_2、主放大器14、第一峰化放大器15_1、第二峰化放大器15_2、第一输出组合器18_1、第二输出组合器18_2以及rf输出端39。主放大器14、第一峰化放大器15_1和第二峰化放大器15_2常常被实现为单独封装的晶体管器件。

11、rf输入端31可以耦合到第一输入拆分器13_1。第一输入拆分器13_1的第一输出可以耦合到主放大器14,并且第一输入拆分器13_1的第二输出可以耦合到第二输入拆分器13_2。与图1的doherty放大器10一样,第一输入拆分器13_1的输出可以在相位上分离90度。第二输入拆分器13_2的输出可以耦合到第一峰化放大器15_1和第二峰化放大器15_2。第一峰化放大器15_1和第二峰化放大器15_2的输入也可以彼此异相。

12、主放大器14、第一峰化放大器15_1和第二峰化放大器15_2的输出可以以分级方式组合。例如,第一峰化放大器15_1和第二峰化放大器15_2的输出可以耦合到第二输出组合器18_2。主放大器14的输出和第二输出组合器18_2的输出可以耦合到提供rf输出39的第一输出组合器18_1。第一输出组合器18_1和/或第二输出组合器18_2可以被配置为转换输入到组合器的信号中的一个或多个的相位。

13、图2还包括输入和输出匹配网络。例如,输入匹配电路32可以分别耦合到主放大器14、第一峰化放大器15_1和第二峰化放大器15_2中的每一个的输入端。输出匹配电路34可以分别耦合到主放大器14、第一峰化放大器15_1和第二峰化放大器15_2中的每一个的输出端。输入匹配电路32和/或输出匹配电路34可以被配置为对接收到的信号执行阻抗匹配和/或谐波终端。每个输入匹配电路32和每个输出匹配电路34可以被配置为接收偏置信号,该偏置信号被配置为偏置相应电路的元件。

14、为了改进3路doherty放大器30的性能,输入匹配电路32和/或输出匹配电路34中的每一个可能需要单独配置。即,第一输入匹配电路32的元件可以与第二输入匹配电路32的元件不同。类似地,第一输出匹配电路34的元件可以与第二输出匹配电路34的元件不同。输入匹配电路32和/或输出匹配电路34的配置可以取决于操作的频率范围和/或三路doherty放大器30所连接到的所提供的负载。而且,如上所述,输入匹配电路32和/或输出匹配电路34中的每一个可以耦合到单独的偏置信号。因此,配置3路doherty放大器30可以复杂并且缺乏灵活性,并且用于容纳一定数目的电路(包括拆分器、组合器、输入匹配电路、输出匹配电路和偏置布线)的空间可以是有限的。随着对具有更高集成度的更小器件的需求的增加,后一个挑战会成为问题。随着doherty组合中放大器数量的增加(例如,超过两个或三个放大器),与复杂性和封装尺寸相关的问题也增加。

技术实现思路

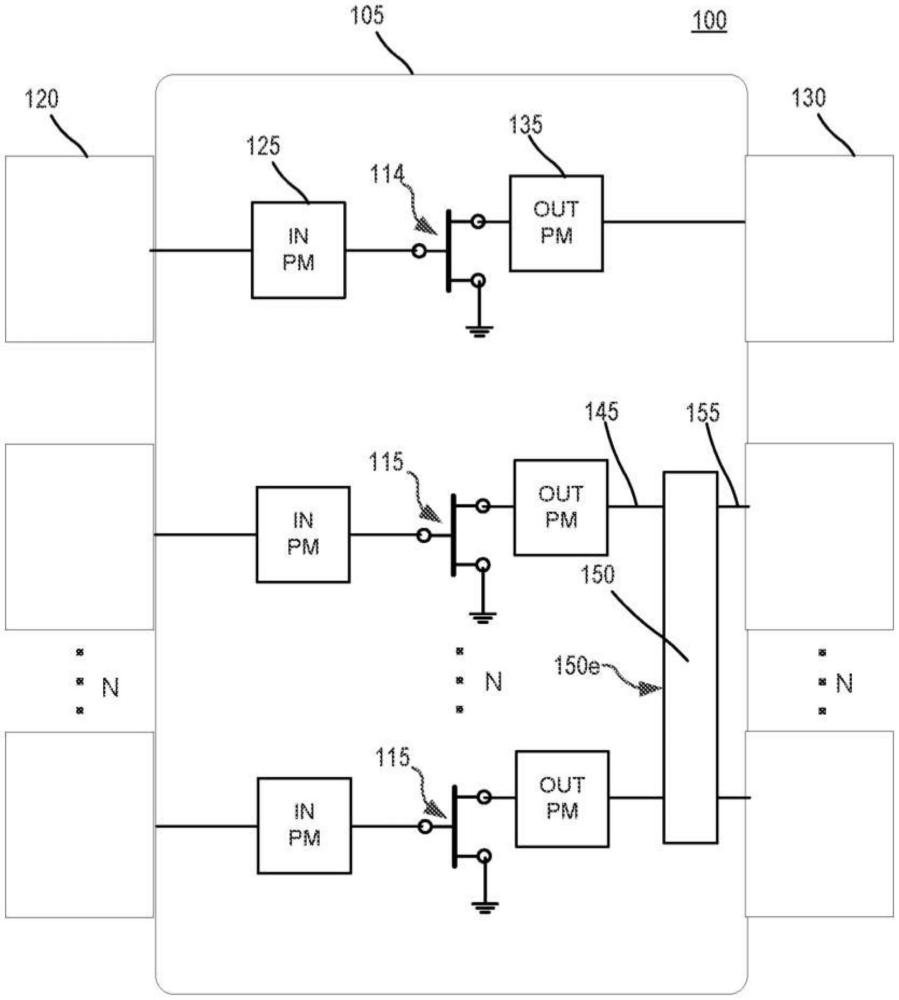

1、根据本发明的实施例,半导体器件封装包括多个输入引线和输出引线、具有分别耦合到多个输入引线的输入端的多个晶体管放大器管芯,以及被配置为组合从多个晶体管放大器管芯接收的输出信号并且将组合信号输出到输出引线的组合电路。

2、在一些实施例中,多个晶体管放大器管芯是第二晶体管放大器管芯,多个输入引线是多个第二输入引线,并且输出引线是第二输出引线,并且该半导体器件封装还包括第一输入引线、第一输出引线以及耦合在第一输入引线与第一输出引线之间的第一晶体管放大器管芯。

3、在一些实施例中,第一晶体管放大器管芯是doherty放大器的主放大器,并且多个第二晶体管放大器管芯是doherty放大器的峰化放大器。

4、在一些实施例中,组合电路位于半导体器件封装内。

5、在一些实施例中,其中输出引线是多个输出引线,并且其中组合电路还被配置为将组合信号输出到多个输出引线中的每一个输出引线。

6、在一些实施例中,半导体器件封装还包括分别位于多个晶体管放大器管芯中的一些晶体管放大器管芯与组合电路之间的多个输出预匹配电路。

7、在一些实施例中,组合电路包括印刷电路板(pcb)。

8、在一些实施例中,多个输出预匹配电路中的至少一个包括安装到组合电路的pcb的电容器。

9、在一些实施例中,多个输出预匹配电路中的至少一个包括通过键合线耦合到组合电路的pcb的电容器。

10、在一些实施例中,多个输入引线被配置为接收分别彼此异相的多个输入信号。

11、根据本发明的实施例,一种半导体器件封装包括:第一晶体管放大器管芯,耦合到半导体器件封装的第一输入引线;以及多个第二晶体管放大器管芯,分别耦合到半导体器件封装的多个第二输入引线。半导体器件封装的输出引线被配置为输出多个第二晶体管放大器管芯中的相应的第二晶体管放大器管芯的输出信号的组合。

12、在一些实施例中,半导体器件封装是doherty放大器封装,多个第二晶体管放大器管芯包括doherty放大器封装的第一峰化晶体管放大器和第二峰化晶体管放大器,并且第一晶体管放大器管芯包括doherty放大器封装的主放大器。

13、在一些实施例中,半导体器件封装还被配置为将第一晶体管放大器管芯的输出与多个第二晶体管放大器管芯的输出的组合进行组合。

14、在一些实施例中,半导体器件封装的多个输出引线被配置为输出输出信号的组合。

15、在一些实施例中,半导体器件封装还包括组合电路,该组合电路被配置为生成多个第二晶体管放大器管芯中的相应的第二晶体管放大器管芯的输出信号的组合。

16、在一些实施例中,组合电路包括印刷电路板(pcb)。

17、在一些实施例中,半导体器件封装还包括位于多个第二晶体管放大器管芯中的相应的第二晶体管放大器管芯与组合电路之间的输出预匹配电路。

18、根据本发明的实施例,一种半导体器件封装包括:多个晶体管放大器管芯,每个晶体管放大器管芯分别耦合到半导体器件封装的多个输入引线中的一个;以及组合电路,被配置为组合来自多个晶体管放大器管芯中的两个或更多个的输出信号以生成组合输出信号,并将该组合输出信号提供给半导体器件封装的至少一个输出引线。

19、在一些实施例中,组合电路包括印刷电路板(pcb)。

20、在一些实施例中,半导体器件封装还包括分别位于多个晶体管放大器管芯中的一些晶体管放大器管芯与组合电路之间的多个输出预匹配电路。

21、在一些实施例中,组合电路包括多个输出预匹配电路中的至少一个输出预匹配电路的电容器。

22、在一些实施例中,多个输出预匹配电路中的至少一个包括通过键合线耦合到组合电路的电容器。

23、在一些实施例中,多个晶体管放大器管芯是第二晶体管放大器管芯,并且至少一个输出引线是至少一个第二输出引线,并且半导体器件封装还包括耦合到半导体器件封装的多个输入引线中的第一输入引线的第一晶体管放大器管芯。

24、在一些实施例中,第一晶体管放大器管芯是doherty放大器的主放大器,并且多个第二晶体管放大器管芯是doherty放大器的峰化放大器。

25、在一些实施例中,组合电路还被配置为将来自多个第二晶体管放大器管芯中的两个或更多个的输出信号与第一晶体管放大器管芯的输出信号进行组合以生成组合输出信号。

- 还没有人留言评论。精彩留言会获得点赞!