用于检测数字电路中时序违例的电路的制作方法

本公开总体上涉及数字电路领域,并且具体来说,涉及数字电路中潜在时序违例的检测。

背景技术:

1、已经提出通过修改提供给集成电路的区域的时钟频率和/或电源电压来提高电路性能和/或降低能耗。

2、然而,在超过时钟频率和电源电压限制所对应的某个工作点后,电路将不再正常工作。具体来说,如果集成电路的同步装置中的一个或更多个发生时序违例,集成电路将不再保持正确的功能。同步装置包括触发器(flip-flop)、存储器和锁存器。这类装置通常由建立时间(setup time)ts表征,应该遵守该建立时间以确保稳定性。建立时间ts定义了有效时钟沿之前的时间段,在该时间段期间同步装置的输入数据不会改变。如果不遵守该建立时间,则会发生时序违例。

3、集成电路设计的静态时序分析能够确定一个或更多个关键传输路径,这些路径是电路中两个同步装置之间传播延迟最长的传输路径。这些关键传输路径上的传播延迟通常用于确定电路的最大允许时钟频率。

4、然而,在各种工作电压下使用静态时序分析来确定最大允许时钟频率不允许考虑某些变量,如需要考虑的pvt-rc变化(过程、电压、温度、电阻-电容寄生)。因此,有必要允许相对较大的裕度(margin),这会导致低效运行。

5、已经提出了允许在电路运行期间评估pvt-rc变化的监测电路。在这些电路中,原位/现场(in-situ/in-field)时序监测器的优点是能将它放置在电路的实际信号传播路径中,并因此在可能发生时序违例时提供准确的局部指示。

6、然而,在有效地为数字电路配置原位时序监测器以及根据原位时序监测器的输出有效地控制电路的电源电压和/或工作频率方面存在着技术困难。

技术实现思路

1、根据一个方面,提供了一种电路,该电路包括:

2、-第一时序守卫电路,其被配置为检测第一数据信号到达第一同步装置的裕量时间何时降到低于第一阈值;和

3、-第二时序守卫电路,其被配置为检测第二数据信号到达第二同步装置的裕量时间何时降到低于第二阈值,第一阈值和第二阈值彼此不相同。

4、根据一个实施例:

5、-第一数据信号由具有第一最差传播延迟的至少一个第一数据路径产生;

6、-第二数据信号由具有大于第一最差传播延迟的第二最差传播延迟的至少一个第二数据路径产生;并且

7、-第二阈值低于第一阈值。

8、根据一个实施例:

9、-第一阈值是状态阈值,所述状态阈值与所述电路的由所述第一同步装置在所述第一数据信号到达后接收到的时钟信号的时钟沿相距第一时间距离;并且

10、-第二阈值是警报阈值,所述警报阈值与所述电路的由所述第二同步装置在所述第二数据信号到达后接收到的时钟信号的时钟沿相距第二时间距离,第二阈值低于第一阈值。

11、根据一个实施例,该电路包括多个所述第一时序守卫电路和时序响应电路,例如通过状态标志处理电路和控制电路实现,其配置为:

12、-当第一数据信号的裕量时间降到低于第一阈值时,接收来自所述多个第一时序守卫电路的状态标志信号;

13、-将所述多个第一时序守卫电路所产生的标志信号的数量与阈值进行比较;

14、-响应于标志记信号的数量超过阈值,对电路的时钟信号进行第一电源电压或偏置电压调整和/或第一频率降低。

15、根据一个实施例,该电路包括多个所述第二时序守卫电路和保护电路,例如通过警报标志处理电路和时钟安全电路实现,其配置为:

16、-当第二数据信号的裕量时间降到低于第二阈值时,接收来自所述多个第二时序守卫电路的警报标志信号;并且

17、-响应于来自第二时序守卫电路中任一个第二时序守卫电路的警报信号,对电路的时钟信号进行第二频率降低。

18、根据一个实施例,第一频率调整是不超过30%的频率降低,第二频率调整是超过30%的频率降低。

19、根据一个实施例,时序响应电路被配置为从警报标志信号的断言开始,在电路的时钟信号的10个时钟周期内,并且优选在5个时钟周期内实施第二频率调整。

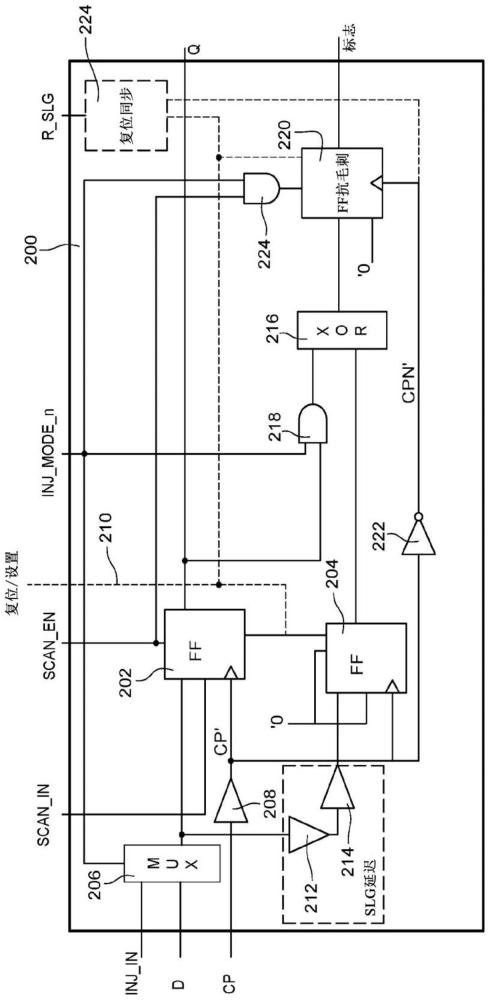

20、根据一个实施例,第一时序守卫电路和第二时序守卫电路中的每个包括:

21、-耦合在其时钟输入和第一同步装置的时钟输入节点之间的第一延迟缓冲器。

22、根据一个实施例,第一时序守卫电路和第二时序守卫电路中的每个包括:

23、-串联耦合在其数据输入和另一同步装置的数据输入之间的第二延迟元件和第三延迟元件,其中由第一时序守卫电路的第三延迟元件引入的延迟不同于由第二时序守卫电路的第三延迟元件所引入的延迟。

24、根据另一方面,提供了一种在电路中进行时序控制的方法,该方法包括:

25、-由第一时序守卫电路,检测第一数据信号到达第一同步装置的裕量时间何时降到低于第一阈值;和

26、-由第二时序守卫电路,检测第二数据信号到达第二同步装置的裕量时间何时降到低于第二阈值,第一阈值和第二阈值彼此不同。

27、根据一个实施例:

28、-第一数据信号由具有第一最差传播延迟的至少一个第一数据路径产生;

29、-第二数据信号由具有大于第一最差传播延迟的第二最差传播延迟的至少一个第二数据路径产生,第二阈值低于第一阈值。

30、根据一个实施例:

31、-第一阈值是状态阈值,所述状态阈值与所述电路的由所述第一同步装置在所述第一数据信号到达后接收到的时钟信号的时钟沿相距第一时间距离;并且

32、-第二阈值是警报阈值,所述警报阈值与所述电路的由所述第二同步装置在所述第二数据信号到达后接收到的时钟信号的时钟沿相距第二时间距离,第二阈值低于第一阈值。

33、根据一个实施例,该电路包括多个所述第一时序守卫电路和时序响应电路,所述时序响应电路例如通过状态标志处理电路和控制电路实现,该方法还包括:

34、-当第一数据信号的裕量时间降到低于第一阈值时,由时序响应电路接收来自所述多个第一时序守卫电路的状态标志信号;

35、-由时序响应电路,将所述多个第一时序守卫电路所产生的标志信号的数量与阈值进行比较;

36、-响应于标志信号的数量超过阈值,由时序响应电路对电路的时钟信号进行第一电源电压或偏置电压调整和/或第一频率降低。

37、根据一个实施例,该电路包括多个所述第二时序守卫电路和保护电路,所述保护电路例如通过警报标志处理电路和时钟安全电路实现,该方法还包括:

38、-当第二数据信号的裕量时间降到低于所述第二阈值时,由保护电路接收来自所述多个第二时序守卫电路的警报标志信号;并且

39、-响应于来自第二时序守卫电路中任一个第二时序守卫电路的警报信号,由保护电路对电路的时钟信号进行第二频率降低。

40、根据又一方面,提供了一种电路,该电路包括:

41、-第一时序守卫电路,其被配置为当检测到第一数据信号到达第一时序守卫电路的第一同步装置的裕量时间降到低于第一阈值时,断言(assert)第一警报标志;

42、-第二时序守卫电路,其被配置为当检测到第二数据信号到达第二时序守卫电路的第一同步装置的裕量时间降到低于第一阈值或低于不同于第一阈值的第二阈值时,断言第二警报标志;和

43、-第一标志收集器电路,其包括:第一异步检测装置,其被配置为当第一警报标志被断言时,在第一标志收集器电路的第一标志输出处断言第一输出信号;和第二异步检测装置,其被配置为当第二警报标志被断言时,在第一标志输出处断言第一输出信号。

44、根据一个实施例,该电路包括保护电路,例如通过警报标志处理电路和时钟安全电路实现,该保护电路被配置为:

45、-接收第一输出信号;并且

46、-响应于第一输出信号,对电路的时钟信号进行第一频率降低。

47、根据一个实施例,电路还包括第三时序守卫电路,该第三时序守卫电路被配置为当检测到第三数据信号到达第三时序守卫电路的第一同步装置的裕量时间降到低于第三阈值时断言状态标志,其中:

48、-第三阈值是状态阈值,所述状态阈值与所述电路的由第三时序守卫电路的第一同步装置在第三数据信号到达后接收到的时钟信号的时钟沿相距第一时间距离;并且

49、-第一阈值是警报阈值,所述警报阈值与所述电路的由第一时序守卫电路的第一同步装置在所述第一数据信号到达后接收到的时钟信号的时钟沿相距第二时间距离,第一阈值低于第三阈值。

50、根据一个实施例,该电路包括多个所述第三时序守卫电路和时序响应电路,所述时序响应电路例如通过状态标志处理电路和控制电路实现,并耦合到第一标志收集器电路的输出,该时序响应电路被配置为:

51、-当第三数据信号的裕量时间降到低于第三阈值时,接收来自所述多个第三时序守卫电路的状态标志信号;

52、-将所述多个第三时序守卫电路所产生的标志信号的数量与阈值进行比较;

53、-响应于标志信号的数量超过阈值,对电路的时钟信号进行第一电源电压或偏置电压调整和/或第一频率降低。

54、根据一个实施例,该电路包括:

55、-第二标志收集器电路,其被配置为在第二标志收集器电路的第二标志输出处断言第二输出信号;和

56、-耦合到第一标志输出和第二标志输出的主标志收集器电路,并且其被配置为当第一输出信号或第二输出信号被断言时生成主标志输出信号。

57、根据一个实施例:

58、-第一异步检测装置包括第一设置-复位触发器,其中第一标志应用于第一设置-复位触发器的设置或复位输入;并且

59、-第二异步检测装置包括第二设置-复位触发器,其中第二标志应用于第二设置复位-触发器的设置或复位输入。

60、根据一个实施例,第一异步检测装置和第二异步检测装置的输出通过或树耦合到第一标志输出。

61、根据又一方面,提供了一种在电路中检测裕量时间减少的方法,该方法包括:

62、-当检测到第一数据信号到达第一时序守卫电路的第一同步装置的裕量时间降到低于第一阈值时,由第一时序守卫电路断言第一警报标志;

63、-当检测到第二数据信号到达第二时序守卫电路的第一同步装置的裕量时间降到低于第一阈值或低于不同于第一阈值的第二阈值时,由第二时序守卫电路断言第二警报标志;

64、-当第一警报标志被断言时,由第一标志收集器电路的第一异步检测装置,在第一标志收集器电路的第一标志输出处断言第一输出信号;并且

65、-当第二警报标志被断言时,由第一标志收集器电路的第二异步检测装置,在第一标志输出处断言第一输出信号。

66、根据一个实施例,该方法还包括:

67、-由第二标志收集器电路,在第二标志收集器电路的第二标志输出处断言第二输出信号;和

68、-当第一输出信号或第二输出信号被断言时,由耦合到第一标志输出和第二标志输出的主标志收集器电路,产生主标志输出。

69、根据一个实施例,该方法包括:

70、-将第一标志应用于第一异步检测装置的第一设置-复位触发器的设置或复位输入;并且

71、-将第二标志应用于第二异步检测装置的第二设置-复位触发器的设置或复位输入。

72、根据一个实施例,该方法还包括:

73、-由电路的保护电路接收第一输出信号;

74、-响应于第一输出信号,由保护电路对电路的时钟信号进行第一频率降低。

75、根据一个实施例,该电路还包括第三时序守卫电路,所述第三时序守卫电路被配置为当检测到第三数据信号到达第三时序守卫电路的第一同步装置的裕量时间降到低于第三阈值时断言状态标志,其中:

76、-第三阈值是状态阈值,所述状态阈值与所述电路的由第三时序守卫电路的第一同步装置在第三数据信号到达后接收到的时钟信号的时钟沿相距第一时间距离;并且

77、-第一阈值是警报阈值,所述警报阈值与所述电路的由第一时序守卫电路的第一同步装置在所述第一数据信号到达后接收到的时钟信号的时钟沿相距第二时间距离,第一阈值低于第三阈值。

78、根据一个实施例,该电路包括多个所述第三时序守卫电路和时序响应电路,并且该时序响应电路耦合到第一标志收集器电路的输出,该方法还包括:

79、-当第三数据信号的裕量时间降到低于第三阈值时,由时序响应电路接收来自所述多个第三时序守卫电路的状态标志信号;

80、-由时序响应电路,将所述多个第三时序守卫电路所产生的标志信号的数量与阈值进行比较;

81、-响应于标志信号的数量超过阈值,由时序响应电路对电路的时钟信号进行第一电源电压或偏置电压调整和/或第一频率降低。

82、根据一个实施例,该方法还包括通过或树将第一异步检测装置和第二异步检测装置的第一输出信号和第二输出信号提供给第一标志输出。

- 还没有人留言评论。精彩留言会获得点赞!