一种用于电源管理芯片的快速电平位移电路

本发明属于微电子,具体涉及一种用于电源管理芯片的快速电平位移电路。

背景技术:

1、随着电源管理技术日趋成熟,电源管理芯片已经成为了电子产品中不可缺少的一部分。电平位移电路作为电源管理芯片的核心电路之一,其性能直接影响电源管理芯片的性能特性。

2、图1为一种传统的电平位移电路,主要由高压nmos管m1、低压pmos管m2、低压nmos管m3、电阻r1和齐纳二极管z1组成。当输入端in为高电平时,nmos管m1管打开,nmos管m1的漏极电压被拉低,齐纳二极管与电阻r1并联目的为防止nmos管m1的漏极电压拉低使pmos管m2的栅氧化层击穿,输出端out为高。当输入端in为低电平时,nmos管m1关闭,nmos管m1的漏极电压被拉高,输出端out为低。传统的电平移位电路具有功耗大,延时大,上升沿延时和下降沿延时不一致等缺点,使得传统的电平位移电路在高精度系统中的应用受到限制。

技术实现思路

1、本发明旨在解决以上现有技术的问题。提出了一种用于电源管理芯片的快速电平位移电路。本发明的技术方案如下:

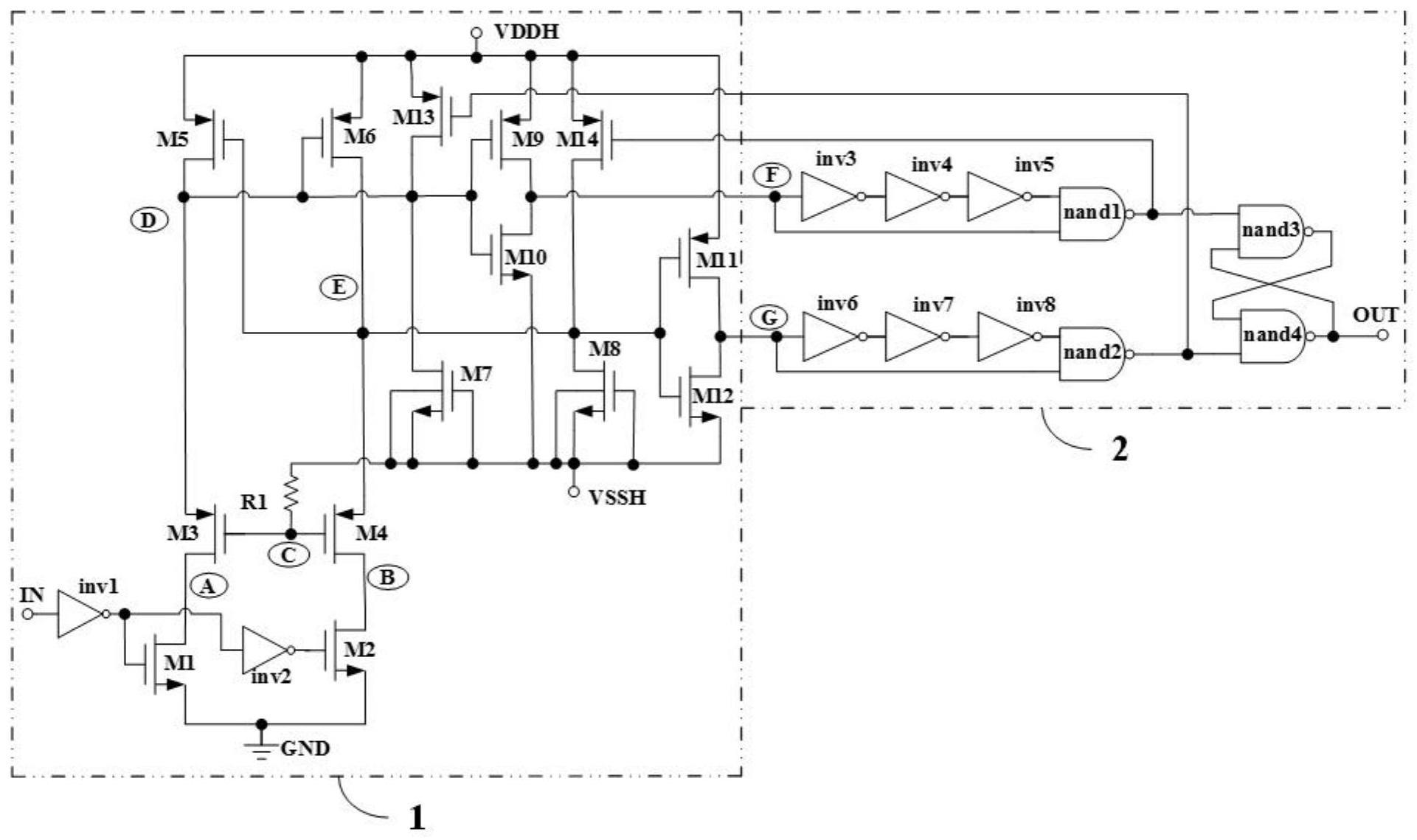

2、一种用于电源管理芯片的快速电平位移电路,其包括:电平位移核心电路(1)及低延时通路检测电路(2),其中,所述电平位移核心电路(1)的信号输出端连接所述低延时通路检测电路(2)的信号输入端,所述低延时通路检测电路(2)的信号输出端连接所述电平位移核心电路(1)的信号输入端;所述电平位移核心电路(1)为所述低延时通路检测电路(2)提供两个控制信号,所述低延时通路检测电路(2)在输出端产生一个高压输出信号。

3、进一步的,所述电平位移核心电路(1)包括:反相器inv1、反相器inv2、nmos管m1、nmos管m2、pmos管m3、pmos管m4、pmos管m5、pmos管m6、nmos管m7、nmos管m8、pmos管m9、nmos管m10、pmos管m11、nmos管m12、pmos管m13、pmos管m14及电阻r1,其中反相器inv1的输入端与电路输入端in相连,反相器inv1的输出端分别与nmos管m1的栅极以及反相器inv2的输入端相连,反相器inv2的输出端与nmos管m2的栅极相连,pmos管m5的源极分别与pmos管m6的源极、pmos管m13的源极、pmos管m9的源极、pmos管m14的源极、pmos管m11的源极以及高压域电源端vddh相连,pmos管m5的栅极分别与pmos管m6的漏极、pmos管m4的源极、pmos管m14的漏极、nmos管m8的漏极、pmos管m11的栅极以及nmos管m12的栅极相连,pmos管m5的漏极分别与pmos管m3的源极、pmos管m6的栅极、pmos管m13的漏极、pmos管m9的栅极、nmos管m10的栅极以及nmos管m7的漏极相连,pmos管m3的栅极分别与电阻r1的一端以及pmos管m4的栅极相连,电阻r1的另一端分别与nmos管m7的衬底、nmos管m7的源极、nmos管m7的栅极、nmos管m10的源极、nmos管m8的衬底、nmos管m8的源极、nmos管m8的栅极、nmos管m12的源极以及高压域低电源端vssh相连,pmos管m3的漏极与nmos管m1的漏极相连,nmos管m1的源极分别与nmos管m2的源极以及外部地线gnd相连,pmos管m4的漏极与nmos管m2的漏极相连,pmos管m9的漏极分别与nmos管m10的漏极、反相器inv3的输入端以及与非门nand1的一输入端相连,pmos管m11的漏极分别与nmos管m12的漏极、反相器inv6的输入端以及与非门nand2的一输入端相连。

4、进一步的,所述低延时通路检测电路(2)包括:反相器inv3、反相器inv4、反相器inv5、反相器inv6、反相器inv7、反相器inv8、与非门nand1、与非门nand2、与非门nand3以及与非门nand4,其中反相器inv3的输出端与反相器inv4的输入端相连,反相器inv4的输出端与反相器inv5的输入端相连,反相器inv5的输出端与与非门nand1的另一输入端相连,与非门nand1的输出端分别与pmos管m14的栅极以及与非门nand3的一输入端相连,与非门nand3的另一输入端分别与与非门nand4的输出端以及电路的输出端out相连,与非门nand3的输出端与与非门nand4的一输入端相连,反相器inv6的输出端与反相器inv7的输入端相连,反相器inv7的输出端与反相器inv8的输入端相连,反相器inv8的输出端与与非门nand2的另一端相连,与非门nand2的输出端分别与pmos管m13的栅极以及与非门nand4的另一输入端相连。

5、进一步的,所述电平位移核心电路(1)中,反相器inv1与反相器inv2的工作电压为vdd且低于高压域低电源端vssh电压vssh及高压域电源端vddh电压vddh,其中vddh-vssh=5v,nmos管m1、nmos管m2、pmos管m3及pmos管m4均为具有大尺寸的高压功率管且其漏源之间的最大耐压大于vddh,电阻r1使pmos管m5漏极即节点d电压vd或pmos管m6漏极即节点e电压ve能快速的从vddh降为vssh;pmos管m13和pmos管m14为上拉mos管,电压vd或电压ve能快速上升;栅极、源极和衬底短接的nmos管m7和nmos管m8实现的二极管使得电压vd和ve不低于vssh-0.7,从而使得pmos管m5和pmos管m6的源极与栅极之间的压差始终小于其击穿电压,pmos管m9和pmos管m11的源极与栅极之间的压差始终小于其击穿电压,确保电路器件可靠性;当电路输入端in的输入信号从0变为vdd时,nmos管m1的漏极即节点a电压va升高,电压vd从vssh变为vddh,从而使得pmos管m9的漏极即节点f电压vf从vddh变为vssh,同时nmos管m2的漏极即节点b电压vb降到外部地线gnd电位,大尺寸高压功率pmos管m4的栅漏电容cgd4使得高压功率pmos管m4的栅极即节点c电压vc降低,进而电压ve降低到约为vssh,从而pmos管m11的漏极即节点g电压vg从vssh变为vddh;同理,当电路输入端in的输入信号从vdd变为0时,nmos管m1管开启,nmos管m2截止,电压vf从vssh变为vddh,电压vg从vddh变为vssh。

6、进一步的,所述低延时通路检测电路(2)中,反相器inv3、反相器inv4、反相器inv5、反相器inv6、反相器inv7、反相器inv8、与非门nand1、与非门nand2、与非门nand3以及与非门nand4的工作电源电压为高压域电源端vddh的电压vddh及工作地电压为高压域低电源端vssh的电压vssh,当电路输入端in的输入信号从0变为反相器inv1的工作电源电压vdd时,pmos管m9的漏极即节点f电压vf从vddh变为vssh,通过由反相器inv3、反相器inv4及反相器inv5构成的延迟链使得与非门nand1输出端电压保持为vddh,同时pmos管m11的漏极即节点g电压vg从vssh变为vddh,通过由反相器inv6、反相器inv7及反相器inv8构成的延迟链使得与非门nand2输出端产生一个从vddh向vssh的下脉冲信号,脉冲宽度为由反相器inv6、反相器inv7及反相器inv8构成的延迟链的延迟时间,从而使得电路输出端out的电压从vssh变为vddh,与输入端in的输入信号变化一致;同理,当电路输入端in的输入信号从vdd变为0时,与非门nand1输出端产生一个从vddh向vssh的下脉冲信号,脉冲宽度为由反相器inv3、反相器inv4及反相器inv5构成的延迟链的延迟时间,与非门nand2输出端电压保持为vddh,从而使得电路输出端out从vddh变为vssh,与输入端in的输入信号变化一致。

7、进一步的,当电路输入端in的输入信号从0变为vdd时,电路输出端out也从vssh变为vddh,其中vdd为反相器inv1的工作电源电压,vssh为高压域低电源端vssh电压,vddh为高压域电源端vddh电压,在此过程中,从输入端in到输出端out的延时由反相器inv1的延迟时间t1、反相器inv2的延迟时间t2、nmos管m2栅极到节点e的延迟时间t3、节点e到与非门nand2输出端的延迟时间t4、与非门nand2输出端到电路输出端out的延迟时间t5构成,其中延迟时间t3占比最大,瞬态增强电阻r1与大沟道宽长比的pmos管m3和pmos管m4的栅源电容及栅漏电容构成电阻-电容延迟,使得节点c电压vc与高压域低电源端vssh电压具有一定的延迟时间,同时nmos管m2开启,节点b电压vb快速下降并通过pmos管m4栅漏电容的耦合使得电压vc较低,pmos管m4栅-源电压|vgs4|=|vc-ve|较大且工作在饱和区电流i4较大;栅极、源极与衬底短接nmos管m8实现的二极管使得电压ve最小值不低于vssh-0.7,因而延迟时间t3=ce(vddh-vssh+0.7)/i4,大的电流i4能有效地降低延迟时间t3,其中,ce为节点e的寄生电容。

8、进一步的,当电路输入端in的输入信号从vdd变为0时,电路输出端out也从高电压vddh变为低电压vssh,其中vdd为反相器inv1的工作电源电压,vssh为高压域低电源端vssh电压,vddh为高压域电源端vddh电压,在此过程中,从输入端in到输出端out的延时主要由反相器inv1的延时时间t1、nmos管m1的栅极到节点d的延时时间t2b、节点d到与非门nand1输出端的延时时间t3b、与非门nand1输出端到电路输出端out的延时时间t4b构成,其中延时时间t2b占比最大,瞬态增强电阻r1与大沟道宽长比的pmos管m3和pmos管m4的栅源电容及栅漏电容构成电阻-电容延迟,使得节点c电压vc与高压域低电源端vssh电压具有一定的延迟时间,同时nmos管m1开启,节点a电压va快速下降并通过pmos管m3栅漏电容的耦合使得电压vc较低,pmos管m3栅-源电压|vgs3|=|vc-vd|较大且工作在饱和区电流i3较大。栅极、源极与衬底短接nmos管m7实现的二极管使得电压vd最小值不低于vssh-0.7,因而延迟时间t2b=cd(vddh-vssh+0.7)/i3,大的电流i3能有效地降低延迟时间t2b,其中,cd为节点d的寄生电容。

9、本发明的优点及有益效果如下:

10、本发明通过提供一种用于电源管理芯片的快速电平位移电路,采用电阻r1使得pmos管m5漏极或pmos管m6漏极的电压能快速的从vddh降为vssh,提高电路的瞬态特性,缩短电路电压转换的延迟时间并减少开关损耗;采用pmos管m13和pmos管m14构成上拉mos管,使pmos管m5漏极或pmos管m6漏极的电压能快速上升,减少开关损耗;采用栅极、源极和衬底短接的nmos管m7和nmos管m8来实现二极管,使得pmos管m5漏极电压以及pmos管m6漏极电压的低电位均不低于vssh-0.7,确保电路器件可靠性,采用反相器inv3-inv5构成延迟链以及反相器inv6-inv8构成延迟链的结构,在与非门nand1输出端或与非门nand2输出端产生一个下脉冲信号,进而在电路输出端out产生一个与输入端in的输入信号变化一致的高压输出信号,从而实现高性能的快速电平位移电路。

- 还没有人留言评论。精彩留言会获得点赞!