一种高速锁存比较器及其偏置电路

本发明属于比较器,具体涉及一种高速锁存比较器及其偏置电路。

背景技术:

1、比较器是模拟集成电路中常用的模块,广泛存在于模数转换器中,比较器通过对差分输入的模拟信号进行比较来产生数字逻辑输出。比较器的速度和精度和其功耗直接相关,可以通过对比较器的电流进行控制来实现对比较器的功耗、速度以及精度的控制。比较器作为模数转换器特别是流水线型模数转换器的核心模块,其速度和比较精度会直接影响流水线型模数转换器的性能指标。流水线型模数转换器由多个子级模数转换器构成,子级模数转换器中电路的性能要求具有随着级数增加而减小的特点。针对流水线型模数转换器这一特点,可以通过给不同子级模数转换器提供不同的偏置电流来对比较器的功耗和速度进行折衷。

技术实现思路

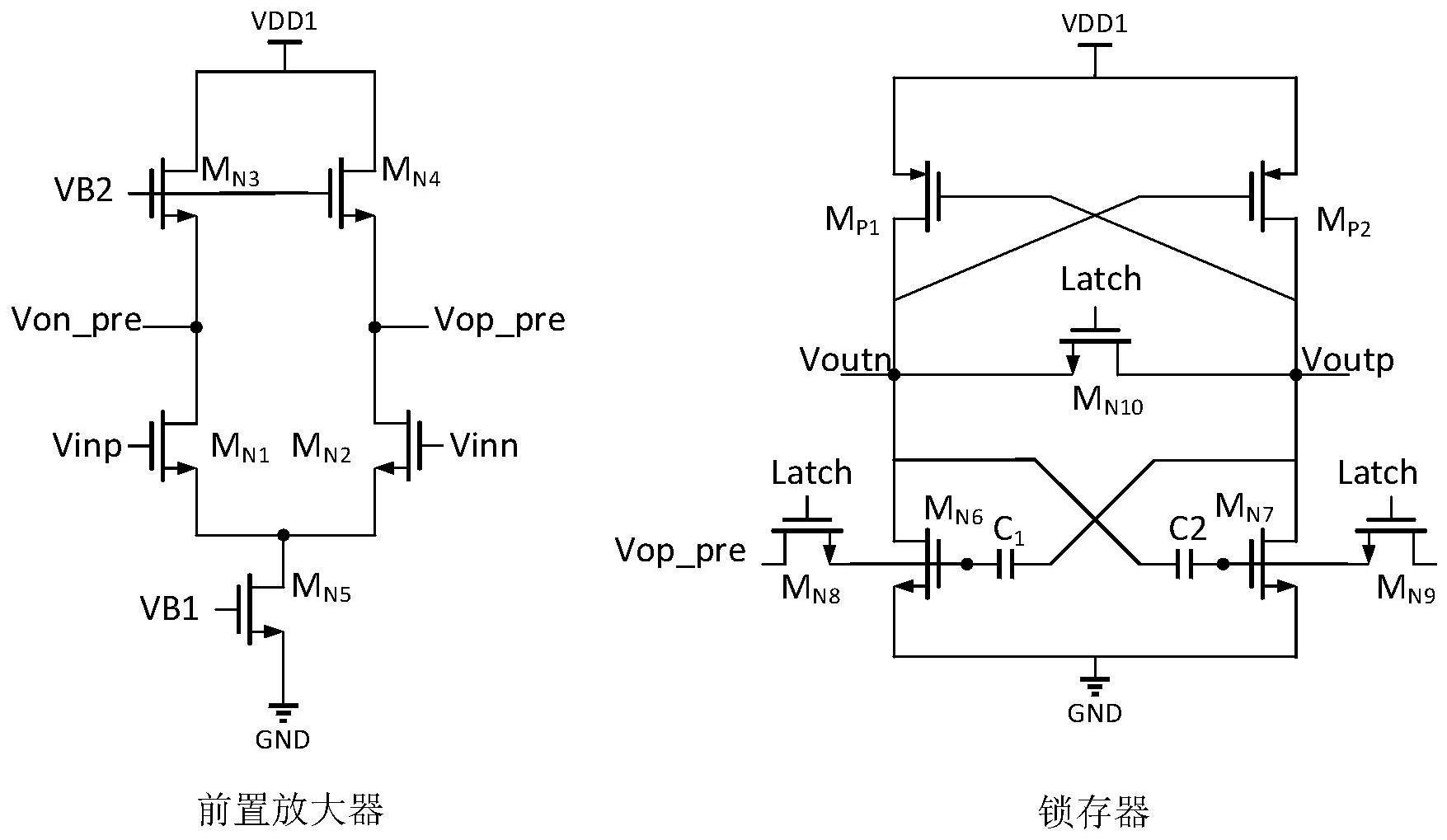

1、有鉴于此,本发明提出一种一种高速锁存比较器及其偏置电路。比较器结构如图1所示,采用了一种前置放大器加高速锁存器的结构,其中前置放大器将输入信号和锁存器进行隔离,减小回踢噪声的同时可以提供一定的增益和带宽,高速锁存器中引入了交叉耦合电容,可以提高锁存器中放大单元中晶体管的跨导,从而提高比较器的速度。偏置电路的结构如图2所示,可以通过调节第一电流源i1和第二电流源i2来产生偏置电压vb1和vb2,偏置电压对前置放大器进行偏置,从而间接控制前置放大器和锁存器的电流。

2、本发明的技术方案为:

3、一种高速锁存比较器及其偏置电路,包括前置放大器、锁存器、偏置电路;

4、所述前置放大器设置于输入信号与锁存器之间,用于隔离输入信号与锁存器并进行信号放大,可减小回踢噪声并提供一定的增益和带宽;

5、所述锁存器用于接收并比较前置放大器输出的放大信号;

6、所述偏置电路用于给前置放大器提供偏置电压,同时调节前置放大器和锁存器的电流。

7、进一步的,前置放大器包括第一nmos管mn1、第二nmos管mn2、第三nmos管mn3、第四nmos管mn4、第五nmos管mn5;

8、第一nmos管mn1的栅极连接输入正信号,源极连接第五nmos管mn5的漏极,第一nmos管mn1的漏极为前置放大器的负信号输出端,第一nmos管mn1的漏极连接第三nmos管mn3的源极;

9、第二nmos管mn2的栅极连接输入负信号,源极连接第五nmos管mn5的漏极,第二nmos管mn2的漏极为前置放大器的正信号输出端,第二nmos管mn2的连接第四nmos管mn4的源极;

10、第三nmos管mn3的栅极连接第二偏置电压vb2,漏极连接第一电源vdd1;

11、第四nmos管mn4的栅极连接第二偏置电压vb2,漏极连接第一电源vdd1;

12、第五nmos管mn5的栅极连接第一偏置电压vb1,源极连接地。

13、进一步的,所述锁存器包括第一pmos管mp1、第二pmos管mp2、第六nmos管mn6、第七nmos管mn7、第八nmos管mn8、第九nmos管mn9、第十nmos管mn10、第一电容c1、第二电容c2;

14、第一pmos管mp1的栅极为锁存器的正信号输出端,连接第二pmos管mp2、第十nmos管mn10和第七nmos管mn7的漏极,第一pmos管mp1的源极连接第一电源vdd1,第一pmos管mp1的漏极为锁存器的负信号输出端,第一pmos管mp1的漏极连接第二pmos管mp2的栅极、第十nmos管mn10的源极和第六nmos管mn6的漏极;

15、第二pmos管mp2的栅极为锁存器负信号输出端,连接第一pmos管mp1和第六nmos管mn6的漏极以及第十nmos管mn10的源极,第二pmos管mp2的源极连接第一电源vdd1,第二pmos管mp2的漏极为锁存器的正信号输出端,第二pmos管mp2的漏极连接第一pmos管mp1的栅极、第十nmos管mn10的漏极和第七nmos管mn7的漏极;

16、第六nmos管mn6通过第八nmos管mn8来接收前置放大器的输出正信号,第六nmos管mn6的栅极连接第八nmos管mn8的源极和第一电容c1的第二连接端,第六nmos管mn6的源极连接地,第六nmos管mn6的漏极为锁存器负信号输出端,第六nmos管mn6的漏极连接第一pmos管mp1的漏极、第十nmos管mn10的源极和第二电容c2的第一连接端;

17、第七nmos管mn7的栅极连接第九nmos管mn9的源极和第二电容c2的第二连接端,第七nmos管mn7的源极连接地,第七nmos管mn7的漏极为锁存器正信号输出端,第七nmos管mn7的漏极连接第二pmos管mp2的漏极、第十nmos管mn10的漏极和第一电容c1的第一连接端;

18、第八nmos管mn8的栅极连接latch时钟信号,源极连接第六nmos管mn6的栅极和第一电容c1的第二连接端,第八nmos管mn8的漏极连接前置放大器的正输出信号;

19、第九nmos管mn9的栅极连接latch时钟信号,源极连接第七nmos管mn7的栅极和第二电容c2的第二连接端,第九nmos管mn9的漏极连接前置放大器的负输出信号;

20、第十nmos管mn10的栅极连接latch时钟信号,源极为锁存器负信号输出端,连接第一pmos管mp1和第六nmos管mn6的漏极和第二电容c2的第一连接端,第十nmos管mn10的漏极为锁存器的正信号输出端,第十nmos管mn10的漏极连接第二pmos管mp2和第七nmos管mn7的漏极、第一电容c1的第一连接端。

21、进一步的,所述偏置电路包括第一电流源i1、第二电流源i2、第一放大器amp1、第二放大器amp2、第三pmos管mp3、第十一nmos管mn11、第十二nmos管mn12、第十三nmos管mn13、第十四nmos管mn14、第十五nmos管mn15、第十六nmos管mn16;

22、第一电流源i1的第一连接端连接第二电源电压vdd2,第二连接端输出第一偏置电压vb1,第二连接端连接第十一nmos管mn11和第十二nmos管mn12的栅极以及第十三nmos管mn13的漏极;

23、第二电流源i2的第一连接端连接第二电源电压vdd2,第二连接端连接第三pmos管mp3的源极和栅极以及第二放大器amp2的负输入端;

24、第一放大器amp1的正输入端连接第十六nmos管mn16的栅极,负输入端连接第十四nmos管mn14的漏极和第十五nmos管mn15的源极,第一放大器amp1的输出端输出第二偏置电压vb2,第一放大器amp1的输出端连接第十五nmos管mn15的栅极;

25、第二放大器amp2的正输入端连接第一电源电压vdd1,负输入端连接第二电源i2的第二连接端和第三pmos管mp3的源极和漏极;

26、第三pmos管mp3的栅极和源极相连,并连接第二放大器amp2的负输入端和第二电源i2的第二连接端;

27、第十一nmos管mn11的栅极连接第一电流源i1的第二连接端和第十二nmos管mn12的栅极,第十一nmos管mn11的源极连接地,第十一nmos管mn11的漏极连接第十三nmos管mn13的源极;

28、第十二nmos管mn12的栅极连接第一电流源i1的第二连接端和第十一nmos管mn11的栅极,第十二nmos管mn12的源极连接地,第十二nmos管mn12的漏极连接第十四nmos管mn14的源极;

29、第十三nmos管mn13的栅极为前置放大器输入共模电压vcm端,第十三nmos管mn13的栅极连接第十四nmos管mn14的栅极,第十三nmos管mn13的源极连接第十一nmos管mn11的漏极,第十三nmos管mn13的漏极连接第一电流源i1的第二连接端以及第十一nmos管mn11和第十二nmos管mn12的栅极;

30、第十四nmos管mn14的源极连接第十二nmos管mn12的漏极,第十四nmos管mn14的漏极连接第十五nmos管mn15的源极和第一放大器amp1的负输入端;

31、第十五nmos管mn15的栅极连接第一放大器amp1的输出端,第十五nmos管mn15的源极连接第十四nmos管mn14的漏极和第一放大器amp1的负输入端;

32、第十六nmos管mn16的栅极连接第一放大器amp1的正输入端和第二放大器amp2的输出端,第十六nmos管mn16的源极接地,第十六nmos管mn16的漏极连接第三pmos管mp3的漏极。

33、本发明的有益效果:本发明设计了一种带前置放大器的高速锁存比较器及其偏置电路,前置放大器可以将输入信号和锁存器进行隔离,减小回踢噪声,并且提供一定的增益和带宽,锁存器中的交叉耦合电容的引入可以提供锁存器的速度,同时发明的偏置电路可以通过调节电流从而产生偏置电压vb1和vb2,通过给前置放大器提供的偏置电压vb1和vb2来间接调节前置放大器和锁存器的电流,从而对比较器的功耗和速度进行折衷控制。本发明可用于流水线模数转换器中的各个子级中,偏置电路可以同时偏置多个比较器,每个子级中可以放置一个偏置电路和多个比较器,通过在流水线模数转换器的不同子级中设置不同的偏置电流来对比较器的速度和功耗进行调整,从而达到控制流水线模数转换器中的各个子级的功耗和精度的目的。

- 还没有人留言评论。精彩留言会获得点赞!