可编程逻辑器件的时钟配置方法、装置、设备及介质与流程

本申请属于可编程逻辑器件,涉及一种可编程逻辑器件的时钟配置方法、装置、设备及介质。

背景技术:

1、电磁干扰(electromagneticinterference,简称emi),指电路系统在运行时通过传导干扰或者辐射干扰的方式,对该电路系统的周边电路系统产生影响,因此,为了保证整个电路系统的正常工作,电子产品的研发必须符合相关机构颁布的电磁兼容的规范,确保上市的电子产品满足规范要求。

2、随着集成电路技术的发展,可编程逻辑器件(fpga、cpld等)中数字信号的时钟频率越来越高,改善可编程逻辑器件时钟引起的辐射干扰已经是每一个应用厂商都要面对的问题,传统的技术方案通过在晶振时钟和可编程逻辑器件之间增加展频芯片配置可编程逻辑器件的时钟来达到改善电磁干扰的效果,但是增加展频芯片的同时还会提高产品的硬件成本和研发成本,并且对于已经量产的可编程逻辑器件,增加展频芯片还需要重新测试产品,大幅度拉长了项目时间。

技术实现思路

1、本申请的目的在于提供一种可编程逻辑器件的时钟配置方法、装置、设备及介质,以解决传统技术方案改善电磁干扰时所需成本高的技术问题。

2、为解决上述技术问题,本申请的技术方案如下:

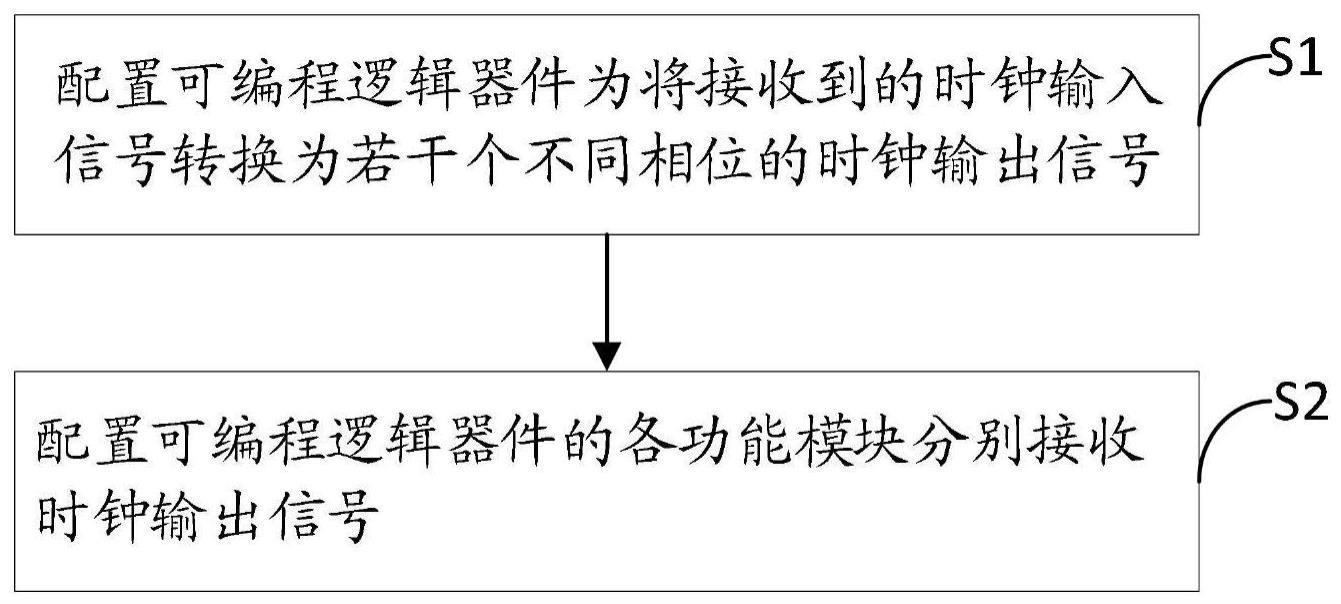

3、本申请提供一种可编程逻辑器件的时钟配置方法,包括:

4、配置所述可编程逻辑器件为将接收到的时钟输入信号转换为若干个不同相位的时钟输出信号;

5、配置所述可编程逻辑器件的各功能模块分别接收所述时钟输出信号;其中,所述功能模块的数量与所述时钟输出信号的数量相同。

6、进一步地,所述可编程逻辑器件的时钟配置方法,还包括:

7、生成配置位流文件,将所述配置位流文件下载至所述可编程逻辑器件以配置所述可编程逻辑器件,配置后的所述可编程逻辑器件用于:

8、接收时钟输入信号,将所述时钟输入信号转换为若干个不同相位的所述时钟输出信号并分别输出至所述可编程逻辑器件的各所述功能模块。

9、进一步地,所述配置所述可编程逻辑器件为将接收到的时钟输入信号转换为若干个不同相位的时钟输出信号的步骤,包括:

10、根据所述功能模块的数量配置所述可编程逻辑器件的锁相环模块,使所述时钟输入信号经所述锁相环模块输出若干个不同相位的所述时钟输出信号。

11、进一步地,所述配置所述可编程逻辑器件的各功能模块分别接收所述时钟输出信号的步骤,包括:

12、例化所述可编程逻辑器件的原语,使所述锁相环模块输出的所述时钟输出信号为所述可编程逻辑器件全局时钟的时钟信号,或为所述可编程逻辑器件局部时钟的时钟信号,以及

13、使所述锁相环模块输出的所述时钟输出信号能驱动各所述功能模块。

14、进一步地,所述例化所述可编程逻辑器件的原语的步骤之后,还包括:

15、为所述功能模块配置数据缓存器,所述数据缓存器用于实现所述可编程逻辑器件不同时钟域的数据缓存。

16、进一步地,所述例化数据缓存器的步骤之后,还包括:

17、根据所述可编程逻辑器件的区域约束将所述功能模块约束至所述功能模块的布局位置。

18、进一步地,所述根据所述可编程逻辑器件的区域约束将所述功能模块约束至所述功能模块的布局位置的步骤,还包括:

19、约束所述功能模块避开受电磁干扰影响严重的布局位置。

20、基于上述任一可编程逻辑器件的时钟配置方法,本申请还提供一种可编程逻辑器件的时钟配置方法,所述装置包括:

21、第一配置模块,用于配置所述可编程逻辑器件为将接收到的时钟输入信号转换为若干个不同相位的时钟输出信号;

22、第二配置模块,用于配置所述可编程逻辑器件的各功能模块分别接收所述时钟输出信号;其中,所述功能模块的数量与所述时钟输出信号的数量相同;

23、第三配置模块,用于生成配置位流文件,将所述配置位流文件下载至所述可编程逻辑器件以配置所述可编程逻辑器件,配置后的所述可编程逻辑器件用于:

24、接收时钟输入信号,将所述时钟输入信号转换为若干个不同相位的所述时钟输出信号并分别输出至所述可编程逻辑器件的各所述功能模块。

25、基于上述任一可编程逻辑器件的时钟配置方法,本申请还提供一种电子设备,包括:

26、存储器、处理器以及存储在所述存储器中并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现上述任一项所述可编程逻辑器件的时钟配置方法的步骤。

27、基于上述任一可编程逻辑器件的时钟配置方法,本申请还提供一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,所述计算机程序被处理器执行时实现如上述任一项所述可编程逻辑器件的时钟配置方法的步骤。

28、相比于现有技术,本申请的有益效果在于:

29、本申请实施例提供的可编程逻辑器件的时钟配置方法,将可编程逻辑器件接收到的时钟输入信号进行时钟调相,分出多个不同相位的时钟输出信号,让可编程逻辑器件原处于同一时钟域下的各个功能模块能在同一时钟频率下的不同相位运行,使可编程逻辑器件内部的逻辑单元和相关电路器件避开了同一个时刻翻转的场景,进而让时钟辐射明显降低,在不增加额外硬件成本的基础上就能改善电磁干扰。

30、此外,本申请实施例提供的可编程逻辑器件的时钟配置方法还能根据实际需求进行多次迭代,不仅避免了重新设计硬件的复杂度,缩短了项目设计的时间周期,并且让产品在不同应用场景需求下通过升级可编程逻辑器件的位流便可以达到改善电磁干扰效果,如使用本申请实施例提供的可编程逻辑器件的时钟配置方法后还需要进一步降低电磁干扰的影响,则可以在上一次使用的基础上继续对时钟输入信号进行分解,以进一步降低电磁干扰。

技术特征:

1.一种可编程逻辑器件的时钟配置方法,其特征在于,包括:

2.如权利要求1所述的可编程逻辑器件的时钟配置方法,其特征在于,还包括:

3.如权利要求1所述的可编程逻辑器件的时钟配置方法,其特征在于,所述配置所述可编程逻辑器件为将接收到的时钟输入信号转换为若干个不同相位的时钟输出信号的步骤,包括:

4.如权利要求3所述的可编程逻辑器件的时钟配置方法,其特征在于,所述配置所述可编程逻辑器件的各功能模块分别接收所述时钟输出信号的步骤,包括:

5.如权利要求4所述的可编程逻辑器件的时钟配置方法,其特征在于,所述例化所述可编程逻辑器件的原语的步骤之后,还包括:

6.如权利要求5所述的可编程逻辑器件的时钟配置方法,其特征在于,所述为所述功能模块配置数据缓存器的步骤之后,还包括:

7.如权利要求6所述的可编程逻辑器件的时钟配置方法,其特征在于,所述根据所述可编程逻辑器件的区域约束将所述功能模块约束至所述功能模块的布局位置的步骤,还包括:

8.一种可编程逻辑器件的时钟配置装置,其特征在于,包括:

9.一种电子设备,包括存储器、处理器以及存储在所述存储器中并可在所述处理器上运行的计算机程序,其特征在于,所述处理器执行所述计算机程序时实现如权利要求1至7中任一项所述可编程逻辑器件的时钟配置方法的步骤。

10.一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现如权利要求1至7中任一项所述可编程逻辑器件的时钟配置方法的步骤。

技术总结

本申请属于可编程逻辑器件技术领域,公开了一种可编程逻辑器件的时钟配置方法、装置、设备及介质。本申请提供的方法包括:配置可编程逻辑器件为将接收到的时钟输入信号转换为若干个不同相位的时钟输出信号;配置可编程逻辑器件的各功能模块分别接收时钟输出信号;功能模块的数量与时钟输出信号的数量相同;本申请将可编程逻辑器件接收到的时钟输入信号进行时钟调相,分出多个不同相位的时钟输出信号,让可编程逻辑器件原处于同一时钟域下的各个功能模块能在同一时钟频率下的不同相位运行,使可编程逻辑器件内部的逻辑单元和相关电路器件避开了同一个时刻翻转的场景,进而让时钟辐射明显降低,在不增加额外硬件成本的基础上就能改善电磁干扰。

技术研发人员:郭紫仕,张晋,包朝伟

受保护的技术使用者:深圳市紫光同创电子有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!