一种高线性度多比特相位插值器的制作方法

1.本发明涉及电子电路技术领域,尤其涉及一种高线性度多比特相位插值器。

背景技术:

2.目前,电信息在多数情况下是以高速串行传输的方式进行交互。在使用高速串行传输的过程中,需要使用时钟与数据恢复(clock and data recovery ,cdr)电路来对接收到的数据进行与时钟的校准工作,这就需要大量不同相位的时钟来对数据进行最优位置的采样。在使用普通电荷泵(charge pump ,cp)锁相环(phase locked loop ,pll)的情况下,通常使用相位插值电路来生成多种不同相位的时钟。

3.相位插值电路需要根据接收到的数据和时钟进行具体和实时地调整相位。传统的相位插值电路采用相位矢量合成的近似方法实现全平面360度的相位移动,该方法将输入信号分为i、q两路,通过尾电流的大小改变i、q路信号的权重,以实现在全平面内相位移动的功能。但是对于移相步进较小的高比特相位插值器,i、q路电流权重的控制变得较为复杂,且是由近似值组合而成,这对于相位插值器的移相精度和线性度造成很大的影响,从而导致系统抖动的增加,降低了通讯系统的抖动容限,制约了整体系统的稳定性以及所传输数据的准确率。

技术实现要素:

4.发明目的:为了解决现有技术中相位插值电路移相精度和线性度差的问题,本发明提供一种高线性度多比特相位插值器。

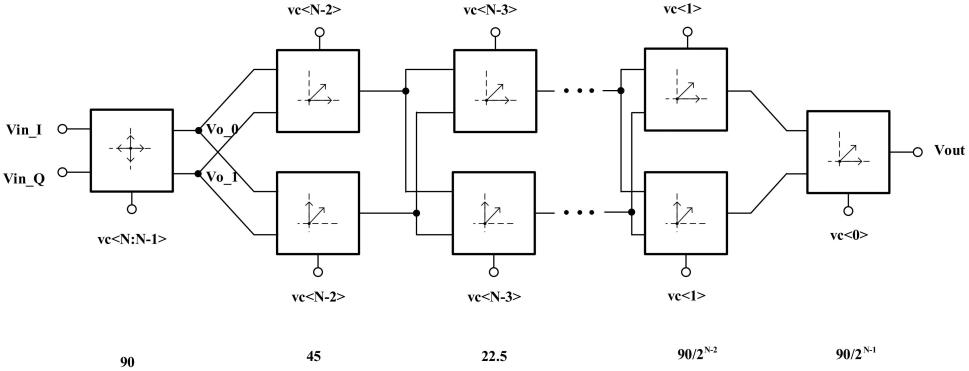

5.技术方案:一种高线性度多比特相位插值器,包括正交相位产生器、一类夹角产生器及二类夹角产生器,一类夹角产生器用于产生第一输出信号或夹角信号,二类夹角产生器用于产生夹角信号或第二输出信号;所述夹角信号的幅值与第一输出信号、第二输出信号的幅值均相同,所述夹角信号的相位为第一输出信号相位与第二输出信号相位的均值;所述正交相位产生器包括第一输出端和第二输出端,分别输出两路相邻的正交信号,第一输出端连接一类夹角产生器和二类夹角产生器的一输入端,第二输出端连接一类夹角产生器和二类夹角产生器的另一输入端,一类夹角产生器、二类夹角产生器的输出端直接连接或者级联后连接末级夹角产生器,所述末级夹角产生器为一类夹角产生器、二类夹角产生器中的一种,所述末级夹角产生器输出相位移动信号。

6.进一步地,所述级联指前一级的一类夹角产生器的输出端连接后一级的一类夹角产生器和二类夹角产生器的一输入端,前一级的二类夹角产生器的输出端连接后一级的一类夹角产生器和二类夹角产生器的另一输入端。

7.进一步地,正交相位产生器输出的两路信号为0

°

、90

°

、180

°

、270

°

相位信号中的两个相邻相位的正交信号。

8.进一步地,所述一类夹角产生器与二类夹角产生器的数量相差一个。

9.进一步地,一类夹角产生器包括输入缓冲单元、一类相位合成单元及输出缓冲单

元,两路输入信号从输入缓冲单元输入,控制信号从一类相位合成单元输入,当控制信号为0时,输出缓冲单元输出第一输出信号,当控制信号为1时,输出缓冲单元输出夹角信号。

10.进一步地,二类夹角产生器包括输入缓冲单元、二类相位合成单元及输出缓冲单元,两路输入信号从输入缓冲单元输入,控制信号从二类相位合成单元输入,当控制信号为0时,输出缓冲单元输出夹角信号,当控制信号为1时,输出缓冲单元输出第二输出信号。

11.进一步地,一类相位合成单元包括第一差分通路及第二差分通路,第一差分通路的差分输入端输入第一输入信号,第二差分通路的差分输入端输入第二输入信号,第一差分通路的差分输出端与第二差分通路的差分输出端相连接,第一差分通路工作时始终导通,第二差分通路包含第一开关s1,控制信号为0时,开关s1断开,第二差分通路不工作;控制信号为1时,开关s1导通,第二差分通路正常工作。

12.进一步地,二类相位合成单元包括第一差分通路及第二差分通路,第一差分通路的差分输入端输入第一输入信号,第二差分通路的差分输入端输入第二输入信号,第一差分通路的差分输出端与第二差分通路的差分输出端相连接,第二差分通路工作时始终导通,第一差分通路包含第二开关s2,控制信号为0时,开关s2导通,第一差分通路正常工作;控制信号为1时,开关s2断开,第一差分通路不工作。

13.进一步地,所述输入缓冲单元具有低通特性,所述输出缓冲单元用于将信号放大至饱和。

14.本发明提供一种高线性度多比特相位插值器,相比较现有技术,存在以下有益效果:具有高线性度和高性能;电路结构简单,移相步进和位数灵活可控;可有效降低系统的相位噪声和抖动,增加了serdes通讯系统的抖动容限,有效提升了整体系统的稳定性和数据传输效率。

附图说明

15.图1为高线性度多比特相位插值器的结构框图;图2为一类夹角产生器的结构框图;图3为二类夹角产生器的结构框图;图4为一类相位合成单元的电路原理图;图5为二类相位合成单元的电路原理图;图6为6比特高线性度相位插值器仿真实验结果。

实施方式

16.下面结合附图和具体实施例对本发明做进一步解释说明。

17.一种高线性度多比特相位插值器,如图1所示,包括正交相位产生器、一类夹角产生器及二类夹角产生器。以本实施例为例,其中有n-1个一类夹角产生器和n-2个二类夹角产生器。

18.正交相位产生器输入信号为vin_i和vin_q,当相位需要在360

°

范围内移动时,正交相位产生器需要能够输出四种正交相位,为2bit正交相位产生器,即输出的两路信号为0

°

、90

°

、180

°

、270

°

相位信号中的两个相邻相位的正交信号,如0

°

、90

°

;90

°

、180

°

;180

°

、270

°

;270

°

、0

°

四种组合,由最高位2bit信号vc《n:n-1》控制,其比特位和输出相位的对应关

系如表1所示。

19.表1 正交相位产生器比特位和输出相位的对应关系vc《n:n=1》vo_0相位(

°

)vo_1相位(

°

)00090019018010180270112700所述正交相位产生器包括第一输出端和第二输出端,分别输出两路相邻的正交信号,第一输出端连接一类夹角产生器和二类夹角产生器的一输入端,第二输出端连接一类夹角产生器和二类夹角产生器的另一输入端,一类夹角产生器、二类夹角产生器的输出端级联后连接末级夹角产生器,本实施例中一类夹角产生器比二类夹角产生器多出一个,所以末级夹角产生器为一类夹角产生器,也可以选择使用二类夹角产生器,这样二类夹角产生器就比一类夹角产生器多出一个。所述末级夹角产生器输出最终的相位移动信号。因此,整个高线性度多比特相位插值器中所含有的一类夹角产生器与二类夹角产生器的数量相差一个,多出来的一个夹角产生器作为末级夹角产生器。

20.一类夹角产生器根据第一输入信号vin_0及第二输入信号vin_1输出第一输出信号或夹角信号,二类夹角产生器根据第一输入信号vin_0及第二输入信号vin_1输出夹角信号或第二输出信号,所述夹角信号的幅值与第一输出信号、第二输出信号的幅值均相同,所述夹角信号的相位为第一输出信号相位与第二输出信号相位的均值,如第一输出信号相位为0

°

,第二输出信号相位为45

°

,则夹角信号相位为22.5

°

。

21.所述级联指前一级的一类夹角产生器的输出端连接后一级的一类夹角产生器的一输入端和二类夹角产生器的一输入端,前一级的二类夹角产生器的输出端连接后一级的一类夹角产生器的另一输入端和二类夹角产生器的另一输入端。夹角产生器级联的级数可根据精度要求选择合适的级数。甚至在满足精度要求的条件下,可在一级夹角产生器后直接连接末级夹角产生器,不需要级联多级。

22.综上所述,对于第k级的两类夹角产生器,分别产生相位夹角为θ/2的两个矢量信号(其中θ为上一级产生的两个信号的夹角),并作为次级的输入信号,由此类推,可以将相位插值器扩展到多bit,直至连接末级夹角产生器。每一级可将上一级夹角为θ的矢量信号通过成比例的电流镜严格意义上精准地一分为二,并作为次级的输入信号。

23.如图2,一类夹角产生器包括输入缓冲单元、一类相位合成单元及输出缓冲单元,第一输入信号vin_0、第二输入信号vin_1从输入缓冲单元输入,控制信号从一类相位合成单元输入,当控制信号vc《k》为0时,输出缓冲单元输出第一输出信号,当控制信号vc《k》为1时,输出缓冲单元输出夹角信号,其比特位和输出相位的对应关系见表2。

24.表2 一类夹角产生器比特位和输出相位的对应关系vc《k》vout相位(

°

)001θ/2如图3,二类夹角产生器包括输入缓冲单元、二类相位合成单元及输出缓冲单元,第一输入信号vin_0、第二输入信号vin_1从输入缓冲单元输入,控制信号从二类相位合成

单元输入,当控制信号vc《k》为0时,输出缓冲单元输出夹角信号,当控制信号vc《k》为1时,输出缓冲单元输出第二输出信号。其比特位和输出相位的对应关系见表3。

25.表3 二类夹角产生器比特位和输出相位的对应关系vc《k》vout相位(

°

)0θ/21θ所述输入缓冲单元具有低通特性,可将接收到的满摆幅的方波转换成摆幅较小的正弦波。所述输出缓冲单元用于将信号放大至饱和,由满摆幅方波输出。

26.在具体相位合成单元的电路实现上,如图4和图5所示给出一种实现方式,但不排除其他相位合成电路的结构。其中,如图4,一类相位合成单元包括第一差分通路及第二差分通路,第一差分通路与第二差分通路的尾电流大小相同,第一差分通路与第二差分通路相对应的晶体管尺寸也完全相同。第一差分通路的差分输入端输入第一输入信号vin_0+/-,第二差分通路的差分输入端输入第二输入信号vin_1+/-,第一差分通路的差分输出端与第二差分通路的差分输出端相连接,第一差分通路在工作时始终保持导通,第二差分通路包含第一开关s1,控制信号vc《k》=0时,第一开关s1断开,只有第一差分通路正常工作,第二差分通路不工作,因此,此时输出的信号为第一输出信号;控制信号vc《k》=1时,第一开关s1闭合,第一差分通路和第二差分通路同时工作,因此,此时输出夹角信号。

27.如图5,二类相位合成单元包括第一差分通路及第二差分通路,第一差分通路的差分输入端输入第一输入信号vin_0+/-,第二差分通路的差分输入端输入第二输入信号vin_1+/-,第一差分通路的差分输出端与第二差分通路的差分输出端相连接,第二差分通路在工作时始终保持导通,第一差分通路包含第二开关s2,控制信号vc《k》=0时,第二开关s2闭合,第一差分通路和第二差分通路同时工作,因此,此时输出夹角信号;控制信号vc《k》=1时,第二开关s2断开,只有第二差分通路正常工作,第一差分通路不工作,因此,此时输出的信号为第二输出信号。

28.其中,夹角信号的幅值与第一输出信号、第二输出信号的幅值均相同,夹角信号的相位为第一输出信号、第二输出信号相位的均值。

29.以6比特的高线性度相位插值器为例,图6展示了仿真条件下该相位插值器差分非线性(dnl)随控制字(0-63)的变化,有图知dnl最大值为0.25,因此可见本实施例提供的高线性度多比特相位插值器具有良好的线性度。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1