模数转换电路

本发明涉及电路,具体而言,涉及一种模数转换电路。

背景技术:

1、一步多位逐次逼近型模数转换器(multi-bit/cycle successive approximationregister analog to digital converter)通过在每个比较周期内量化多位数字码,有效的提升了传统逐次逼近型模数转换器的转换速率。通常一步多位转换电路伴随着多个信号电容阵列协同多个比较器,或一个信号电容阵列同多个参考电容阵列协同多个比较器,用以产生多个参考电压并实现在每个比较周期内的多位比较。

2、对于前者而言,信号电容阵列数量越多,对于输入带宽的衰减越大。对于后者而言,信号电容阵列同参考电容阵列之间通常存在共模电平失调问题,通常需要采用校准技术消除。此外,对于一步m位的方案,通常需要2m-1个电容阵列同2m-1个比较器。虽然m越大,在每个周期内量化的数字码越多,对于转换速率的提升也就越大。然而,考虑到呈指数增长的硬件开销,电路功耗,时序复杂度以及芯片面积的开销,通常传统的解决方案更适合一步两位或一步三位的设计。在相关技术中,传统一步多位逐次逼近型模数转换器只能有限的提升转换速率。因此,逐次逼近型模数转换器在中等分辨率高速场合的应用依然受到较大限制。

技术实现思路

1、本发明的目的在于,针对上述现有技术中的不足,提供一种模数转换电路,以便提升模数转换速率。

2、为实现上述目的,本技术实施例采用的技术方案如下:

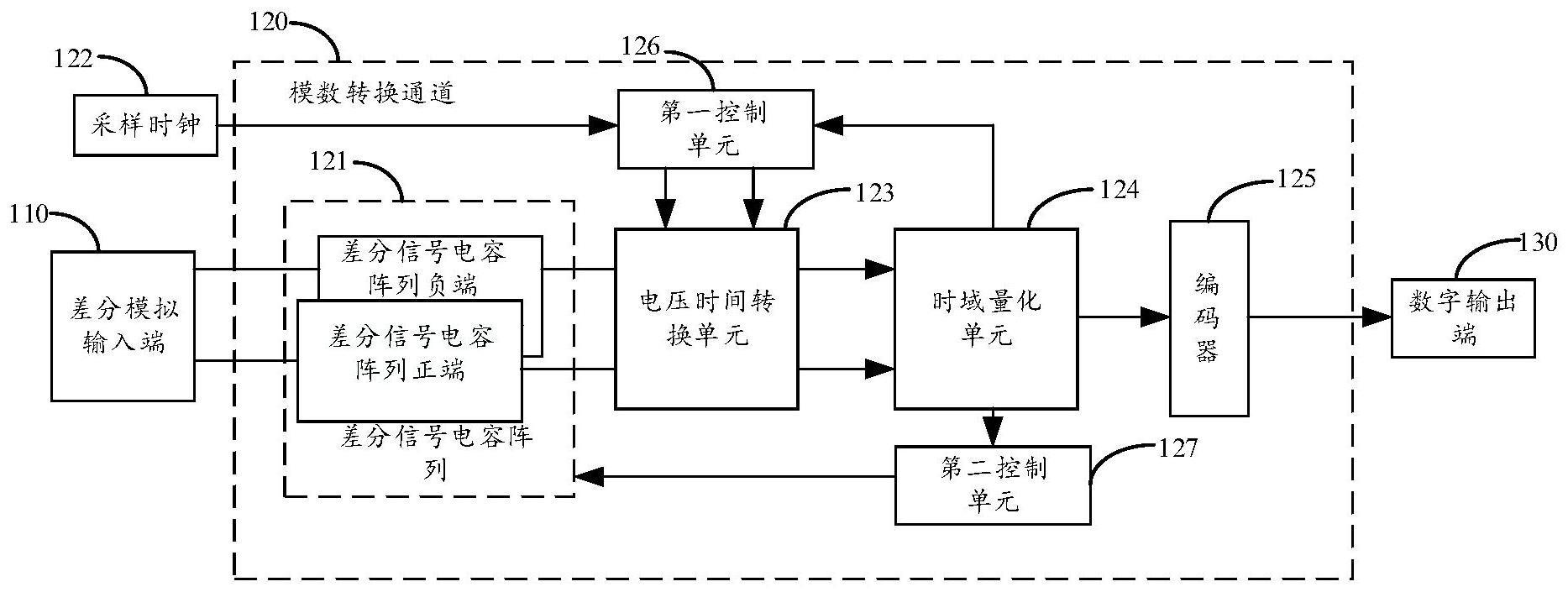

3、本技术实施例提供了一种模数转换电路,包括:差分模拟输入端、模数转换通道以及数字输出端,其中,所述模数转换通道包括:差分信号电容阵列、采样时钟、电压时间转换单元、时域量化单元、编码器、第一控制单元以及第二控制单元;

4、差分模拟输入正端连接差分信号电容阵列正端的输入端,差分模拟输入负端连接差分信号电容阵列负端的输入端,所述差分信号电容阵列的输出端均连接所述电压时间转换单元的输入端;所述电压时间转换单元的输出端连接所述时域量化单元的输入端,所述时域量化单元的输出端连接所述编码器,所述编码器还连接所述数字输出端;所述时域量化单元的输出端还连接所述第二控制单元,所述第二控制单元还连接所述差分信号电容阵列的控制端;

5、其中,所述采样时钟、所述电压时间转换单元的输出端还连接所述第一控制单元,所述第一控制单元还连接所述电压时间转换单元的控制端、所述时域量化单元的控制端、以及所述第二控制单元。

6、在可选的实施方式中,所述差分信号电容阵列正端包括:两个第一电容开关组,其中,所述两个第一电容开关组的一端相连,并作为所述差分信号电容阵列正端的输入端和输出端;

7、所述两个第一电容开关组的另一端还连接预设参考电压端,所述两个第一电容开关组的另一端还接地;当一个第一电容开关组的另一端与所述预设参考电压端连通时,另一个第一电容开关组的另一端与地连通;

8、所述差分信号电容阵列负端包括:两个第二电容开关组,其中,所述两个第二电容开关组的一端相连,并作为所述差分信号电容阵列负端的输入端和输出端;

9、所述两个第二电容开关组的另一端还连接所述预设参考电压端,所述两个第二电容开关组的另一端还接地;当一个第二电容开关组的另一端与所述预设参考电压端连通时,另一个第二电容开关组的另一端与地连通。

10、在可选的实施方式中,所述电压时间转换单元包括:跨导器、积分转换器以及两个阈值交叉检测器,所述跨导器的输入端为所述电压时间转换单元的输入端,用以接收差分电压输入信号;

11、所述跨导器的输出端连接所述积分转换器的输入端,所述积分转换器的输出端连接所述两个阈值交叉检测器的输入端,所述两个阈值交叉检测器的输出端为所述电压时间转换单元的输出端,以输出正负时域信号。

12、在可选的实施方式中,所述积分转换器包括:两个放电支路以及两个可调配负载电容阵列,其中,所述两个放电支路的输入端为所述积分转换器的输入端,所述两个放电支路的输出端为所述积分转换器的输出端,所述两个放电支路的输出端还分别通过所述两个可调配负载电容阵列接地。

13、在可选的实施方式中,每个可调配负载电容阵列包括两级电容阵列,每级电容阵列包括:负载电容,以及可调电容阵列组,所述第一负载电容和所述可调电容阵列组并联在一个放电支路的输出端和地之间,并且,所述可调电容阵列组的控制端连接第一控制单元。

14、在可选的实施方式中,所述电压时间转换单元还包括:延迟缓冲器、与非门以及两个或非门;所述延迟缓冲器的输入端连接所述第一控制单元,所述延迟缓冲器的输出端和所述第一控制单元分别连接所述与非门的输入端,所述与非门的输出连接所述两个阈值交叉检测器的第一控制端;

15、每个阈值交叉检测器的输出端和所述第一控制单元分别连接一个或非门的输入端,所述两个或非门的输出端还分别连接所述两个阈值交叉检测器的第二控制端。

16、在可选的实施方式中,所述时域量化单元包括:时间比较器、两个时间数字转换器、复位逻辑单元;其中,所述时间比较器的正相输入端连接所述电压时间转换单元的正输出端,所述时间比较器的反相输入端连接所述电压时间转换单元的负输出端;

17、所述两个时间数字转换器的输入端分别连接所述电压时间转换单元的正负输出端;所述时间比较器的输出端还通过所述复位逻辑单元连接所述两个时间数字转换器的控制端,所述复位逻辑单元还连接所述第一控制单元;

18、所述时间比较器的输出端、所述两个时间数字转换器的输出端均连接所述编码器和所述第二控制单元。

19、在可选的实施方式中,每个时间数字转换器包括:动态延时器组、时间内插器组以及时间比较器组;其中,所述动态延时器组的输入端连接所述电压时间转换单元的一个输出端,所述动态延时器组的输出端通过所述时间内插器组连接所述时间比较器组的正相输入端;所述动态延时器组的控制端连接所述复位逻辑单元,所述时间比较器组的反相输入端连接所述电压时间转换单元的另一个输出端;所述时间比较器组的输出端为所述每个时间数字转换器的输出端。

20、在可选的实施方式中,所述模数转换通道还包括:数字对齐寄存器,所述编码器通过所述数字对齐寄存器连接所述数字输出端。

21、在可选的实施方式中,若所述模数转换通道的数量为多个,则所述模数转换电路还包括:多路选择器,多个所述模数转换通道中的编码器通过所述多路选择器连接所述数字输出端。

22、本技术的有益效果是:

23、本技术实施例提供一种模数转换电路,包括:差分模拟输入端、模数转换通道以及数字输出端,其中,模数转换通道包括:差分信号电容阵列、采样时钟、电压时间转换单元、时域量化单元、编码器、第一控制单元以及第二控制单元;差分模拟输入正端连接差分信号电容阵列正端的输入端,差分模拟输入负端连接差分信号电容阵列负端的输入端,差分信号电容阵列的输出端均连接电压时间转换单元的输入端;电压时间转换单元的输出端连接时域量化单元的输入端,时域量化单元的输出端连接编码器,编码器还连接数字输出端;时域量化单元的输出端还连接第二控制单元,第二控制单元还连接差分信号电容阵列的控制端;采样时钟、电压时间转换单元的输出端还连接第一控制单元,第一控制单元还连接电压时间转换单元的控制端、时域量化单元的控制端、以及第二控制单元。本技术的电路,通过时域量化单元获得固定的参考时间,将时间信号与参考时间进行比较得到数字信号,并且本技术的电路只采用一个差分信号电容阵列,从而可有效提升模数转换电路的输入带宽。

- 还没有人留言评论。精彩留言会获得点赞!