基于片上纳米颗粒结构的自组装单分子层集成芯片

本发明涉及集成芯片领域,具体指有基于片上纳米颗粒结构的自组装单分子层集成芯片。

背景技术:

1、然而随着晶体管集成度的提高,芯片的制程开始进入量子领域,短沟道效应和热载流子注入等问题成为了目前制程进一步缩小的难题。分子电子学的发展目标是以分子为基本单元,通过分子工程的方式构筑分子尺度的功能电子器件以替代硅基半导体器件,从而克服传统半导体技术的尺度限制,是未来电子器件小型化的一个极具潜力的发展方向,随着分子电子学的发展,如分子二极管,分子晶体管,分子开关等诸多功能分子器件被报道,展现出了分子器件的巨大潜力。

2、在分子电子学的研究中,自组装单分子层(self-assembled monolayer,sam)因其高度有序的结构以及较强的稳定性,成为构建分子器件的一个重要研究技术。sam的形成原理是气体或者溶液中的有机分子在金属及其氧化物的表面上,自发有序地通过化学键、范德华力、静电力等作用力,形成热力学稳定、排布有序的一种具有分子尺度的微纳结构。

3、而目前国内外对分子层的研究、分子层器件的构筑主流的应用技术方案有三种:交叉金属线技术、金属沉积法及液态镓铟合金(eutectic gallium-indium,egain)作为sam顶电极。金属原子比较容易沉积到单分子层中的缺陷位置,容易造成整个单分子层器件的短路。液态镓铟合金(eutectic gallium-indium,egain)作为sam顶电极构筑分子层器件,主要有以下优点:(1)液态镓铟合金接触电阻低,不具有毒性和挥发性,对人体无任何的损害;(2)液态镓铟合金表面具有天然的氧化层,具有较强的机械稳定性,有助于控制顶电极与单分子层的接触面积;(3)液态镓铟合金不易与金属基底反应形成合金,能减小单分子层器件在测试过程中出现的短路现象。

4、目前基于镓铟合金作为sam顶电极的技术方案主要有两种,一种是通过采用紫外光固化胶对egain微型电极、sam和底电极形成的分子结进行支撑。第二种是在pdms材料上通过微纳加工技术制备出微米级微通道模板,从而制备出一系列电极微通道阵列,用外部作用力将egain灌入微通道中并使其稳定,构建基于sam的隧穿结阵列。然而上述方法由于微通道阻力的原因,从原理角度讲,很难继续推进到具有实际应用意义的纳米级,且egain本身不透光的特性,使分子层器件在极有潜力的光电领域大受局限。因此目前存在分子层器件制备良率低、器件之间差异性大等问题。

5、针对上述的现有技术存在的问题设计基于片上纳米颗粒结构的自组装单分子层集成芯片是本发明研究的目的。

技术实现思路

1、针对上述现有技术存在的问题,本发明在于提供基于片上纳米颗粒结构的自组装单分子层集成芯片,能够有效解决上述现有技术存在的至少一个问题。

2、本发明的技术方案是:

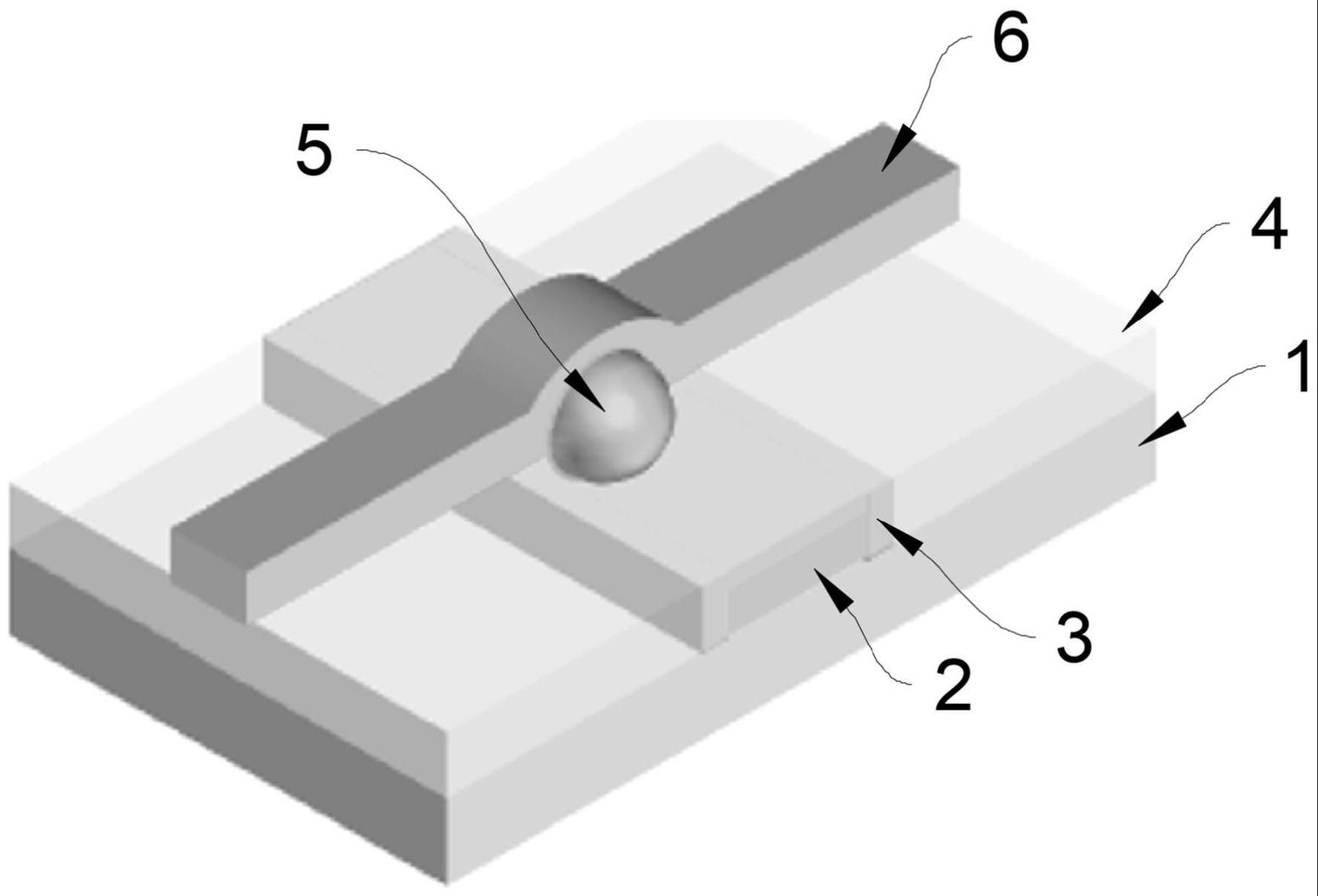

3、基于片上纳米颗粒结构的自组装单分子层集成芯片,包括硅基底、二氧化硅绝缘层、有机玻璃层、底电极、分子层、纳米粒子、顶电极;

4、所述硅基底表面生长有二氧化硅绝缘层,所述二氧化硅绝缘层上铺设有所述有机玻璃层;所述底电极设置于所述有机玻璃层内且与所述二氧化硅绝缘层接触;所述分子层设置于所述底电极和所述有机玻璃层之间;所述纳米粒子的下部分穿过所述有机玻璃层后与所述分子层接触,所述纳米粒子的上部分暴露于所述有机玻璃层外;所述顶电极设置于所述有机玻璃层的上表面且与所述纳米粒子的上部分接触。

5、进一步地,所述底电极作为自组装单分子层集成芯片的漏极,所述顶电极作为自组装单分子层集成芯片的源极,所述分子层作为自组装单分子层集成芯片的介电层。

6、进一步地,所述分子层含具有破坏性量子干涉效应的分子。

7、进一步地,通过改变所述源极和所述漏极之间的电位差,使所述的导电方式切换为分子辅助隧穿或电子直接隧穿,从而改变自组装单分子层集成芯片的电导,进而控制所述源极和所述漏极之间导通或断开。

8、进一步地,所述自组装单分子层集成芯片通过以下方法制得:

9、将氧化硅片洗净、烘干,作为覆盖有二氧化硅绝缘层的硅基底;

10、在所述二氧化硅绝缘层的上表面旋涂光刻胶并烘干;

11、对所述光刻胶进行掩膜光刻、显影,从而在所述光刻胶显影出与第一掩膜模版相对应的底电极图案;

12、采用电子束蒸镀在所述二氧化硅绝缘层上表面对应所述底电极图案的区域生长铬层,然后,采用电子束蒸镀在铬层的上表面生长金薄膜,洗去光刻胶,得到与所述底电极图案相对应的底电极;

13、将带有所述底电极的所述硅基底浸入含具有破坏性量子干涉效应的分子溶液中,使所述底电极的外表面自组装所述分子层;

14、将金纳米粒子溶液滴加在所述分子层,使所述分子层的外表面沉积金纳米粒子;

15、在所述硅基底的上表面涂覆pmma,使pmma覆盖所述金纳米粒子,刻蚀pmma使所述金纳米粒子的上部分暴露,制得所述有机玻璃层;

16、在所述有机玻璃层的上表面通过第二掩膜模版进行覆盖,所述第二掩膜模版设置有顶电极图案,采用电子束蒸镀在所述有机玻璃层的上表面生长金薄膜,得到所述顶电极。

17、进一步地,底电极图案包含器件区域,所述器件区域为交错且间隙设置的平行线形状,所述顶电极图案为穿过对应所述器件区域的上方的横线形状。

18、进一步地,使所述分子层的外表面沉积金纳米粒子包括:

19、使具有破坏性量子干涉效应的分子和金纳米粒子以共价键的方式结合。

20、进一步地,在所述硅基底的上表面涂覆pmma,使pmma覆盖所述金纳米粒子包括:定义硅基底到纳米粒子顶端的垂直距离为d,在所述硅基底的上表面涂覆厚度为d+50nm的pmma;

21、所述刻蚀pmma使所述金纳米粒子的上部分暴露包括:刻蚀100nm厚度的pmma使所述金纳米粒子的上部分暴露。

22、进一步地,所述自组装单分子层集成芯片的使用方法包括:

23、将所述顶电极接地,在所述底电极施加连续变化的电极电位,获取所述分子层器件的电导变化,得到连续变化的电极电位下的电导转折点,以电导转折点对应的电压为所述自组装单分子层集成芯片的阈值电压;

24、当对所述底电极施加阈值电压及以上电压时,使所述顶电极和所述底电极之间导通;

25、当对所述底电极施加阈值电压以下电压时,使所述顶电极和所述底电极之间断开。

26、因此,本发明提供以下的效果和/或优点:

27、本器件通过pmma对分子层封装保护以及纳米颗粒与底层的sam层极小的接触面积,大大减小了传统金属沉积法中顶电极覆盖时,由于高温等因素对分子层造成的损伤,减小了器件短路率,同时大大提高了器件的稳定性。本器件相对于目前主流egain器件的技术方案,集成度提高达到微米级。且在本方案的技术基础上,通过进一步对基板进行特异性图案化,可以使集成度提高至百纳米级,达到现在主流器件的应用要求。

28、本器件的顶电极透光,相比于egain不透光的特性,光电领域应用范围更广;同时器件本身的金纳米粒子与底部金电极构成的光学纳腔,具有限域效应,对场增强可达八个数量级以上。

29、本方法对不同的基底、电极材料均具有较好的适应性和可更换性,应用范围更广,可以适用于研究各种异质材料的特殊性能。

30、应当明白,本发明的上文的概述和下面的详细说明是示例性和解释性的,并且意在提供对如要求保护的本发明的进一步的解释。

- 还没有人留言评论。精彩留言会获得点赞!