一种用于时域交织型模数转换器的时间偏斜误差检测方法与流程

本发明涉及模数转换器时间偏斜误差检测,特别是一种用于时域交织型模数转换器的时间偏斜误差检测方法。

背景技术:

1、传统时间偏斜误差检测方法,基本思路是给模数转换器(adc)输入一个幅度频率已知的模拟信号,得到adc的数字输出,通过对比adc实际数字输出和已知模拟输入信号之间的差异,得到时间偏斜误差信息,因此需要设计专用信号产生电路,比如斜坡信号发生器,正弦信号发生器等,亦或是需要在芯片外部人为加入特殊信号。

2、首先,专用信号产生电路本身设计就具有一定的复杂度;且因为在时域交织型adc中,时间偏斜误差对adc的影响与输入信号的频率正相关,为了得到误差信息,往往需要专用信号具有较高的频率;另外,专用信号产生电路除了在adc上电时校准一次,其余时间都处于关闭状态平白浪费了诸多面积。

技术实现思路

1、发明目的:为了克服现有技术中存在的不足,本发明提供一种用于时域交织型模数转换器的时间偏斜误差检测方法,通过将工作时钟输入时域交织的子adc中,通过子adc的量化结果来得到时间偏斜误差信息,达到降低设计难度和节省芯片面积的效果。

2、技术方案:为实现上述目的,本发明的一种用于时域交织型模数转换器的时间偏斜误差检测方法,通过时间偏斜误差检测电路实现对时域交织型模数转换器的时间偏斜误差进行检测:将工作时钟输入时域交织的子adc中,通过子adc的量化结果来得到时间偏斜误差信息,其中,所述时间偏斜误差检测电路主要由开关sw_m、sw_cal以及多个子adc组成,多个所述子adc包括子模数转换器sub0~subn,所述子模数转换器sub0~subn并联设置;

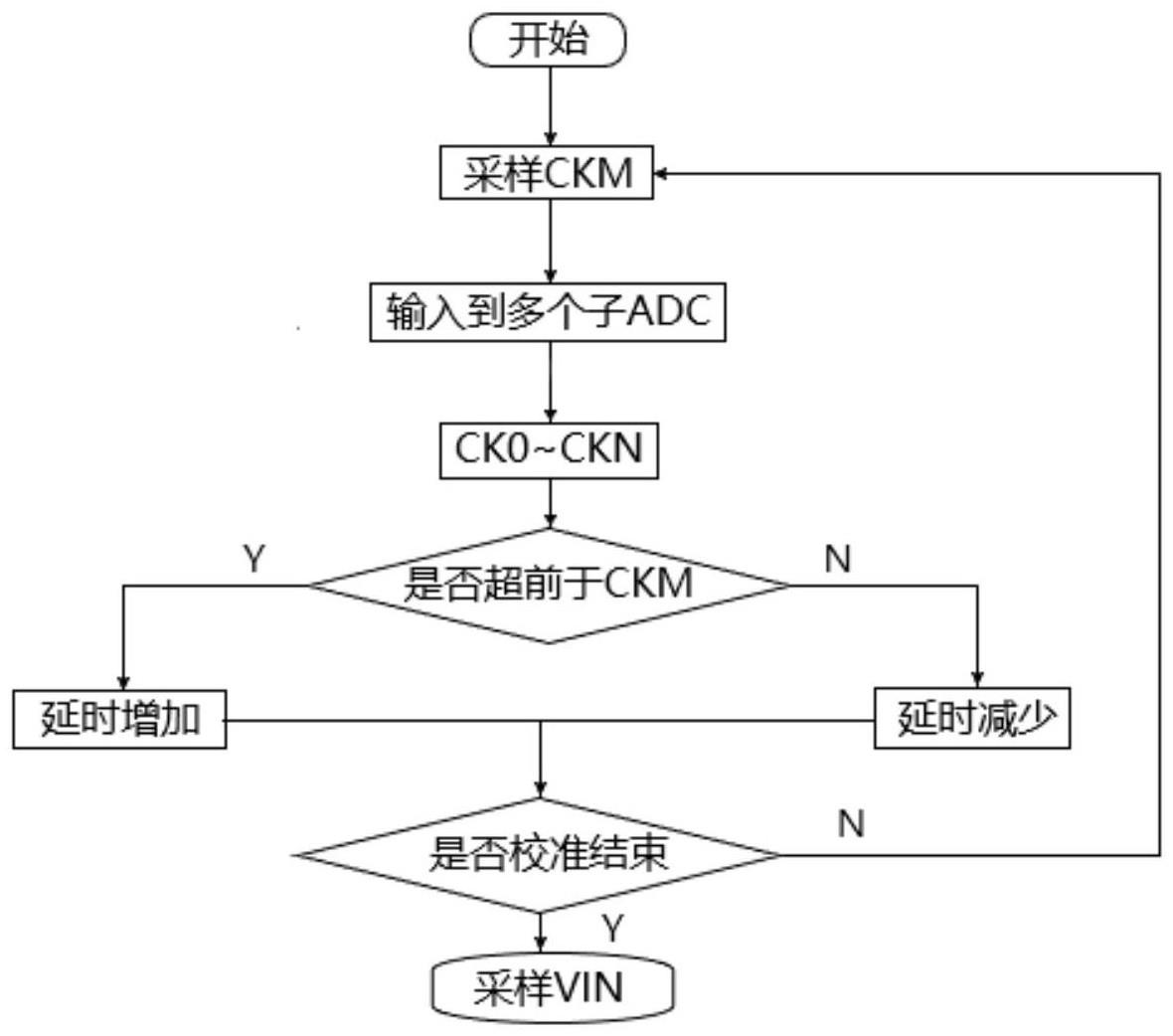

3、时间偏斜误差具体检测步骤如下:

4、步骤ⅰ,在检测过程中,开关sw_m关断,开关sw_cal闭合,此时所有的子adc的输入信号为主采样时钟ckm;

5、步骤ⅱ,所有子adc内部的采样开关sw_sub0~sw_subn在各自的采样时钟ck0~ckn控制下依次对ckm进行采样;

6、步骤ⅲ,在检测结束后,开关sw_cal关断,开关sw_m闭合,所有子adc对输入信号进行采样。

7、进一步地,当所述子adc的数字输出结果为0,则说明所述子adc的采样时刻滞后于所述主采样时钟ckm。

8、进一步地,当所述子adc的数字输出结果为1,则说明所述子adc的采样时刻超前于所述主采样时钟ckm。

9、进一步地,当所述子adc的采样时钟ck0~ckn超前于所述主采样时钟ckm,则将ck0~ckn的延时增加;当所述子adc的采样时钟ck0~ckn滞后于所述主采样时钟ckm,则将ck0~ckn的延时减少。

10、进一步地,通过延时增减电路来调整时钟延时。

11、有益效果:本发明的一种用于时域交织型模数转换器的时间偏斜误差检测方法,至少包括以下优点:不需要额外的专用信号产生电路,且实现方式较为简单,不仅降低了设计的复杂度,同时还节省了芯片的面积。

技术特征:

1.一种用于时域交织型模数转换器的时间偏斜误差检测方法,其特征在于,通过时间偏斜误差检测电路实现对时域交织型模数转换器的时间偏斜误差进行检测:将工作时钟输入时域交织的子adc中,通过子adc的量化结果来得到时间偏斜误差信息,其中,所述时间偏斜误差检测电路主要由开关sw_m、sw_cal以及多个子adc组成,多个所述子adc包括子模数转换器sub0~subn,所述子模数转换器sub0~subn并联设置;

2.根据权利要求1所述的一种用于时域交织型模数转换器的时间偏斜误差检测方法,其特征在于:当所述子adc的数字输出结果为0,则说明所述子adc的采样时刻滞后于所述主采样时钟ckm。

3.根据权利要求2所述的一种用于时域交织型模数转换器的时间偏斜误差检测方法,其特征在于:当所述子adc的数字输出结果为1,则说明所述子adc的采样时刻超前于所述主采样时钟ckm。

4.根据权利要求3所述的一种用于时域交织型模数转换器的时间偏斜误差检测方法,其特征在于:当所述子adc的采样时钟ck0~ckn超前于所述主采样时钟ckm,则将ck0~ckn的延时增加;当所述子adc的采样时钟ck0~ckn滞后于所述主采样时钟ckm,则将ck0~ckn的延时减少。

5.根据权利要求4所述的一种用于时域交织型模数转换器的时间偏斜误差检测方法,其特征在于:通过延时增减电路来调整时钟延时。

技术总结

本发明公开了一种用于时域交织型模数转换器的时间偏斜误差检测方法,通过时间偏斜误差检测电路实现对时域交织型模数转换器的时间偏斜误差进行检测:将工作时钟输入时域交织的子ADC中,通过子ADC的量化结果来得到时间偏斜误差信息,其中,所述时间偏斜误差检测电路主要由开关SW_M、SW_CAL以及多个子ADC组成,多个所述子ADC包括子模数转换器SUB0~SUBN,所述子模数转换器SUB0~SUBN并联设置。本发明不需要额外的专用信号产生电路,且实现方式较为简单,不仅降低了设计的复杂度,同时还节省了芯片的面积。

技术研发人员:胡伟波,石方敏,燕翔,崔海涛,马伟,秦可凡

受保护的技术使用者:江苏谷泰微电子有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!