时钟占空比调整电路及其方法与流程

本公开涉及集成电路,更具体地,涉及一种时钟占空比调整电路及其方法。

背景技术:

1、分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。常见的分频器为二分频、三分频或五分频等。一般地,单端二分频的输出信号的时钟占空比为50%,单端三分频的输出信号的时钟占空比为33.33%或66.67%,单端五分频的输出信号的时钟占空比为40%或60%。

2、在实际应用场景中,50%的时钟占空比的时钟信号对于数据处理最有利,可以保证系统稳定工作。然而,为了得到50%的时钟占空比的时钟信号,往往需要时钟占空比调整电路(duty cycle correction circuit)来调整时钟信号的占空比。

3、相关技术中,时钟占空比调整电路输出的输出信号的时钟占空比往往存在调整精度偏低的技术问题。

技术实现思路

1、本公开提出了一种时钟占空比调整电路及其方法。

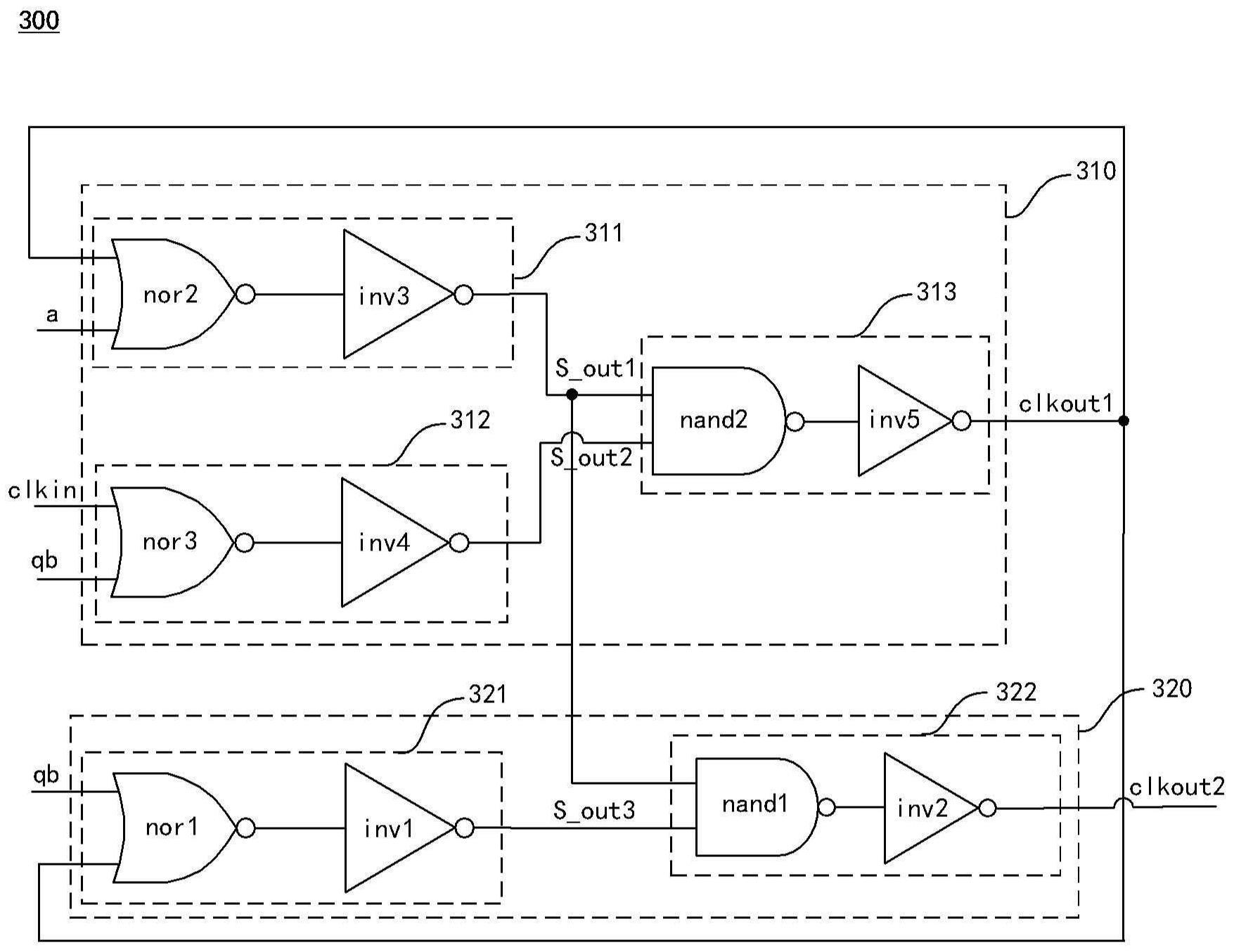

2、根据本公开的第一方面,提出了一种时钟占空比调整电路,包括第一调整子电路,配置为获取第一待调整时钟信号、第二待调整时钟信号和时钟输入信号,并基于时钟输入信号,对第一待调整时钟信号和第二待调整时钟信号进行逻辑运算处理,得到第一输出时钟信号;其中,第一待调整时钟信号和第二待调整时钟信号为来自三分频的输出信号或五分频的输出信号;以及第二调整子电路,配置为对第一输出时钟信号、第二待调整时钟信号和第一调整子电路的第一输出信号进行逻辑运算处理,得到第二输出时钟信号;其中,第二输出时钟信号为50%占空比的时钟信号。

3、例如,第二调整子电路包括第一或门单元,配置为对第一输出时钟信号和第二待调整时钟信号进行或逻辑运算,得到第三输出信号;以及第一与逻辑单元,配置为对第一输出信号和第三输出信号进行逻辑与运算,得到第二输出时钟信号。

4、例如,第二调整子电路包括第一或门单元,配置为对第一输出时钟信号和第二待调整时钟信号进行或逻辑运算,得到第三输出信号;第二与逻辑单元,配置为对第一输出信号、第三输出信号和第二输出时钟信号进行逻辑与运算,得到第四输出信号;以及

5、第二或门单元,配置为对第四输出信号和第一输出时钟信号进行或逻辑运算,得到第二输出时钟信号。

6、例如,第一或门单元包括第一或非门,第一或非门的第一输入端与第二待调整时钟信号的输出端电连接,第一或非门的第二输入端与第一输出时钟信号的输出端电连接;以及第一反相器,第一反相器的输入端与第一或非门的输出端电连接,第一反相器的输出端与第一与逻辑单元的输入端电连接。

7、例如,第一与逻辑单元包括第一与非门,第一与非门的第一输入端与第一反相器的输出端电连接,第一与非门的第二输入端与第一输出信号的输出端电连接;以及第二反相器,第二反相器的输入端与第一与非门的输出端电连接,第二反相器的输出端为第二输出时钟信号的输出端。

8、例如,第一或门单元包括第一或非门,第一或非门的第一输入端与第二待调整时钟信号的输出端电连接,第一或非门的第二输入端与第一输出时钟信号的输出端电连接;以及第一反相器,第一反相器的输入端与第一或非门的输出端电连接,第一反相器的输出端为第三输出信号的输出端。

9、例如,第二与逻辑单元包括第一与非门,第一与非门的第一输入端与第一反相器的输出端电连接,第一与非门的第二输入端与第一输出信号的输出端电连接,第一与非门的第三输入端与第二输出时钟信号的输出端连接;以及第二反相器,第二反相器的输入端与第一与非门的输出端电连接,第二反相器的输出端为第四输出信号的输出端。

10、例如,第二或门单元包括第二或非门,第二或非门的第一输入端与第二反相器的输出端电连接,第二或非门的第二输入端与第一输出时钟信号的输出端电连接;以及第三反相器,第三反相器的输入端与第二或非门的输出端电连接,第三反相器的输出端为第二输出时钟信号的输出端。

11、例如,第一调整子电路包括第三或门单元,配置为对第一输出时钟信号和第一待调整时钟信号进行或逻辑运算,得到第一输出信号;第四或门单元,配置为对时钟输入信号和第二待调整时钟信号进行或逻辑运算,得到第二输出信号;以及第三与逻辑单元,配置为对第一输出信号和第二输出信号进行逻辑与运算,得到第一输出时钟信号。

12、根据本公开实施例的第二方面,提供了一种时钟占空比调整方法,该方法适用于如本公开第一个方面提供的时钟占空比调整电路,包括获取第一待调整时钟信号、第二待调整时钟信号和时钟输入信号;其中,第一待调整时钟信号和第二待调整时钟信号为来自三分频的输出信号或五分频的输出信号;基于时钟输入信号,对第一待调整时钟信号和第二待调整时钟信号进行逻辑运算处理,得到第一输出时钟信号;以及对第一输出时钟信号、第二待调整时钟信号和第一调整子电路的第一输出信号进行逻辑运算处理,得到第二输出时钟信号;其中,二输出时钟信号为50%占空比的时钟信号。

13、根据公开实施例的技术方案,提供了一种时钟占空比调整电路。该时钟占空比调整电路通过将第一调整子电路输出的第一输出时钟信号反馈至第二调整子电路中进行信号调整,以解决由于存在信号延迟问题导致的第一输出时钟信号的时钟占空比偏离50%的问题,最终得到时钟占空比为50%的第二输出时钟信号。该电路适用于三分频和五分频,使得三分频和五分频能够输出精度较高的50%占空比的时钟信号。

技术特征:

1.一种时钟占空比调整电路,包括:

2.根据权利要求1所述的时钟占空比调整电路,其中,所述第二调整子电路包括:

3.根据权利要求1所述的时钟占空比调整电路,其中,所述第二调整子电路包括:

4.根据权利要求2所述的时钟占空比调整电路,其中,所述第一或门单元包括:

5.根据权利要求4所述的时钟占空比调整电路,其中,所述第一与逻辑单元包括:

6.根据权利要求3所述的时钟占空比调整电路,其中,所述第一或门单元包括:

7.根据权利要求6所述的时钟占空比调整电路,其中,所述第二与逻辑单元包括:

8.根据权利要求7所述的时钟占空比调整电路,其中,所述第二或门单元包括:

9.根据权利要求2所述的时钟占空比调整电路,其中,所述第一调整子电路包括:

10.一种时钟占空比调整方法,该方法适用于如权利要求1~9中任一项所述的时钟占空比调整电路,包括:

技术总结

本公开提供了一种时钟占空比调整电路及其方法,该时钟占空比调整电路包括第一调整子电路,配置为获取第一待调整时钟信号、第二待调整时钟信号和时钟输入信号,并基于时钟输入信号,对第一待调整时钟信号和第二待调整时钟信号进行逻辑运算处理,得到第一输出时钟信号;其中,第一待调整时钟信号和第二待调整时钟信号为来自三分频的输出信号或五分频的输出信号;以及第二调整子电路,配置为对第一输出时钟信号、第二待调整时钟信号和第一调整子电路的第一输出信号进行逻辑运算处理,得到第二输出时钟信号;其中,第二输出时钟信号为50%占空比的时钟信号。

技术研发人员:张玲,李超,张任伟

受保护的技术使用者:南京奕斯伟计算技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!