一种高均一性浮栅结构铁电隧穿结存储器及制备方法

本发明属于半导体,特别涉及一种高均一性浮栅结构铁电隧穿结存储器及制备方法。

背景技术:

1、为推动集成电路的发展,要求存储器单元信息存储密度提升。然而通过缩小器件尺寸这种最易提高密度的方法由于可靠性等问题突出而逐渐失效。铁电隧穿结(ftj)具有结构简单、可靠性高和功耗低等特点,有望替代传统存储存储单元,实现高密度存储器。另外由于chatgpt等(ai)的发展,构建类神经网络的智能芯片有助于推动ai的进步。ftj具有与神经突触相似的结构和特性,是构建智能芯片的理想突触单元之一。

2、ftj依靠铁电材料的极化特性以及上下电极的屏蔽长度差异性,实现存储功能。目前,ftj器件已经从金属-铁电-金属(mfm)结构发展到金属-铁电-介质-半导体(mfis)结构。通过扩大势垒层的调整幅度以及隧穿宽度实现更高的开关电流比(ter)。更大的ter可以使ftj器件具有更大的存储窗口,实现多态存储。

3、虽然现有的ftj器件结构丰富且具有多态存储能力,但是基于现有工艺制造的铁电层薄膜均为多晶形态,其使薄膜质量的均一性较差[dynamics of multi-domains inferroelectric tunnel junction]。由于铁电层对器件具有重要的影响,导致相同参数指标下的器件性能存在较大的差异。这将引起ftj器件构建的存储器以及智能计算芯片的可靠性存在严重问题。例如相同的开启脉冲下,相邻位置上的器件可能表现出不同的阻抗特性,这将使得采用ftj器件构建的存储器件产生信息差异,从而引起数据存储错误。同时均一性较差的ftj使得类神经网络芯片的训练准确性降低。以上导致现有的器件远不能满足存储器、类神经网络和人工智能的ai芯片的要求。

技术实现思路

1、为了克服上述现有技术的缺点,本发明的目的在于提供一种高均一性浮栅结构铁电隧穿结存储器及制备方法,以期解决由于铁电隧穿结铁电层的多畴特性影响引起的铁电隧穿结器件均一性差的问题,实现超高均一性铁电隧穿结。

2、为了实现上述目的,本发明采用的技术方案是:

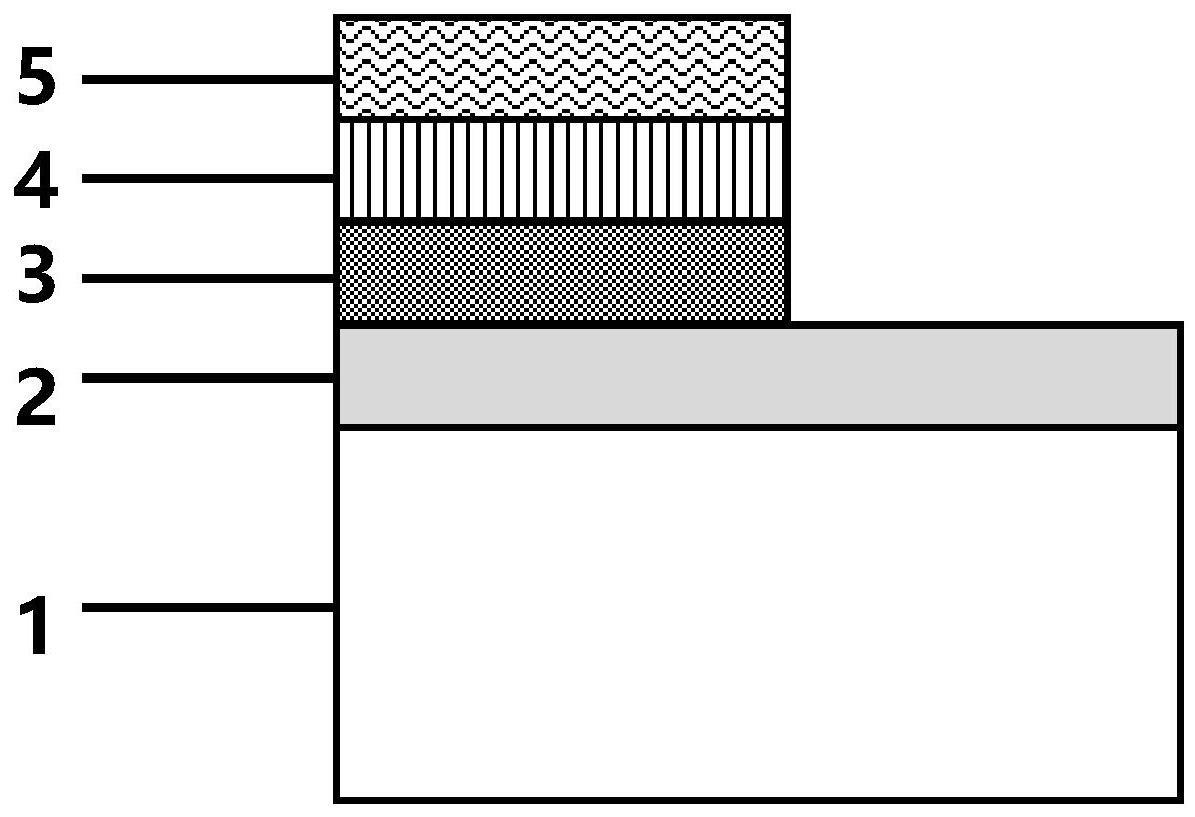

3、一种高均一性浮栅结构铁电隧穿结存储器,包括自下而上依次设置的衬底、底电极层、半导体调控层、铁电层和顶电极层;所述半导体调控层为厚度在纳米量级的重掺半导体层;

4、通过在顶电极层施加正向脉冲,铁电层极化方向指向顶电极层,势垒下降,器件表现开态;施加负向脉冲,铁电层极化方向指向底电极层,势垒增高,器件表现关态。

5、在本发明的一个实施例中,所述半导体调控层为n型掺杂半导体或p型掺杂半导体;其材料为si、ge或gesi。

6、在本发明的一个实施例中,所述半导体调控层的厚度为1~5nm,掺杂浓度1e18~2e19 cm-3,掺杂浓度越重,厚度范围越小。

7、在本发明的一个实施例中,所述底电极层的厚度为10~50nm,铁电层的厚度为1~10nm,顶电极层的厚度为10~100nm。

8、在本发明的一个实施例中,所述衬底的材料为si、ge、sic、gan、蓝宝石及金刚石材料中的任意一种;所述底电极层和顶电极层的材料为金属钨、金属钛、金属铜、金属铝、金属铂、金属铱、金属钌、氮化钨、氮化钛、氮化钽、氧化铱、氧化钌、碳化钨、碳化钛、硅化钨、硅化钛和硅化钽中的任意一种;所述铁电层的材料为hfzro、hfalo、sbt、batio3、cd2nb2o7、bifeo3和znsno3中的任意一种。

9、本发明还提供了所述高均一性浮栅结构铁电隧穿结存储器的制备方法,包括如下步骤:

10、步骤1),在衬底上生长底电极层;

11、步骤2),利用原子层淀积工艺,在底电极层上生长半导体层,再经过扩散反应完成重掺杂,得到半导体调控层;

12、步骤3),利用湿法刻蚀技术,刻蚀半导体调控层上形成的天然氧化层;

13、步骤4),在半导体调控层上淀积铁电层;

14、步骤5),在铁电层上生长顶电极层。

15、在本发明的一个实施例中,所述步骤1),利用反应溅射工艺,在衬底上生长10~50nm的底电极层;所述步骤5),利用磁控溅射工艺,在铁电层上生长10-100nm的顶电极层。

16、在本发明的一个实施例中,所述步骤2),采用si源或ge源,以h2作为还原剂,以n2作为保护气,在500℃~800℃范围内在底电极层上生长1nm~5nm的半导体层,再经过扩散反应,完成n型或p型重掺杂。

17、在本发明的一个实施例中,所述步骤3),采用hf·nh3溶液作为刻蚀反应液,浸泡3~5s后,去除半导体调控层上天然氧化层。

18、在本发明的一个实施例中,所述步骤4),利用原子层淀积工艺,在半导体调控层上方淀积1~10nm的铁电层。

19、在本发明的一个实施例中,所述步骤5),在生长顶电极层之后,利用刻蚀工艺,刻蚀出部分区域的底电极层。

20、与现有技术相比,本发明的有益效果是:

21、1.本发明利用铁电层对半导体能带的调控作用,采用超薄半导体调控层调制,实现了在现有工艺条件下生长的均一性较差的铁电薄膜构成超高均一性的铁电隧穿结。

22、2.本发明在获得超高均一可靠性的同时,由于减小半导体厚度,通过提升铁电层剩余极化强度,提高了铁电剩余极化强度,从而提升铁电隧穿结开关电流比,更有利于发展高能效非冯存算一体架构,有望突破后摩尔时代集成电路产业能效瓶颈。

技术特征:

1.一种高均一性浮栅结构铁电隧穿结存储器,其特征在于,包括自下而上依次设置的衬底(1)、底电极层(2)、半导体调控层(3)、铁电层(4)和顶电极层(5);所述半导体调控层(3)为厚度在纳米量级的重掺半导体层;

2.根据权利要求1所述高均一性浮栅结构铁电隧穿结存储器,其特征在于,所述半导体调控层(3)为n型掺杂半导体或p型掺杂半导体;其材料为si、ge或gesi。

3.根据权利要求1所述高均一性浮栅结构铁电隧穿结存储器,其特征在于,所述半导体调控层(3)的厚度为1~5nm,掺杂浓度1e18~2e19 cm-3,掺杂浓度越重,厚度范围越小。

4.根据权利要求3所述高均一性浮栅结构铁电隧穿结存储器,其特征在于,所述底电极层(2)的厚度为10~50nm,铁电层(4)的厚度为1~10nm,顶电极层(5)的厚度为10~100nm。

5.根据权利要求1或3所述高均一性浮栅结构铁电隧穿结存储器,其特征在于,所述衬底(1)的材料为si、ge、sic、gan、蓝宝石及金刚石材料中的任意一种;所述底电极层(2)和顶电极层(5)的材料为金属钨、金属钛、金属铜、金属铝、金属铂、金属铱、金属钌、氮化钨、氮化钛、氮化钽、氧化铱、氧化钌、碳化钨、碳化钛、硅化钨、硅化钛和硅化钽中的任意一种;所述铁电层(4)的材料为hfzro、hfalo、sbt、batio3、cd2nb2o7、bifeo3和znsno3中的任意一种。

6.权利要求1所述高均一性浮栅结构铁电隧穿结存储器的制备方法,其特征在于,包括如下步骤:

7.根据权利要求6所述的制备方法,其特征在于,所述步骤1),利用反应溅射工艺,在衬底(1)上生长10~50nm的底电极层(2);所述步骤4),利用原子层淀积工艺,在半导体调控层(3)上方淀积1~10nm的铁电层(4);所述步骤5),利用磁控溅射工艺,在铁电层(4)上生长10~100nm的顶电极层(5)。

8.根据权利要求6所述的制备方法,其特征在于,所述步骤2),采用si源或ge源,以h2作为还原剂,以n2作为保护气,在500℃~800℃范围内在底电极层(2)上生长1nm~5nm的半导体层,再经过扩散反应,完成n型或p型重掺杂。

9.根据权利要求6所述的制备方法,其特征在于,所述步骤3),采用hf·nh3溶液作为刻蚀反应液,浸泡3~5s后,去除半导体调控层(3)上天然氧化层。

10.根据权利要求6所述的制备方法,其特征在于,所述步骤5),在生长顶电极层(5)之后,利用刻蚀工艺,刻蚀出部分区域的底电极层(2)。

技术总结

一种高均一性浮栅结构铁电隧穿结存储器,包括自下而上依次设置的衬底、底电极层、半导体调控层、铁电层和顶电极层;所述半导体调控层为厚度在纳米量级的重掺半导体层;通过在顶电极层施加正向脉冲,铁电层极化方向指向顶电极层,势垒下降,器件表现开态;施加负向脉冲,铁电层极化方向指向底电极层,势垒增高,器件表现关态。本发明还提供了其制备方法和应用形式。

技术研发人员:周久人,冯雯静,闫钦元,韩根全

受保护的技术使用者:西安电子科技大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!