半导体结构及其形成方法与流程

本公开实施例涉及半导体,特别涉及一种半导体结构及其形成方法。

背景技术:

1、随着人们对电子产品的要求向小型化、多功能化发展,半导体封装结构也向着高密度、高集成化的方向发展。

2、半导体封装结构可以包括相互键合的芯片,其中,芯片之间的导电走线的分布方式以及芯片的设置不仅对键合工艺的复杂度具有影响,还对半导体封装结构的性能具有一定的影响,目前,半导体封装结构中芯片以及导电走线的设置仍存在不足,如何优化半导体封装结构的性能为现阶段亟需解决的技术问题。

技术实现思路

1、本公开实施例提供一种半导体结构及其形成方法,至少有利于提升半导体结构的性能。

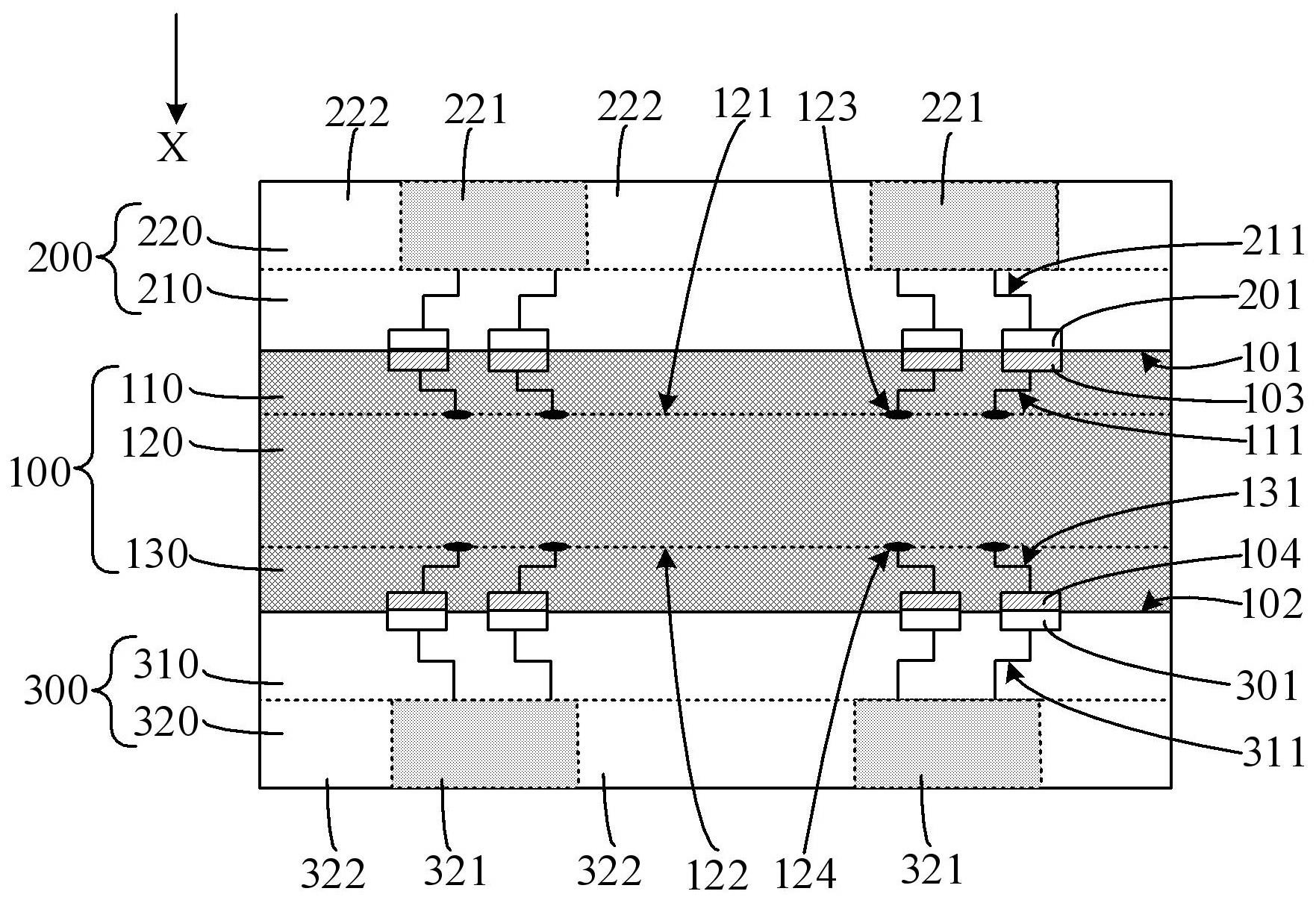

2、本公开实施例一方面提供一种半导体结构,包括:中间器件层,中间器件层具有相对的第一面和第二面,第一面具有第一焊盘,第二面具有第二焊盘,中间器件层包括存储单元阵列,第一焊盘与存储单元阵列的字线电连接,第二焊盘与存储单元阵列的位线电连接;第一器件层,第一器件层位于第一面上,且第一器件层朝向中间器件层的表面具有第三焊盘,第三焊盘与相应的第一焊盘电连接,第一器件层包括字线驱动器,第三焊盘与字线驱动器电连接;第二器件层,第二器件层位于第二面上,且第二器件层朝向中间器件层的表面具有第四焊盘,第四焊盘与相应的第二焊盘电连接,第二器件层包括位线感测放大器,第四焊盘与位线感测放大器电连接。

3、在一些实施例中,半导体结构包括外围电路,外围电路位于第一器件层或第二器件层中的至少一者。

4、在一些实施例中,外围电路包括第一部分和第二部分,第一部分位于第一器件层,第二部分位于第二器件层。

5、在一些实施例中,沿第一面指向第二面的方向上,中间器件层包括依次堆叠的第一重布线层、芯片层以及第二重布线层,存储单元阵列位于芯片层内;第一焊盘位于第一重布线层内,第一重布线层包括第一走线,存储单元阵列的字线通过第一走线与第一焊盘连接;第二焊盘位于第二重布线层内,第二重布线层包括第二走线,存储单元阵列的位线通过第二走线与第二焊盘连接。

6、在一些实施例中,芯片层包括朝向第一面的第一侧以及朝向第二面的第二侧,第一侧具有字线接口,存储单元阵列的字线通过字线接口与第一走线相连接;第二侧具有位线接口,存储单元阵列的位线通过位线接口与第二走线相连接。

7、在一些实施例中,沿第一面指向第二面的方向上,第一器件层包括依次堆叠的第二芯片层以及第三重布线层,字线驱动器位于第二芯片层内;第三焊盘位于第三重布线层内,且第三重布线层包括第三走线,字线驱动器通过第三走线与第三焊盘连接;沿垂直于第一面指向第二面的方向上,第二芯片层包括多个间隔排布的第一区,字线驱动器位于第一区。

8、在一些实施例中,第一器件层包括外围电路,外围电路位于第二芯片层,第二芯片层包括第一区以外的第二区,外围电路位于第二区。

9、在一些实施例中,沿第一面指向第二面的方向上,第二器件层包括依次堆叠的第四重布线层以及第三芯片层,位线感测放大器位于第三芯片层内;第四焊盘位于第四重布线层内,且第四重布线层包括第四走线,位线感测放大器通过第四走线与第四焊盘连接;沿垂直于第一面指向第二面的方向上,第三芯片层包括多个间隔排布的第三区,位线感测放大器位于第三区。

10、在一些实施例中,第二器件层包括外围电路,外围电路位于第三芯片层,第三芯片层包括第三区以外的第四区,外围电路位于第四区。

11、本公开实施例另一方面还提供一种半导体结构的形成方法,包括:提供中间器件层,中间器件层具有相对的第一面和第二面,第一面具有第一焊盘,第二面具有第二焊盘,中间器件层包括存储单元阵列,第一焊盘与存储单元阵列的字线电连接,第二焊盘与存储单元阵列的位线电连接;提供第一器件层,第一器件层的第一表面具有第三焊盘,第一器件层包括字线驱动器,第三焊盘与字线驱动器电连接,将第一器件层的第一表面与第一面相固定,第三焊盘与相应的第一焊盘电连接;提供第二器件层,第二器件层的第一表面具有第四焊盘,第二器件层包括位线感测放大器,第四焊盘与位线感测放大器电连接,将第二器件层的第一表面与第二面相固定,第四焊盘与相应的第二焊盘电连接。

12、本公开实施例提供的技术方案至少具有以下优点:

13、本公开实施例提供的半导体结构包括:承载存储单元阵列的中间器件层、承载字线驱动器的第一器件层以及承载位线感测放大器的第二器件层,相较于在一个器件层中设置字线驱动器以及位线感测放大器,并将包括字线驱动器以及位线感测放大器的器件层设置在中间器件层一侧的方式,本公开实施例提供的半导体结构中,第一器件层以及第二器件层设置在中间器件层的相对的两侧,如此,第一器件层和第二器件层作为与中间器件层相键合的器件层,中间器件层与相键合的器件层之间的导电走线的分布更为分散,不仅有利于缓解器件层之间的导电走线的密度对中间器件层中存储单元密度的限制,还可以缓解相键合的器件层中的电路结构对中间器件层中存储单元密度的限制,有利于提升存储单元阵列中的存储单元的密度。此外,分散分布的导电走线之间的间隔距离更大,不仅有利于降低耦合干扰,还有利于降低器件层之间的键合难度。并且,由于第一器件层以及第二器件层分布在中间器件层两侧,因此,也可以设置更多的导电走线实现中间器件层与第一器件层的电连接,以及可以设置更多的导电走线实现中间器件层与第二器件层的电连接,更多的导电走线有利于降低半导体结构中的导通电阻,进而有利于提升半导体结构的性能。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构包括外围电路,所述外围电路位于所述第一器件层或所述第二器件层中的至少一者。

3.根据权利要求2所述的半导体结构,其特征在于,所述外围电路包括第一部分和第二部分,所述第一部分位于所述第一器件层,所述第二部分位于所述第二器件层。

4.根据权利要求1所述的半导体结构,其特征在于,沿所述第一面指向所述第二面的方向上,所述中间器件层包括依次堆叠的第一重布线层、芯片层以及第二重布线层,所述存储单元阵列位于所述芯片层内;

5.根据权利要求4所述的半导体结构,其特征在于,所述芯片层包括朝向所述第一面的第一侧以及朝向所述第二面的第二侧,所述第一侧具有字线接口,所述存储单元阵列的字线通过所述字线接口与所述第一走线相连接;

6.根据权利要求1所述的半导体结构,其特征在于,沿所述第一面指向所述第二面的方向上,所述第一器件层包括依次堆叠的第二芯片层以及第三重布线层,所述字线驱动器位于所述第二芯片层内;

7.根据权利要求6所述的半导体结构,其特征在于,所述第一器件层包括外围电路,所述外围电路位于所述第二芯片层,所述第二芯片层包括所述第一区以外的第二区,所述外围电路位于所述第二区。

8.根据权利要求1所述的半导体结构,其特征在于,沿所述第一面指向所述第二面的方向上,所述第二器件层包括依次堆叠的第四重布线层以及第三芯片层,所述位线感测放大器位于所述第三芯片层内;

9.根据权利要求8所述的半导体结构,其特征在于,所述第二器件层包括外围电路,所述外围电路位于所述第三芯片层,所述第三芯片层包括所述第三区以外的第四区,所述外围电路位于所述第四区。

10.一种半导体结构的形成方法,其特征在于,包括:提供中间器件层,所述中间器件层具有相对的第一面和第二面,所述第一面具有第一焊盘,所述第二面具有第二焊盘,所述中间器件层包括存储单元阵列,所述第一焊盘与所述存储单元阵列的字线电连接,所述第二焊盘与所述存储单元阵列的位线电连接;

技术总结

本公开实施例提供一种半导体结构及其形成方法,半导体结构包括:中间器件层,中间器件层具有第一面和第二面,第一面具有第一焊盘,第二面具有第二焊盘,中间器件层包括存储单元阵列,第一焊盘与存储单元阵列的字线电连接,第二焊盘与存储单元阵列的位线电连接;第一器件层位于第一面上,且第一器件层的表面具有第三焊盘,第三焊盘与相应的第一焊盘电连接,第一器件层包括字线驱动器,第三焊盘与字线驱动器电连接;第二器件层位于第二面上,且第二器件层的表面具有第四焊盘,第四焊盘与相应的第二焊盘电连接,第二器件层包括位线感测放大器,第四焊盘与位线感测放大器电连接。本公开实施例至少有利于提升半导体结构的性能。

技术研发人员:黄猛

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!