一种D触发器

【】本发明涉及集成电路,具体涉及一种d触发器。

背景技术

0、

背景技术:

1、d触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

2、d触发器(dff)作为标准单元中不可或缺的时序逻辑结构被广泛应用各种设计中。尤其是在高速的逐次逼近型模数转换器(sar adc)中,同步数字电路常被用于实现高速的数字逻辑反馈;这其中最基本的电路模块就是d触发器。通常来说,sar adc利用二分法算法在每个转换周期内的数个循环中不断对采样到的信号进行逼近,以求解出最近似的数字信号。因此在每个转换周期结束时需要对数字逻辑进行复位处理,以便进行下一次的信号转换。

3、现有的d触发器的结构中,要么不具备复位功能;要么采用过多的晶体管和复杂的控制逻辑来实现复位功能。因此现有的具备复位功能的d触发器存在电路布线复杂与控制逻辑复杂的问题。

4、本发明针对现有的具备复位功能的d触发器存在电路布线复杂与控制逻辑复杂的技术问题,对d触发器进行了技术改进。

技术实现思路

0、

技术实现要素:

1、本发明的目的是,提供一种具备复位功能,布线资源节约,版图设计简化,以及控制逻辑简化的d触发器。

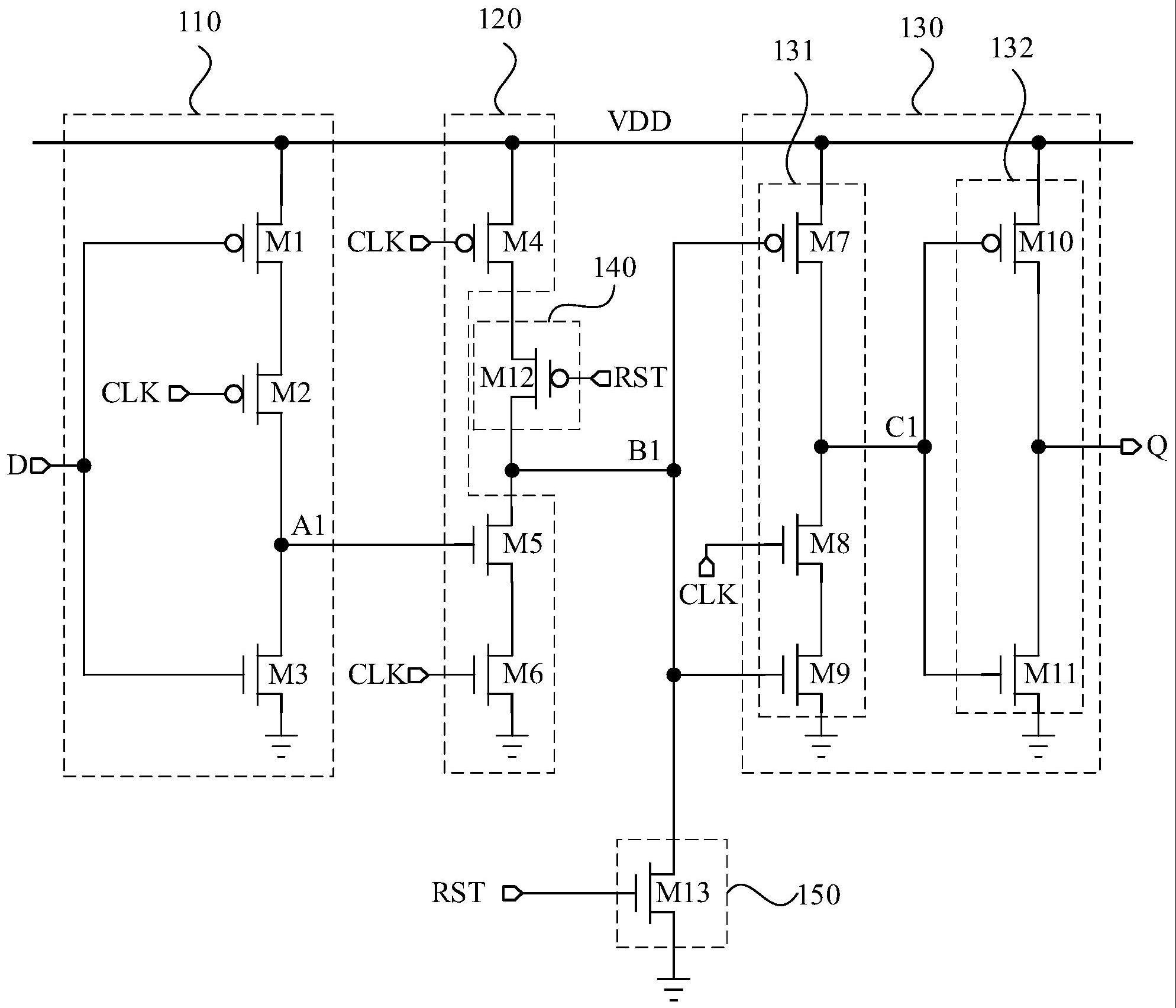

2、为实现上述目的,本发明采取的技术方案是一种d触发器,包括第一输入端、时钟端、复位端、第一输出端、第一输入模块、第一转换模块、第一输出模块、第一复位模块和第二复位模块;

3、所述第一输入模块第一输入端,接入第一输入信号d;所述第一输入模块第二输入端、所述第一转换模块第一输入端和所述第一输出模块第一输入端,接入时钟信号clk;所述第一复位模块第一输入端和所述第二复位模块第一输入端,接入复位信号rst;所述第一输出模块输出端,输出第一输出信号q;所述第一输入模块输出端电连接所述第一转换模块第二输入端,所述第一输入模块、第一转换模块和第一输出模块,在时钟信号clk的控制下完成第一输入信号d的转换,实现所述d触发器第一输出信号q输出;

4、所述第一转换模块第一输出端为第二节点b1;所述第一复位模块第二输入端与所述第一转换模块第二输出端电连接,所述第一复位模块输出端与所述第二节点b1电连接,所述第二复位模块输出端与所述第二节点b1电连接;所述第一输出模块第二输入端与所述第二节点b1电连接;所述第一复位模块、所述第二复位模块在复位信号rst的作用下,配合第一转换模块共同控制第二节点b1的电位,实现所述d触发器第一输出信号q复位。

5、优选地,所述第一输入模块输出端为第一节点a1,所述第一输入模块根据第一输入信号d和时钟信号clk控制所述第一节点a1的电位;所述第一输出模块包括串联的第一输出单元和第二输出单元,所述第一输出单元第一输入端为第一输出模块第一输入端,所述第一输出单元第二输入端为第一输出模块第二输入端,所述第一输出单元输出端为第五节点c1,所述第二输出单元输入端与第五节点c1电连接,所述第二输出单元输出端为第一输出模块输出端。

6、优选地,所述第一输入模块包括第一晶体管m1、第二晶体管m2和第三晶体管m3;所述第一晶体管m1栅极接入第一输入信号d,所述第一晶体管m2第一极接入第一电源信号vdd,所述第二晶体管m2栅极接入时钟信号clk,所述第二晶体管m2第一极与所述第一晶体管m1第二极电连接,所述第三晶体管m3栅极接入第一输入信号d,所述第三晶体管m3第一极与所述第二晶体管m2第二极电连接,并作为第一节点a1,所述第三晶体管m3第二极接入第二电源信号g;其中,所述第一晶体管m1、第二晶体管m2为低电位导通极性,所述第三晶体管m3为高电位导通极性。

7、优选地,所述第一转换模块包括第四晶体管m4、第五晶体管m5和第六晶体管m6;所述第四晶体管m4栅极接入时钟信号clk,所述第四晶体管m4第一极接入第一电源信号vdd,所述第四晶体管m4第二极为所述第一转换模块第二输出端,所述第五晶体管m5栅极与所述第一节点a1电连接,所述第五晶体管m5第一极为所述第二节点b2,所述第六晶体管m6栅极接入时钟信号clk,所述第六晶体管m6第一极与所述第五晶体管m5第二极电连接,所述第六晶体管m6第二极接入所述第二电源信号g;其中,所述第四晶体管m4为低电位导通极性,所述第五晶体管m5、第六晶体管m6为高电位导通极性。

8、优选地,所述第一输出模块包括第七晶体管m7、第八晶体管m8、第九晶体管m9、第十晶体管m10和第十一晶体管m11;所述第七晶体管m7栅极与所述第二节点b2电连接,所述第七晶体管m7第一极接入第一电源信号vdd,所述第八晶体管m8栅极接入时钟信号clk,所述第八晶体管m8第一极作为第五节点c1分别与所述第七晶体管m7第二极、所述第十晶体管m10栅极和所述第十一晶体管m11栅极电连接,所述第九晶体管m9栅极与所述第二节点b2电连接,所述第九晶体管m9第一极与所述第八晶体管m8第二极电连接,所述第九晶体管m9第二极接入第二电源信号g,所述第十晶体管m10第一极接入所述第一电源信号vdd,所述第十一晶体管m11第一极与所述第十晶体管m10第二极电连接、并作为所述第一输出模块输出端,所述第十一晶体管m11第二极接入所述第二电源信号g;其中,所述第七晶体管m7、第十晶体管m10为低电位导通极性,所述第八晶体管m8、第九晶体管m9、第十一晶体管m11为高电位导通极性。

9、优选地,所述第一复位模块包括第十二晶体管m12,所述第二复位模块包括第十三晶体管13;所述第十二晶体管m12栅极接入复位信号rst,所述第十二晶体管m12第一极与所述第一转换模块第二输出端电连接,所述第十二晶体管m12第二极与所述第二节点b2电连接;所述第十三晶体管m13栅极接入复位信号rst,所述第十三晶体管m13第一极与所述第二节点b2电连接,所述第十三晶体管m13第二极接入第二电源信号g;其中,所述第十二晶体管m12为低电位导通极性,所述第十三晶体管m13为高电位导通极性。

10、进一步地,上述的一种d触发器,还包括第二输入模块、第二转换模块、第二输出模块和交叉耦合模块;

11、所述第二输入模块第二输入端,接入第二输入信号dn,所述第二输入信号dn是所述第一输入信号d的差分信号;所述第二输入模块第二输入端、所述第二转换模块第一输入端和所述第二输出模块第一输入端,接入时钟信号clk;所述第二输出模块输出端,输出第一输出信号qn;所述第二输入模块输出端为第三节点a2,所述第二转换模块第二输入端与所述第三节点a2电连接,所述第二转换模块第一输出端为第四节点b2,所述第二输出模块第二输入端与所述第四节点b2电连接;所述第二输入模块、第二转换模块和第二输出模块,在时钟信号clk的控制下完成第二输入信号dn的转换,实现所述d触发器第二输出信号qn输出;

12、所述第二输出模块包括串联的第三输出单元和第四输出单元,所述第三输出单元第一输入端为第二输出模块第一输入端,所述第三输出单元第二输入端为第二输出模块第二输入端,所述第三输出单元输出端为第六节点c2,所述第四输出单元输入端与第六节点c2电连接,所述第四输出单元输出端为第二输出模块输出端;

13、所述交叉耦合模块第一端与第五节点c1电连接,所述交叉耦合模块第二端与第六节点c2电连接,所述交叉耦合模块用于根据正反馈强制将第五节点c1的电位与第六节点c2的电位取反,以实现第二输出信号qn的复位。

14、优选地,上述的一种d触发器,还包括第一伪复位模块和第二伪复位模块;所述第一伪复位模块第一输入端和所述第二伪复位模块第一输入端,接入伪复位信号gnd;所述第一伪复位模块第二输入端与所述第二转换模块第二输出端电连接,所述第一伪复位模块输出端与所述第四节点b2电连接,所述第一伪复位模块在所述伪复位信号gnd的控制下始终导通;所述第二伪复位模块输出端与所述第四节点b2电连接,所述第二伪复位模块在所述伪复位信号gnd的控制下始终关断。

15、优选地,

16、所述第二输入模块包括第十四晶体管m4、第十五晶体管m15和第十六晶体管m16;所述第十四晶体管m14栅极接入第二输入信号dn,所述第十四晶体管m14第一极接入第一电源信号vdd,所述第十五晶体管m15栅极接入时钟信号clk,所述第十五晶体管m15第一极与所述第十四晶体管m14第二极电连接,所述第十六晶体管m16栅极接入第二输入信号dn,所述第十六晶体管m16第一极与所述第十五晶体管m15第二极电连接、并作为第三节点a2,所述第十六晶体管m16第二极接入第二电源信号g;其中,所述第十四晶体管m4、第十五晶体管m15为低电位导通极性,所述第十六晶体管m16为高电位导通极性;

17、所述第二转换模块包括第十七晶体管m17、第十八晶体管m18和第十九晶体管m19;所述第十七晶体管m17栅极接入时钟信号clk,所述第十七晶体管m17第一极接入第一电源信号vdd;所述第十八晶体管m18栅极与所述第三节点a2电连接;所述第十八晶体管m18第一极与所述第十七晶体管m17第二极电连接、并作为所述第四节点b2;所述第十九晶体管m19栅极接入时钟信号clk,所述第十九晶体管m19第一极与所述第十八晶体管m19第二极电连接,所述第十九晶体管m19第二极接入第二电源信号g;其中,所述第十七晶体管m17为低电位导通极性,所述第十八晶体管m18、第十九晶体管m19为高电位导通极性;

18、所述第二输出模块包括第二十晶体管m20、第二十一晶体管m21、第二十二晶体管m22、第二十三晶体管m23和第二十四晶体管m24;所述第二十晶体管m20栅极与所述第四节点b2电连接,所述第二十晶体管m20第一极接入第一电源信号vdd;所述第二十一晶体管m21栅极接入时钟信号clk,所述第二十一晶体管m21第一极作为六节点c2分别与所述第二十晶体管m20第二极、所述第二十三晶体管m23栅极和所述第二十四晶体管m24栅极电连接,所述第二十二晶体管m22栅极与所述第四节点b2电连接,所述第二十二晶体管m22第一极与所述第二十一晶体管m21第二极电连接,所述第二十二晶体管m22第二极接入第二电源信号g,所述第二十三晶体管m23第一极接入第一电源信号vdd,所述第二十四晶体管m24第一极与所述第二十三晶体管m23第二极电连接、并作为第二输出模块输出端,所述第二十四晶体管m24第二极接入第二电源信号g;其中,所述第二十晶体管m20、第二十三晶体管m23为低电位导通极性,所述第二十一晶体管m21、第二十二晶体管m22、第二十四晶体管m24为高电位导通极性;

19、所述交叉耦合模块包括第二十五晶体管m25和第二十六晶体管m26;所述第二十五晶体管m25栅极分别与所述第二十六晶体管m26第一极和所述第六节点c2电连接;所述第二十五晶体管m25第一极分别与所述第五节点c1和所述第二十六晶体管m26栅极电连接;所述第二十五晶体管m25第二极和所述第二十六晶体管m26第二极均接入第二电源信号g;其中,所述第二十五晶体管m25、第二十六晶体管m26为高电位导通极性。

20、优选地,所述第一伪复位模块包括第二十七晶体管m27,所述第二伪复位模块包括第二十八晶体管m28;所述第二十七晶体管m27栅极接入伪复位信号gnd,所述第二十七晶体管m27第一极为所述伪复位模块第一输入端,所述第二十七晶体管m27第二极与所述第四节点b2电连接;所述第二十八晶体管m28栅极接入伪复位信号gnd,所述第二十八晶体管m28第一极与所述第四节点b2电连接,所述第二十八晶体管m28第二极接入第二电源信号g;其中,所述第二十七晶体管m27为低电位导通极性,所述第二十八晶体管m28为高电位导通极性。

21、本发明一种d触发器有如下有益效果:1、设置有第一输入模块、第一转换模块和第一输出模块,以在时钟信号的控制下完成第一输入信号的转换,实现第一输出信号的可靠输出;并在上述基础上,设置有第一复位模块和第二复位模块;其中,第一复位模块在复位信号的作用下,配合第一转换模块共同控制第二节点的电位;第二复位模块在复位信号作用下控制第二节点的电位;也就是说,第一复位模块和第二复位模块共同作用于第二节点,通过控制第二节点的电位来控制第一输出模块的输出,使该d触发器具有复位功能。2、并且,本发明d触发器中仅需要一个时钟信号和一个复位信号即可实现d触发器的正常输出和复位功能,简化了控制逻辑;与此同时,本发明d触发器的控制只需要单根时钟信号线和单根复位信号线,节约了电路布线资源,简化了整体版图设计;因此,与现有技术相比,本发明可以实现d触发器的复位功能,并在此基础上节约电路布线资源,简化版图设计,以及简化控制逻辑。

- 还没有人留言评论。精彩留言会获得点赞!