基于绕线的延迟单元的制作方法

本发明适用于物理集成电路设计,尤其涉及一种基于绕线的延迟单元。

背景技术:

1、随着制程工艺的提升,在集成电路(integrated circuit,ic)的先进技术节点,导线电阻显著增加,使时序收敛变得越来越困难。但是,集成电路中增加的导线延迟在需要时可用于实现时序收敛,这样的结构称为延时单元(delay cell)。目前有两种典型的延迟单元:一,保持缓冲器(hold buffer),用于修复保持时间(hold time)违例;二,时钟缓冲器(clock buffer),用于调节时钟偏移(clock skew)。

2、大多数的保持时间违例都在几皮秒的尺度上,为了修复保持时间违例,需要在集成电路中插入数十万或更多的保持缓冲器。插入保持缓冲器的缺点包括但不限于:

3、保持时间违例的过度修复,因为插入保持缓冲器所取得的时序延迟往往超过所需要的,并可能导致如共享部分逻辑锥的路径的预置时间(setup time)违例;

4、插入大量保持缓冲器会干扰局部单元摆放和绕线,造成设计违例;

5、保持缓冲器可能放置在远离目标位置的地方,使得局部区域出现拥塞;

6、增加集成电路的功耗;

7、延时单元在不同工艺(process)、电压(voltage)、温度(temperature) 情况下不会按比例变化,从而导致过多非必要的手工修复(timing eco)。

8、较低的时钟偏移有利于2ghz以上高性能cpu(中央处理器)设计,调节时钟偏移一般是通过在集成电路中插入时钟缓冲器和使用不同驱动能力的时钟缓冲器来实现。但类似的,插入时钟缓冲器的方式会具有以下缺点:

9、时钟缓冲器的调整量较为粗糙,通过时钟缓冲器实现的延迟可能超过需要的延迟;

10、高性能cpu设计中一般采用时钟网格(clock mesh)的设计,然而时钟网格的逻辑基数固定,通常不允许插入额外的时钟缓冲器;

11、由于时钟节点所驱动的时序单元量众多,难以分别对每一个时序单元量的时钟偏移调节到理想的数值。

12、因此,有必要提供一种新的延迟单元设计来解决上述问题。

技术实现思路

1、本发明提供一种基于绕线的延迟单元,旨在解决现有技术的延迟单元设计受限于制程工艺和实现原理而不能精确调节路径延迟的技术问题。

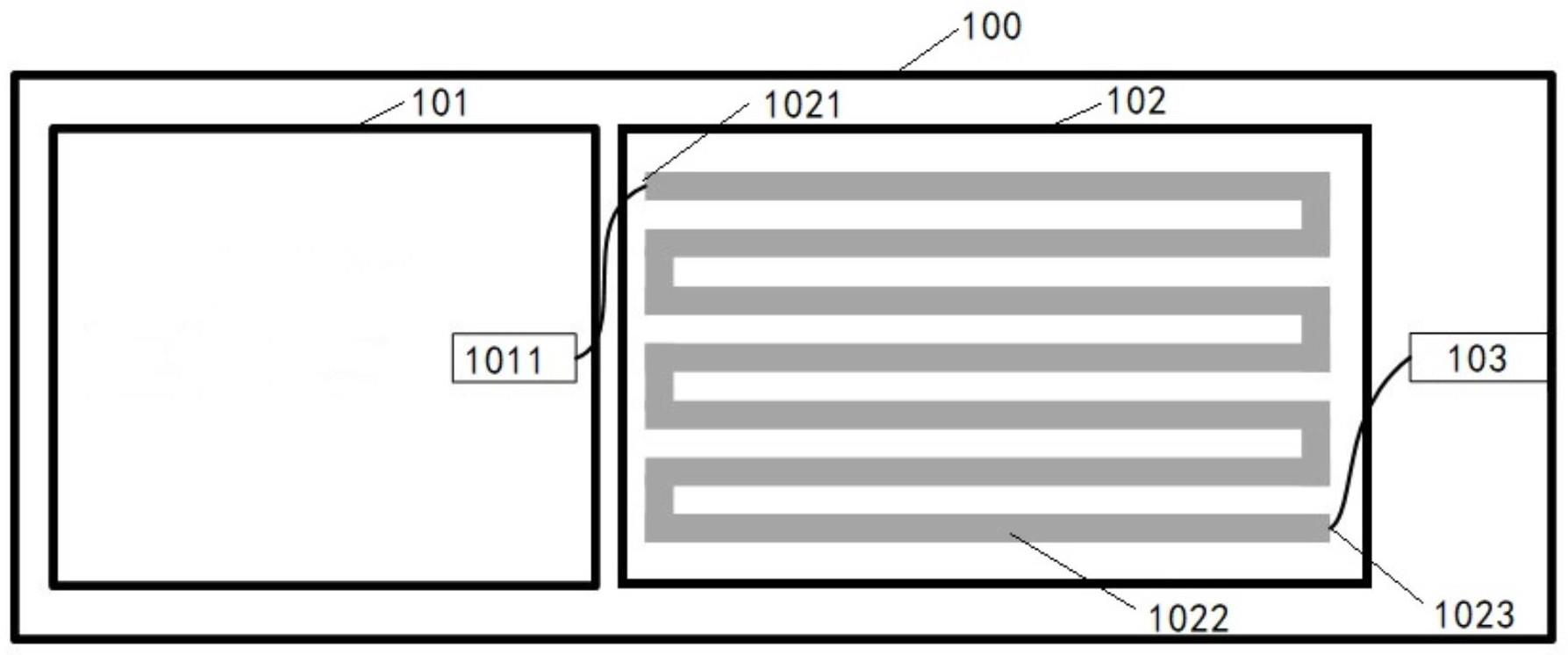

2、本发明具体提供了一种基于绕线的延迟单元,所述延迟单元包括标准子单元、和与所述标准子单元相邻并连接的至少一个绕线子单元:所述标准子单元包括输出引脚,每一所述绕线子单元包括绕线输入端、绕线层和绕线输出端;与所述标准子单元相邻并连接的所述绕线子单元的所述绕线输入端与所述输出引脚之间实现电连接,其中,

3、所述绕线层由至少两条绕线金属相接形成,每一所述绕线金属上设有多个通孔,不同的所述绕线金属之间通过插设于所述通孔的电阻金属实现电连接,并形成由多个所述绕线金属并联连接的层次堆叠结构,且不同的所述绕线金属之间堆叠时满足预设最小导线间距。

4、更进一步地,每一所述绕线子单元的所述绕线输入端和所述绕线输出端皆与所述标准子单元的所述输出引脚处于同一金属层。

5、更进一步地,不同的两个所述绕线子单元之间,通过将其中一个所述绕线子单元的所述绕线输出端和另一个所述绕线子单元的所述绕线输入端紧邻相接实现电连接,并形成层次堆叠结构。

6、更进一步地,不同的所述绕线子单元中的所述绕线层的有效绕线总长不同。

7、更进一步地,所述标准子单元设置于集成电路的m0金属层级或多晶硅层级,所述绕线子单元设置于m1金属层级、或m2金属层级、或m3金属层级。

8、更进一步地,每一所述绕线金属上还设有多个控制引脚,所述绕线层还包括可编程控制并插入所述控制引脚以调节所述绕线层的有效绕线总长的多个切断金属掩膜层。

9、更进一步地,所述绕线金属、所述电阻金属、以及所述切断金属掩膜层的电阻均不同。

10、更进一步地,所述延迟单元还包括设于所述标准子单元与所述绕线子单元之间的插指型电容子单元,所述插指型电容子单元的第一端分别与所述标准子单元的输出引脚以及所述绕线子单元的所述绕线输入端电连接,所述插指型电容子单元的第二端接地。

11、本发明所达到的有益效果,在于提出了一种应用与集成电路中的基于绕线的延迟单元,该延迟单元通过层叠设计能够更好地利用低金属层中的绕线区域,并通过紧邻连接形成延迟单元库,节约连接线,提高空间利用率,并且,还能够基于可编程控制的切断金属技术实现精确的路径延迟调节,提高绕线层的可修复能力,具有高兼容的特性。

技术特征:

1.一种基于绕线的延迟单元,其特征在于,所述延迟单元包括标准子单元和与所述标准子单元相邻并连接的至少一个绕线子单元;所述标准子单元包括输出引脚,每一所述绕线子单元包括绕线输入端、绕线层和绕线输出端;与所述标准子单元相邻并连接的所述绕线子单元的所述绕线输入端与所述输出引脚之间实现电连接,其中,

2.如权利要求1所述的基于绕线的延迟单元,其特征在于,每一所述绕线子单元的所述绕线输入端和所述绕线输出端皆与所述标准子单元的所述输出引脚处于同一金属层。

3.如权利要求2所述的基于绕线的延迟单元,其特征在于,不同的两个所述绕线子单元之间,通过将其中一个所述绕线子单元的所述绕线输出端和另一个所述绕线子单元的所述绕线输入端紧邻相接实现电连接,并形成层次堆叠结构。

4.如权利要求3所述的基于绕线的延迟单元,其特征在于,不同的所述绕线子单元中的所述绕线层的有效绕线总长不同。

5.如权利要求1所述的基于绕线的延迟单元,其特征在于,所述标准子单元设置于集成电路的m0金属层级或多晶硅层级,所述绕线子单元设置于集成电路的m1金属层级、或m2金属层级、或m3金属层级。

6.如权利要求1所述的基于绕线的延迟单元,其特征在于,每一所述绕线金属上还设有控制引脚,所述绕线层还包括可编程控制并插入所述控制引脚以调节所述绕线层的有效绕线总长的多个切断金属掩膜层。

7.如权利要求6所述的基于绕线的延迟单元,其特征在于,所述绕线金属、所述电阻金属、以及所述切断金属掩膜层的电阻均不同。

8.如权利要求1所述的基于绕线的延迟单元,其特征在于,所述延迟单元还包括设于所述标准子单元与所述绕线子单元之间的插指型电容子单元,所述插指型电容子单元的第一端分别与所述标准子单元的输出引脚以及所述绕线子单元的所述绕线输入端电连接,所述插指型电容子单元的第二端接地。

技术总结

本发明适用于物理集成电路设计技术领域,尤其涉及一种基于绕线的延迟单元。本发明提出了一种应用与集成电路中的基于绕线的延迟单元,该延迟单元通过层叠设计能够更好地利用低金属层中的绕线区域,并通过紧邻连接形成延迟单元库,节约连接线,提高空间利用率,并且,还能够基于可编程控制的切断金属技术实现精确的路径延迟调节,提高绕线层的可修复能力,具有高兼容的特性。

技术研发人员:李风雷

受保护的技术使用者:睿思芯科(深圳)技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!