数字锁相环及其操作方法与流程

本发明构思涉及集成电路器件,并且更具体地,涉及数字锁相环和操作数字锁相环的方法。

背景技术:

1、锁相环(pll)可生成相位固定的时钟信号。例如,时钟信号可用于从发送器发送数据或者在接收器中恢复数据。pll可被分类为模拟pll或数字pll。数字pll可被实现为占用小于模拟pll的面积的面积,并且可相对容易地重新配置。随着高速接口(诸如,外围组件互连快速(pcie))接口)的发展,对具有低抖动的数字pll的需求增加了。

技术实现思路

1、发明构思涉及具有相对低的抖动特性的数字锁相环(pll),该相对低的抖动特性通过数字环路滤波器的可调增益和可调占空比特性而被提供。

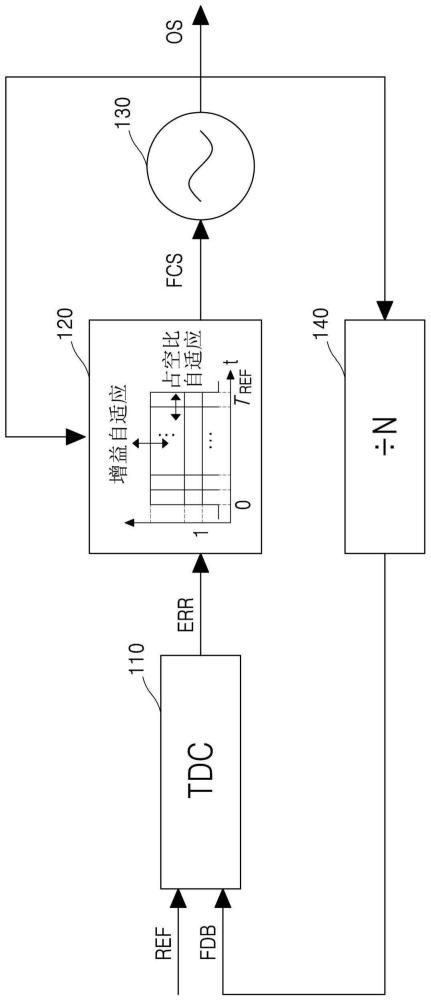

2、根据发明构思的一个方面,提供了一种数字锁相环,所述数字锁相环包括:(i)数控振荡器(dco),被配置为:生成具有基于频率控制信号可调节的频率的振荡信号,(ii)分频器,被配置为:响应于对所述振荡信号的频率进行分频而生成反馈信号,(iii)时间-数字转换器(tdc),被配置为:检测参考信号与反馈信号之间的相位差并生成与所述相位差对应的误差信号,以及(iv)数字环路滤波器,被配置为:接收所述误差信号和所述振荡信号(作为反馈)并生成频率控制信号。数字环路滤波器包括:增益/占空比控制电路,被配置为基于所述误差信号和所述振荡信号来控制数字环路滤波器的增益和占空比中的至少一个;滤波器电路,被配置为基于增益/占空比控制电路的控制来滤除所述误差信号的噪声并生成频率控制信号。

3、根据发明构思的另一方面,提供了一种数字锁相环,所述数字锁相环包括:(i)数控振荡器(dco),配置为:生成具有基于频率控制信号可调节的频率的振荡信号,(ii)分频器,被配置为:通过对所述振荡信号的频率进行分频来生成反馈信号,(iii)时间-数字转换器(tdc),被配置为:检测参考信号与反馈信号之间的相位差并生成与所述相位差对应的误差信号,以及(iv)数字环路滤波器,被配置为:接收所述误差信号并生成所述频率控制信号。数字环路滤波器可包括:增益控制电路,被配置为基于所述误差信号控制数字环路滤波器的增益;占空比控制电路,被配置为基于所述误差信号和所述振荡信号控制数字环路滤波器的占空比;以及滤波器电路,被配置为滤除所述误差信号的噪声并基于占空比控制电路或增益控制电路的控制生成频率控制信号。

4、根据发明构思的另一方面,提供了一种操作数字锁相环的方法。所述操作方法包括:生成具有基于频率控制信号可调节的频率的振荡信号;通过对所述振荡信号的频率进行分频来生成反馈信号;检测参考信号与反馈信号之间的相位差;生成与所述相位差对应的误差信号;基于所述误差信号控制数字环路滤波器的增益;以及基于所述误差信号和所述振荡信号控制数字环路滤波器的占空比。

5、根据发明构思的另一方面,提供了一种片上系统(soc),所述soc包括:数字锁相环;以及应用处理器,被配置为:响应于数字锁相环的振荡信号而操作。数字锁相环包括:数控振荡器(dco),被配置为:生成具有基于频率控制信号可调节的频率的振荡信号;分频器,被配置为通过对所述振荡信号的频率进行分频来生成反馈信号;时间-数字转换器(tdc),被配置为:检测参考信号与反馈信号之间的相位差并生成与所述相位差对应的误差信号;以及数字环路滤波器,被配置为:接收所述误差信号以生成频率控制信号。数字环路滤波器可包括:滤波器电路,被配置为基于所述误差信号生成频率控制信号;以及增益/占空比控制电路,被配置为控制数字环路滤波器的增益和占空比中的至少一个。

技术特征:

1.一种数字锁相环,包括:

2.根据权利要求1所述的数字锁相环,其中,数字环路滤波器电路包括:

3.根据权利要求2所述的数字锁相环,

4.根据权利要求3所述的数字锁相环,其中,数字环路滤波器电路还包括:

5.根据权利要求4所述的数字锁相环,其中,增益/占空比控制电路被配置为:当数字环路滤波器处于活动模式时,控制复用器输出相加信号。

6.根据权利要求4所述的数字锁相环,其中,增益/占空比控制电路被配置为:当数字环路滤波器处于非活动模式时,控制复用器输出延迟的第二中间信号。

7.根据权利要求4所述的数字锁相环,其中,增益/占空比控制电路被配置为:控制数字环路滤波器的增益和占空比中的至少一个,以减少所述振荡信号的均方根抖动。

8.根据权利要求4所述的数字锁相环,其中,增益/占空比控制电路被配置为:基于所述误差信号的自相关来控制数字环路滤波器的增益和占空比中的至少一个。

9.根据权利要求4所述的数字锁相环,其中,增益/占空比控制电路包括计数器,计数器被配置为:对所述振荡信号的脉冲数量进行计数;并且其中,增益/占空比控制电路被配置为:基于所述振荡信号的脉冲数量来控制数字环路滤波器的占空比。

10.一种数字锁相环,包括:

11.根据权利要求10所述的数字锁相环,其中,增益控制电路被配置为:控制数字环路滤波器的增益,以减少所述振荡信号的均方根抖动。

12.根据权利要求10所述的所述的数字锁相环,其中,占空比控制电路被配置为:控制数字环路滤波器的占空比,以减少所述振荡信号的均方根抖动。

13.根据权利要求10所述的数字锁相环,其中,增益控制电路被配置为:基于所述误差信号的自相关来控制数字环路滤波器的增益。

14.根据权利要求10所述的数字锁相环,其中,占空比控制电路包括计数器,计数器被配置为对所述振荡信号的脉冲数量进行计数;并且其中,占空比控制电路被配置为:基于所述振荡信号的脉冲数量来控制数字环路滤波器的占空比。

15.一种操作数字锁相环的方法,包括:

16.根据权利要求15所述的方法,其中,控制占空比的步骤包括:

17.根据权利要求16所述的方法,其中,生成第一中间信号的步骤包括:将所述误差信号乘以比例增益以生成第一中间信号;并且其中,累加所述误差信号的步骤包括:将所述误差信号乘以积分增益以生成内部信号,以及累加内部信号以生成第二中间信号。

18.根据权利要求17所述的方法,其中,控制占空比的步骤包括:

19.根据权利要求15所述的方法,其中,控制占空比的步骤包括:控制数字环路滤波器的占空比,以减少所述振荡信号的均方根抖动。

20.根据权利要求15所述的方法,其中,控制占空比的步骤包括:

技术总结

公开了数字锁相环及其操作方法。所述数字锁相环(PLL)包括:(i)数控振荡器(DCO),被配置为:生成具有响应于频率控制信号可调节的频率的振荡信号,(ii)分频器,被配置为:响应于对所述振荡信号的频率进行分频而生成反馈信号,(iii)时间‑数字转换器(TDC),被配置为:检测参考信号与反馈信号之间的相位差,并且基于所述相位差生成误差信号,以及(iv)数字环路滤波器,被配置为:响应于所述误差信号和所述振荡信号而生成频率控制信号。

技术研发人员:李镕善,朴宰佑,郭明保,郑振旭,崔桢焕

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!