IO接口置换电路及其接口电路的制作方法

本发明涉及本发明涉及模拟集成电路设计领域,更具体地说,涉及一种io接口置换电路以及包括其的io接口电路。

背景技术:

1、移动行业处理器接口(mipi,mobile industry processor interface)是一个由移动设备厂商联合组成的非营利性组织,其致力于为移动设备提供一系列标准化的接口和规范,包括硬件接口、软件接口、通信协议等。mipi电路常用于移动设备领域,如智能手机、平板电脑、智能手表、车载娱乐等。mipi电路的特点是高速、低功耗、可靠性高,具有极佳的抗干扰性能。射频前端(rffe,rf front-end)是mipi中的一种协议,其是一种用于控制射频前端(rf front-end)组件的接口协议。射频前端是指手机中用于无线通信的前端电路部分,包括滤波器、放大器、开关、天线等。rffe协议主要用于控制这些组件的开关、增益、频率选择等操作,实现对射频信号的控制和调整。在rffe mipi协议中,主设备(master)和从设备(slave)是两种不同的设备,图1是示出了mipi rffe中主设备(master)和从设备(slave)的关系的示意图。如图1所示,主设备通常是控制器或者处理器,它们通过rffe总线向从设备发送控制命令,以控制从设备的工作。从设备可以是各种类型的设备,如射频前端模块(rf front-end module)、功放器件(power amplifier,pa)等。在rffe mipi系统中,master和slave之间是一种主从关系,也就是master通过rffe总线对slave进行控制,而slave只能在master的控制下工作。master和slave之间的通信采用了mipi协议,master通过发送特定的命令和数据包来控制slave的工作,slave则通过发送响应数据包来向master返回响应结果。这样,master就可以通过rffe总线控制多个slave设备,从而实现对整个rffe系统的控制。总的来说,master和slave在rffe mipi系统中是一种主从关系,master控制着整个系统的运行,而slave则被动地接受master的控制,执行相应的命令和操作。

2、在rffe mipi协议中,vio、sdata和sclk是rffe总线上的三个信号线,它们分别代表:电压输入/输出信号(vio,voltageinput/output),用于连接rffe总线和master设备的电源电压;串行数据信号(sdata,serial data),用于在master和slave之间传输控制命令和数据信息;串行时钟信号(sclk,serial clock),用于同步master和slave之间的数据传输,保证数据传输的正确性和稳定性。这三个信号线是rffe mipi协议中非常重要的组成部分,它们共同构成了rffe总线,实现了master和slave之间的通信和控制。sdata和sclk信号线是密切相关的,它们之间的关系是同步的。具体来说,master在向slave发送数据时,会根据sclk的时钟脉冲来产生相应的数据位,并通过sdata进行传输。slave在接收到数据时,也会根据sclk的时钟脉冲来确定数据的传输速率和传输时序,并通过sdata进行数据接收。因此,sdata和sclk信号线之间的同步关系是rffe mipi协议中非常重要的一部分,它保证了master和slave之间的数据传输的正确性和可靠性。图2是示出了mipi电路的示意图。参考图2,mipi电路包括io接口电路、数字电路和模拟电路三部分。从设备唯一标识符(usid,unique slave identifier)是mipi协议中的一种标识符,用于标识mipi系统中的从设备。每个从设备都需要一个唯一的usid,主设备可以通过usid来选择特定的从设备进行通信。在mipi中,usid是用于配置和控制从设备的标识符,包括硬件接口、传输协议、寄存器映射等信息。在电路中usid<3:0>=sa<3:0>,从设备地址(sa,slave address)用来唯一标识rffe总线上的每个从设备。在rffe协议中,每个从设备都必须具有唯一的sa。因此,当主设备需要与从设备进行通信时,必须使用正确的sa来寻址所需的从设备。

3、在当今的5g手机射频系统中,需要用到多个主天线和副天线,以支持多个频段和多个天线组合方式的通信。因此,为了实现这种天线切换,需要使用多个具有mipi控制功能的天线开关器件,例如,单极四掷(sp4t)开关器件。这些开关器件通过mipi总线接口与手机处理器通信,控制不同的天线或滤波器在天线输入和输出之间进行信号切换,这种天线切换技术对于实现高效的5g通信和优化信号强度至关重要。一般的sp4t开关具有1.1x1.1mm的封装尺寸,具有9个引脚。图3是示出了的sp4t开关芯片的引脚示意图。如图3所示。9个引脚包括5个射频引脚

4、rf1/rf2/rf3/rf4/rfc、一个gnd引脚和一组mipi信号引脚。为了实现在一个手机主板实用多个sp4t天线开关器件的需求,需要每个器件具有唯一的usid,因此需要厂家提供具有不同uisd的芯片。一般厂家的做法是设计多款芯片,每款芯片被配置不同的usid提供给手机厂家使用。对于芯片设计厂家来说,这种做法增加了产品型号和设计成本。对于手机厂家来说,这种做法增加了物料清单(bom),不利于备货和库存管理。

技术实现思路

1、本发明的一方面提供了一种io接口置换电路,包括数据选择器(mux)、脉冲扩展电路(pulse extended)、d锁存器(d latch)和计数器(counter)。在mipi io接口电路中应用根据本发明实施例的io接口置换电路,可以实现sdata和sclk的位置置换,并根据io端口置换信息自动修改芯片的usid,进一步可以实现在一块手机主板上应用两颗相同的芯片。这种方法可为芯片设计厂家带来多项益处,如降低产品型号数量及设计成本等;对于手机厂家而言,该方法有助于优化物料清单bom,以提升备货及库存管理效率。

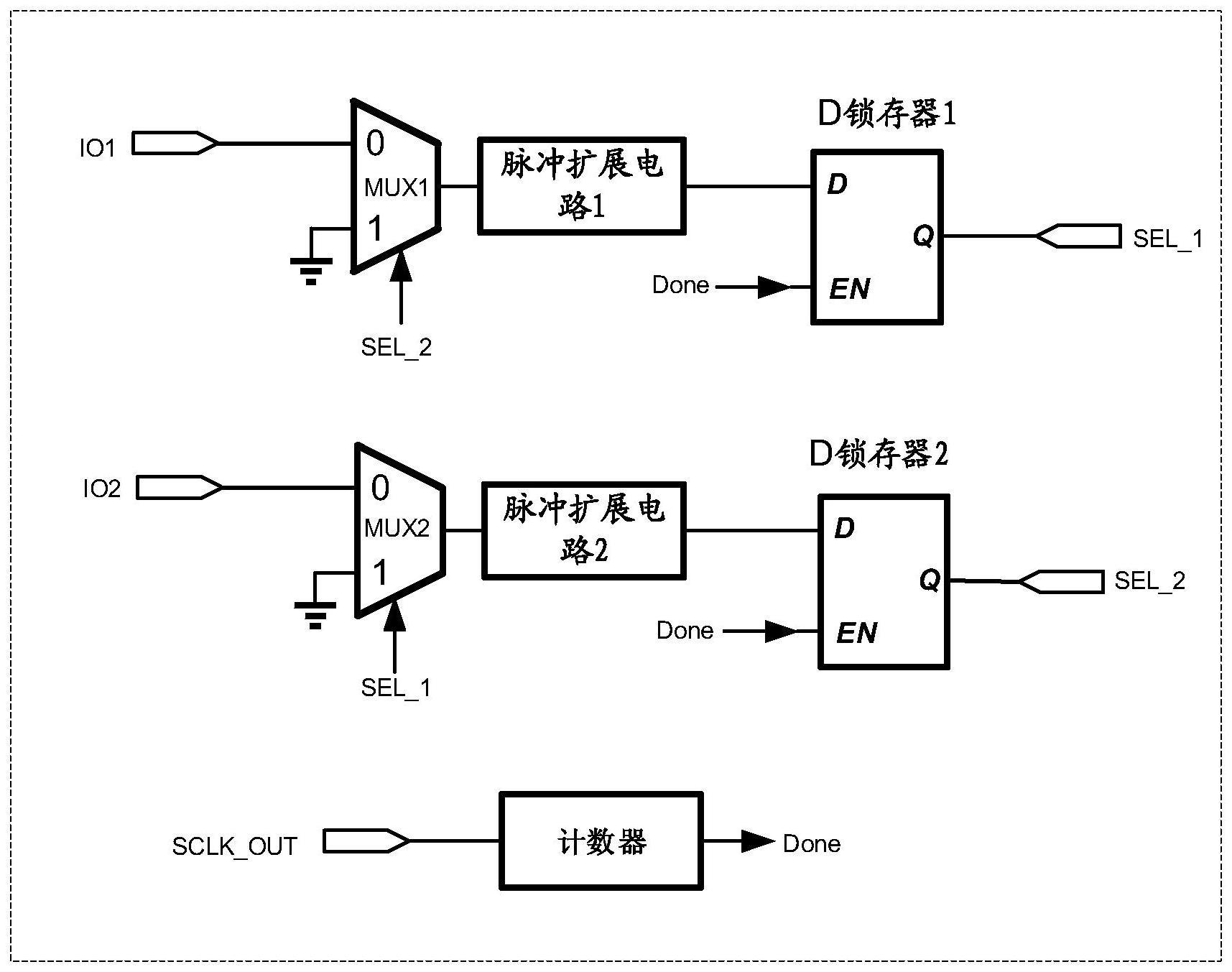

2、本发明的一方面提出了一种io接口置换电路,包括:第一io端口和第二io端口,所述第一io端口被配置为用于接收串行数据sdata信号和串行时钟sclk信号中的一个,并且所述第二io端口被配置为用于接收串行数据sdata信号和串行时钟sclk信号中的另一个;第一数据选择器和第二数据选择器,所述第一数据选择器被配置为以第一io端口作为所述第一数据选择器输入中的一个并且根据第二选择信号来选择其输入中的一个作为所述第一数据选择器的输出端,所述第二数据选择器被配置为以第二io端口作为所述第二数据选择器输入中的一个并且根据第一选择信号来选择其输入中的一个作为所述第二数据选择器的输出端;第一脉冲扩展电路和第二脉冲扩展电路,所述第一脉冲扩展电路被配置为连接到第一数据选择器的输出端,并且所述第二脉冲扩展电路被配置为连接到第二数据选择器的输出端,所述第一脉冲扩展电路和第二脉冲扩展电路被配置为分别对所述第一脉冲扩展电路和第二脉冲扩展电路的输入信号扩展其脉冲持续时间;第一锁存器和第二锁存器,所述第一锁存器被配置为用于接收所述第一脉冲扩展电路的输出并且根据控制信号来执行锁存以输出第一选择信号,所述第二锁存器被配置为用于接收所述第二脉冲扩展电路的输出并且根据控制信号来执行锁存以输出第二选择信号;以及计数器,所述计数器被配置为对时钟信号进行计数,并且根据计数器的倒计时时间来输出控制信号。

3、本发明的另一方面提出了一种io接口置换电路,其中,所述第一数据选择器被配置为使得第一io端口连接到所述第一数据选择器的第0输入端,并且所述第一数据选择器的第1输入端接地;所述第二数据选择器被配置为使得第二io端口连接到所述第二数据选择器的第0输入端,并且所述第二数据选择器的第1输入端接地,并且其中,第一选择信号等于0时,所述第一数据选择器的第0输入端数据传递到所述第一数据选择器的输出端,以及当第一选择信号等于1时,所述第一数据选择器的第1输入端数据传递到所述第一数据选择器输出端;第二选择信号等于0时,所述第二数据选择器的第0输入端数据传递到所述第二数据选择器的输出端,以及当第二选择信号等于1时,所述第二数据选择器的第1输入端数据传递到所述第二数据选择器输出端。

4、本发明的另一方面提出了一种io接口置换电路,其中,第一脉冲扩展电路和第二脉冲扩展电路被配置为将其输入信号的脉冲持续时间扩展为大于所述计数器的倒计时时间。

5、本发明的另一方面提出了一种io接口置换电路,其中,所述第一锁存器和第二锁存器被配置为d锁存器,其中,所述第一脉冲扩展电路的输出端连接到所述第一锁存器的d输入端,并且所述控制信号连接到所述第一锁存器的e输入端,以输出第一选择信号,并且其中,所述第二脉冲扩展电路的输出端连接到所述第二锁存器的d输入端,并且所述控制信号连接到所述第二锁存器的e输入端,以输出第二选择信号。

6、本发明的另一方面提出了一种io接口置换电路,其中,所述串行数据sdata信号被配置为包括用于指示sdata信号的数据帧开始的序列开始条件ssc指令。

7、本发明的另一方面提出了一种包括如上所述的任何一个方面的io接口置换电路的io接口电路,包括:io接口置换电路,其被配置为从第一io端口和第二io端口接收信号,并且提供第一选择信号和第二选择信号;第三数据选择器和第四数据选择器,所述第三数据选择器被配置为以第一io端口作为所述第三数据选择器的输入并且根据第一选择信号来将所述第三数据选择器的输入通过所述第三数据选择器的第0输出端或者第1输出端输出,并且所述第四数据选择器被配置为以第二io端口作为所述第四数据选择器的输入并且根据第二选择信号来将所述第四数据选择器的输入通过所述第四数据选择器的第0输出端或者第1输出端输出;以及第一缓冲区和第二缓冲区,所述第一缓冲区被配置为从第三数据选择器和第四数据选择器的第0输出端接收信号,并且输出缓冲的串行时钟sclk信号,并且所述第二缓冲区被配置为从第三数据选择器和第四数据选择器的第1输出端接收信号,并且输出缓冲的串行数据sdata信号。

8、本发明的另一方面提出了一种io接口电路,其中,所述第一缓冲区为第一缓冲器,其被配置为从第三数据选择器和第四数据选择器的第0输出端接收信号,并且输出缓冲的串行时钟sclk信号。

9、本发明的另一方面提出了一种io接口电路,其中,所述第二缓冲区包括第二缓冲器和第三缓冲器,其中,所述第二缓冲器的输入端连接到第三缓冲器的输出端,并且所述第二缓冲器的输出端连接到第三缓冲器的输入端,并且其中,从第三数据选择器和第四数据选择器的第1输出端输出的信号被提供到第三缓冲器的输入端,并且从所述第三缓冲器的输出端输出缓冲的串行时钟sclk信号。

10、本发明的另一方面提出了一种io接口电路,还包括第五数据选择器,所述第五数据选择器被配置为:第一从设备唯一标识符usid被提供到所述第五数据选择器的第0输入端,第二从设备唯一标识符usid被提供到所述第五数据选择器的第1输入端,并且根据第第二选择信号来选择所述第五数据选择器的第0输入端和第1输入端中的一个作为从设备唯一标识符usid输出。

11、本发明的另一方面提出了一种io接口电路,其中,所述io接口置换电路被配置为从所述第一缓冲区接收缓冲的串行时钟sclk信号。

- 还没有人留言评论。精彩留言会获得点赞!