半导体结构及其制备方法与流程

本公开涉及半导体,特别是涉及一种半导体结构及其制备方法。

背景技术:

1、dram(dynamic random access memory,动态随机存取存储器),具有集成度高、功耗低、价格便宜等优点,所以在大容量存储器中普遍采用。

2、然而,随着半导体的高度集成以及摩尔定律向10nm至20nm之间级别的演进,要求有源区的排布更加密集,存储单元的尺寸越来越小,尤其是在关键尺寸小于15nm的dram制造过程中,减小位线之间的寄生电容变得越来越困难。因此,亟需一种半导体结构及其制备方法,在半导体尺寸收缩的同时减小寄生电容,以提高存储器件的性能。

技术实现思路

1、基于此,本公开提供一种半导体结构及其制备方法,能够减小位线间的寄生电容,进而提高半导体器件的整体性能。

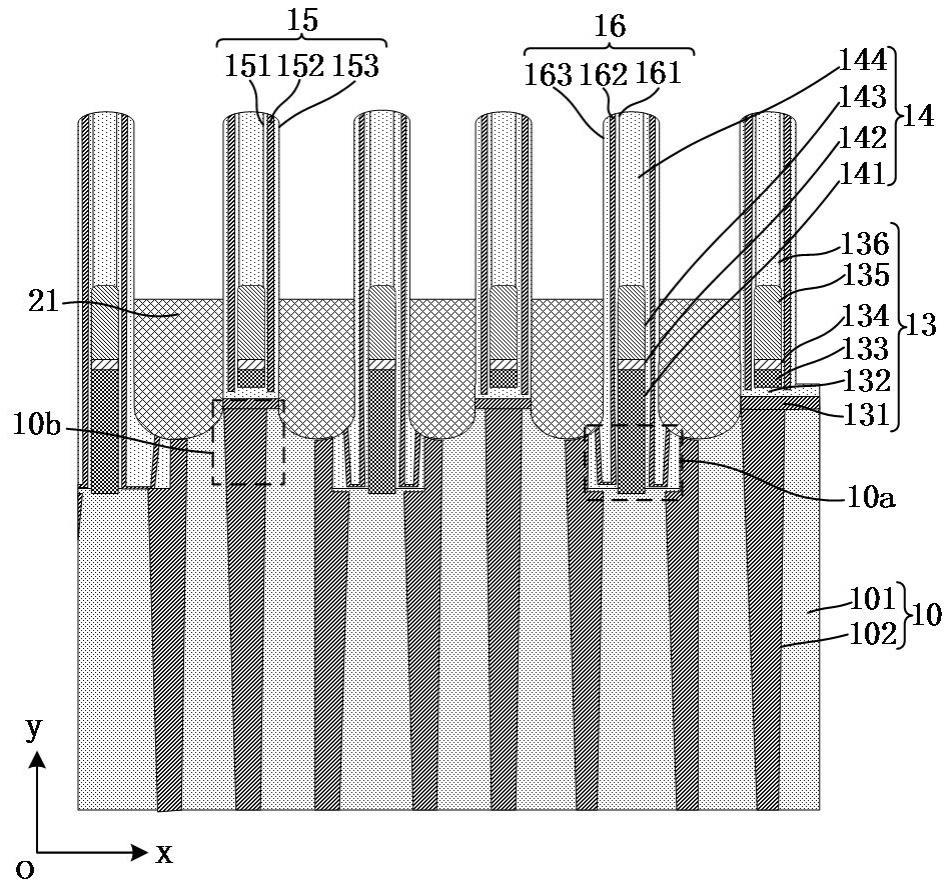

2、根据本公开的各种实施例,一方面提供一种半导体结构,包括衬底和第一位线立柱;第一位线立柱位于衬底上,其包括沿衬底的厚度方向依次叠置的第一介电层、第一绝缘层及第一接触层,第一绝缘层与衬底相邻;其中,第一绝缘层具有第一预设厚度,且第一预设厚度关联于第一介电层、第一绝缘层及第一接触层的厚度和;第一绝缘层的顶面沿第一方向的长度与第一绝缘层的底面沿第一方向的长度比为第一目标值;第一方向、第一绝缘层的顶面和底面均与厚度方向垂直。

3、于上述实施例中的半导体结构中,第一位线立柱中的第一绝缘层具有第一预设厚度,且第一预设厚度与第一介电层、第一绝缘层及第一接触层的厚度和相关,即当第一介电层、第一绝缘层及第一接触层的厚度和不变时,通过增大第一介电层和第一接触层的厚度,能够使得第一预设厚度减小。在相关技术中,由于多层结构层叠的复杂性以及刻蚀工艺精度的限制,会导致在刻蚀形成第一位线立柱时,使得第一位线立柱中越靠近衬底的部分层结构,其侧壁刻蚀越不完全,因此,会导致第一绝缘层的侧壁并不能够完全垂直于第一方向,即水平方向;且由于靠近衬底的部分刻蚀不完全,会使得第一绝缘层的底面沿第一方向的长度远大于其顶面沿第一方向的长度,以致第一绝缘层的底面以及靠近底面的位置沿第一方向的尺寸较大,占据了第一位线立柱侧壁方向的空间,使其与相邻的位线立柱之间的距离在靠近衬底的部分变得较小,增大了寄生电容,影响了器件的整体性能。本公开通过控制第一绝缘层的厚度,即第一预设厚度,来控制第一绝缘层侧壁的垂直程度,当第一预设厚度在第一介电层、第一绝缘层及第一接触层的厚度和中占据的比例更小时,第一绝缘层的侧壁更容易垂直于第一方向,同时第一绝缘层的顶面沿第一方向的长度与其底面沿第一方向的长度的差值更小,长度比被控制在第一目标值,第一位线立柱的垂直程度更好、性能更优。另外,第一绝缘层的垂直程度更好,也能够为第一绝缘层的侧壁方向留出更多的空间,使得第一位线立柱与其相邻的位线立柱之间的间距增大,进而减小寄生电容,进一步提升存储结构的整体性能。

4、在其中一些实施例中,第一预设厚度与第一介电层的厚度、第一接触层的厚度均成负相关;其中,第一预设厚度的范围为[1/6t,1/4t];其中,t为第一介电层、第一绝缘层及第一接触层的厚度和。

5、在其中一些实施例中,第一预设厚度的范围为[3nm,10nm]。

6、在其中一些实施例中,第一目标值的范围为[0.8,1]。

7、在其中一些实施例中,半导体结构还包括第一位线侧墙,其位于第一位线立柱的外侧壁上,第一位线侧墙沿第一方向的长度关联于第一绝缘层的底面沿第一方向的长度。

8、在其中一些实施例中,第一位线侧墙沿第一方向的长度与第一绝缘层的底面沿第一方向的长度成负相关。

9、在其中一些实施例中,衬底内包括沿第一方向交替排布的有源区和隔离结构,且衬底包括沿第一方向交替排布的凹槽及凸出部,第一位线立柱位于凸出部的顶面,且与其正下方的隔离结构连接;半导体结构还包括第二位线立柱,其部分位于凹槽内且与凹槽暴露的有源区连接。

10、在其中一些实施例中,第一位线立柱还包括沿衬底的厚度方向依次叠置的第一阻挡层、第一导电层及第一位线盖层,第一接触层与第一阻挡层相邻;其中,第一位线盖层的厚度范围为[10nm,30nm]。

11、在其中一些实施例中,第二位线立柱包括沿厚度方向依次叠置的位线插塞、第二阻挡层、第二导电层及第二位线盖层;其中,位线插塞与凹槽暴露的有源区连接,第二位线盖层的厚度范围为[10nm,30nm]。

12、本公开的另一方面还提供一种半导体结构的制备方法,包括:提供衬底;于衬底上形成第一位线立柱,第一位线立柱包括沿衬底的厚度方向依次叠置的第一介电层、第一绝缘层及第一接触层,第一绝缘层与衬底相邻;其中,第一绝缘层具有第一预设厚度,且第一预设厚度关联于第一介电层、第一绝缘层及第一接触层的厚度和;第一绝缘层的顶面沿第一方向的长度与第一绝缘层的底面沿第一方向的长度比具有第一目标值;第一方向、第一绝缘层的顶面和底面均与厚度方向垂直。

13、于上述实施例中的半导体结构的制备方法中,通过于沿衬底的厚度方向形成依次叠置的第一介电层、第一绝缘层及第一接触层,且将第一预设厚度设置为关联于第一介电层、第一绝缘层及第一接触层的厚度和、第一绝缘层的顶面沿第一方向的长度与第一绝缘层的底面沿第一方向的长度比具有第一目标值,能够使得第一绝缘层的侧壁与衬底表面的夹角更接近于90°,并且能够增大第一位线立柱与相邻位线立柱之间的空间,以减小寄生电容。本公开克服了相关技术中第一绝缘层的侧壁并不能够完全垂直于第一方向且第一位线立柱与相邻的位线立柱之间的距离在靠近衬底的部分较小的问题,通过控制第一绝缘层的厚度,即第一预设厚度,来控制第一绝缘层侧壁的垂直程度,当第一预设厚度在第一介电层、第一绝缘层及第一接触层的厚度和中占据的比例更小时,第一绝缘层的侧壁更容易垂直于第一方向,同时第一绝缘层的顶面沿第一方向的长度与其底面沿第一方向的长度的比值被控制在第一目标值,第一位线立柱的垂直程度更好、性能更优;还使得第一位线立柱与其相邻的位线立柱之间的间距增大,进而减小寄生电容以提高器件性能。

14、在其中一些实施例中,衬底内包括沿第一方向交替排布的有源区和隔离结构,且衬底包括沿第一方向交替排布的凹槽及凸出部,第一介电层位于凸出部上,第一位线立柱位于凸出部的顶面,且与其正下方的隔离结构连接;形成第一位线立柱,包括:于衬底上依次形成沿厚度方向叠置的绝缘材料层、插塞材料层、阻挡材料层、导电材料层及盖层材料层,绝缘材料层位于凸出部上的第一介电层上,插塞材料层至少填满凹槽;刻蚀导电材料层及盖层材料层,以形成沿厚度方向依次叠置的第一导电层及第一位线盖层;刻蚀绝缘材料层、插塞材料层及阻挡材料层,以形成第一位线立柱,第一位线立柱包括沿厚度方向依次叠置的第一介电层、第一绝缘层、第一接触层、第一阻挡层、第一导电层及第一位线盖层。

15、在其中一些实施例中,形成第一绝缘层、第一接触层及第一阻挡层,包括:于第一预设工艺环境下刻蚀绝缘材料层、插塞材料层及阻挡材料层,剩余的绝缘材料层形成第一绝缘层,剩余的插塞材料层位于第一绝缘层顶面的部分形成第一接触层,剩余的插塞材料层位于凹槽内及凹槽顶面的部分形成中间插塞层,剩余的阻挡材料层位于第一接触层顶面的部分形成第一阻挡层,剩余的阻挡材料层位于中间插塞层顶面的部分形成第二阻挡层。

16、在其中一些实施例中,第一预设工艺环境包括第一工艺气体及第一预设压力;其中,第一工艺气体选自氯气、三氟化氮、氮气、惰性气体和其组合,第一预设压力范围为[4mt,6mt]。

17、在其中一些实施例中,形成第一导电层及第一位线盖层,包括:于第二预设工艺环境下刻蚀盖层材料层,并于第三预设工艺环境下刻蚀导电材料层,剩余的导电材料层位于第一阻挡层顶面的部分形成第一导电层,剩余的导电材料层位于第二阻挡层顶面的部分形成第二导电层,剩余的盖层材料层位于第一导电层顶面的部分形成第一位线盖层,剩余的盖层材料层位于第二导电层顶面的部分形成第二位线盖层。

18、在其中一些实施例中,形成第一位线立柱之后,还包括:于第四预设工艺环境下对中间插塞层进行处理,形成沿第一方向间隔排布的位线插塞,以形成第二位线立柱,第二位线立柱包括沿厚度方向依次叠置的位线插塞、第二阻挡层、第二导电层以及第二位线盖层。

19、在其中一些实施例中,第二预设工艺环境包括第二工艺气体及第二预设压力;其中,第二工艺气体选自四氟化碳、三氟甲烷、氧气、氮气、惰性气体和其组合,第二预设压力范围为[13mt,17mt]。

20、在其中一些实施例中,第三预设工艺环境包括第三工艺气体及第三预设压力;其中,第三工艺气体选自氯气、三氟化氮、氧气、氮气、惰性气体和其组合,第三预设压力范围为[4mt,6mt]。

21、在其中一些实施例中,第四预设工艺环境包括第四工艺气体及第四预设压力;其中,第四工艺气体选自溴化氢、氧气、惰性气体和其组合,第四预设压力范围为[18mt,22mt]。

- 还没有人留言评论。精彩留言会获得点赞!