开关电路与芯片的制作方法

本技术涉及电子电路,特别是涉及一种开关电路与芯片。

背景技术:

1、随着usb pd快充技术的普及,线缆作为设备之间的电力传输的介质,重要性逐渐凸显。尤其是在高压大电流的工作状态下,不仅对线材的材质,线径有要求,而且还需要加入usb-if协会认证的电子标记芯片。有电子标记芯片的线缆可以支持最大5a电流,无电子标记芯片的线缆只能支持最大3a电流。基于此,usb type-c接口需要支持为电子标记芯片供电的功能,以为电子标记芯片供电。同时,由于充电电压的提高,usb type-c接口上的总线电源管脚可以支持到20v的高压。

2、然而,在实际充电过程中,很容易造成usb type-c接口的通道配置管脚和总线电源管脚短路,导致通道配置管脚的电压过高,并高于usb type-c接口的芯片供电管脚上的电压。进而,在为电子标记芯片供电的过程中,导致电流会经电子标记芯片的cc管脚倒灌到vconn端,会损坏vconn端的供电电源和芯片的vconn管脚。

技术实现思路

1、本技术旨在提供一种开关电路与芯片,能够防止电流经电子标记芯片的cc管脚倒灌到vconn端。

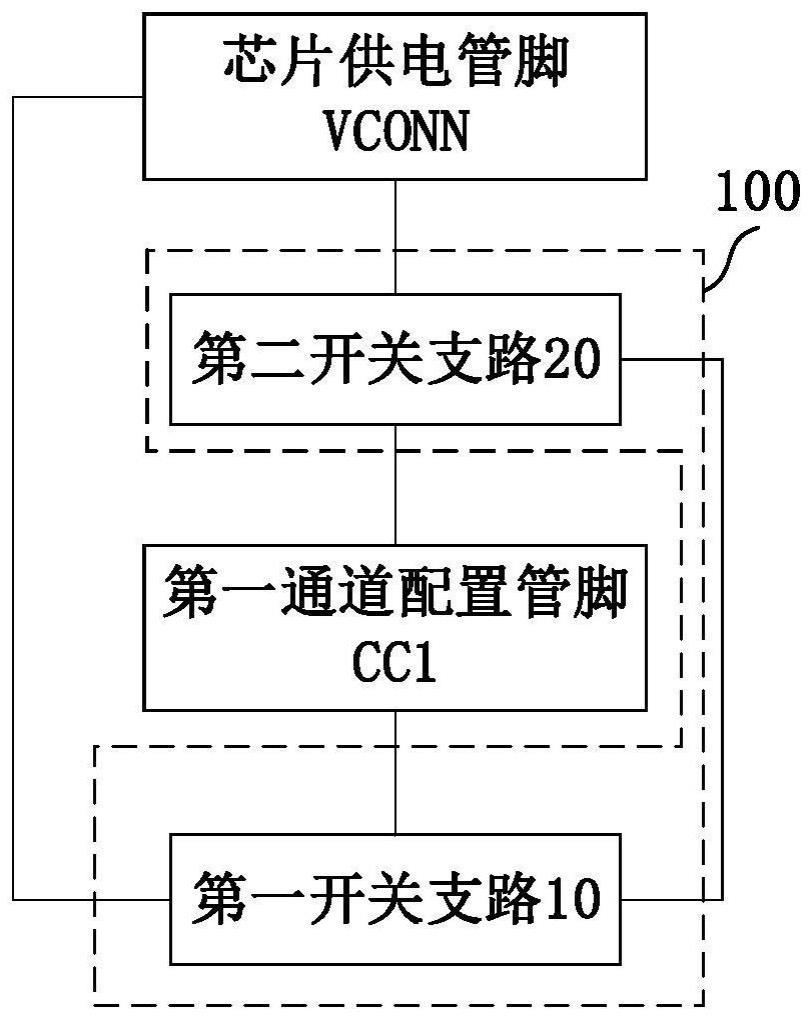

2、为实现上述目的,第一方面,本技术提供一种开关电路,所述开关电路分别与usb接口的芯片供电管脚与第一通道配置管脚连接,所述开关电路包括第一开关支路与第二开关支路;

3、所述第一开关支路分别与所述第一通道配置管脚及所述芯片供电管脚连接,所述第一开关支路用于在所述第一通道配置管脚的电压与所述芯片供电管脚的电压之间的差值大于第一电压阈值时导通,并输出第一电平信号至所述第二开关支路;

4、所述第二开关支路连接于所述芯片供电管脚及所述第一通道配置管脚之间,且所述第二开关支路与所述第一开关支路连接,所述第二开关支路用于在接收到所述第一电平信号时断开所述芯片供电管脚与所述第一通道配置管脚之间的连接。

5、在一种可选的方式中,所述开关电路还与所述usb接口的第二通道配置管脚连接,所述开关电路还包括第三开关支路与第四开关支路:

6、所述第三开关支路分别与所述第二通道配置管脚及所述芯片供电管脚连接,所述第三开关支路用于在所述第二通道配置管脚的电压与所述芯片供电管脚的电压之间的差值大于所述第一电压阈值时导通,并输出所述第一电平信号至所述第四开关支路;

7、所述第四开关支路连接于所述芯片供电管脚及所述第二通道配置管脚之间,且所述第四开关支路与所述第三开关支路连接,所述第四开关支路用于在接收到所述第一电平信号时断开所述芯片供电管脚与所述第二通道配置管脚之间的连接。

8、在一种可选的方式中,所述第一开关支路包括第一电阻、第一开关管、第二开关管、第三开关管与第四开关管;

9、所述第一电阻的第一端与所述第一通道配置管脚连接,所述第一电阻的第二端与所述第一开关管的第二端连接,所述第一开关管的第一端与所述芯片供电管脚连接,所述第一开关管的第三端分别与所述第二开关管的第三端、所述第二开关管的第一端及所述第三开关管的第一端连接,所述第二开关管的第二端及所述第三开关管的第二端均接地,所述第三开关管的第三端与所述第四开关管的第二端连接,所述第四开关管的第一端与第一电压连接,所述第四开关管的第三端与所述第二开关支路连接。

10、在一种可选的方式中,所述第一开关管为pmos管,所述第二开关管为nmos管,所述第三开关管为nmos管,所述第四开关管为nmos管;

11、所述第一开关管的第一端为pmos管的栅极,所述第一开关管的第二端为pmos管的源极,所述第一开关管的第三端为pmos管的漏极;

12、所述第二开关管的第一端为nmos管的栅极,所述第二开关管的第二端为nmos管的源极,所述第二开关管的第三端为nmos管的漏极;

13、所述第三开关管的第一端为nmos管的栅极,所述第三开关管的第二端为nmos管的源极,所述第三开关管的第三端为nmos管的漏极;

14、所述第四开关管的第一端为nmos管的栅极,所述第四开关管的第二端为nmos管的源极,所述第四开关管的第三端为nmos管的漏极。

15、在一种可选的方式中,所述第二开关支路包括第五开关管与第六开关管;

16、所述第五开关管的第二端与所述芯片供电管脚连接,所述第五开关管的第三端与所述第六开关管的第二端连接,所述第六开关管的第三端与所述第一通道配置管脚连接,所述第六开关管的第一端与所述第一开关支路连接。

17、在一种可选的方式中,所述第五开关管为nmos管,所述第六开关管为pmos管;

18、所述第五开关管的第一端为nmos管的栅极,所述第五开关管的第二端为nmos管的源极,所述第五开关管的第三端为nmos管的漏极;

19、所述第六开关管的第一端为pmos管的栅极,所述第六开关管的第二端为pmos管的源极,所述第六开关管的第三端为pmos管的漏极。

20、在一种可选的方式中,所述第三开关支路包括第二电阻、第七开关管、第八开关管、第九开关管与第十开关管;

21、所述第二电阻的第一端与所述第二通道配置管脚连接,所述第二电阻的第二端与所述第七开关管的第二端连接,所述第七开关管的第一端与所述芯片供电管脚连接,所述第七开关管的第三端分别与所述第八开关管的第三端、所述第八开关管的第一端及所述第九开关管的第一端连接,所述第八开关管的第二端及所述第九开关管的第二端均接地,所述第九开关管的第三端与所述第十开关管的第二端连接,所述第十开关管的第一端与第一电压连接,所述第十开关管的第三端与所述第四开关支路连接。

22、在一种可选的方式中,所述第七开关管为pmos管,所述第八开关管为nmos管,所述第九开关管为nmos管,所述第十开关管为nmos管;

23、所述第七开关管的第一端为pmos管的栅极,所述第七开关管的第二端为pmos管的源极,所述第七开关管的第三端为pmos管的漏极;

24、所述第八开关管的第一端为nmos管的栅极,所述第八开关管的第二端为nmos管的源极,所述第八开关管的第三端为nmos管的漏极;

25、所述第九开关管的第一端为nmos管的栅极,所述第九开关管的第二端为nmos管的源极,所述第九开关管的第三端为nmos管的漏极;

26、所述第十开关管的第一端为nmos管的栅极,所述第十开关管的第二端为nmos管的源极,所述第十开关管的第三端为nmos管的漏极。

27、在一种可选的方式中,所述第四开关支路包括第十一开关管与第十二开关管;

28、所述第十一开关管的第二端与所述芯片供电管脚连接,所述第十一开关管的第三端与所述第十二开关管的第二端连接,所述第十二开关管的第三端与所述第二通道配置管脚连接,所述第十二开关管的第一端与所述第三开关支路连接。

29、在一种可选的方式中,所述第十一开关管为nmos管,所述第十二开关管为pmos管;

30、所述第十一开关管的第一端为nmos管的栅极,所述第十一开关管的第二端为nmos管的源极,所述第十一开关管的第三端为nmos管的漏极;

31、所述第十二开关管的第一端为pmos管的栅极,所述第十二开关管的第二端为pmos管的源极,所述第十二开关管的第三端为pmos管的漏极。

32、第二方面,本技术提供一种芯片,包括如上所述的开关电路。

33、本技术的有益效果是:本技术提供的开关电路分别与usb接口的芯片供电管脚与第一通道配置管脚连接。开关电路包括第一开关支路与第二开关支路。当usb type-c接口的第一通道配置管脚和总线电源管脚短路,导致第一通道配置管脚的电压过高时,第一通道配置管脚的电压与芯片供电管脚的电压之间的差值大于第一电压阈值。此时,第一开关支路导通,并输出第一电平信号至第二开关支路。继而,第二开关支路断开芯片供电管脚与第一通道配置管脚之间的连接。从而,当该开关电路应用于电子标记芯片时,由于芯片供电管脚与第一通道配置管脚之间的连接被断开,电流无法经经电子标记芯片的cc管脚倒灌到vconn端,有利于对vconn端的供电电源和芯片的vconn管脚起到保护作用。

- 还没有人留言评论。精彩留言会获得点赞!