半导体存储器件的制作方法

本公开涉及一种半导体存储器件。

背景技术:

1、随着半导体器件变得更加高度集成,单独的电路图案可以更加小型化以便在相同的区域中实现更多的半导体器件。例如,随着半导体器件集成度的增加,可以减少半导体器件的组件的设计规则。

2、随着在高度缩小的半导体器件中临界尺寸(cd)变小,对新集成技术进行了各种研究。

技术实现思路

1、本公开的各方面是为了提供一种具有改进的电特性和可靠性的半导体存储器件。

2、然而,本公开的各方面不限于本文所阐述的那些。通过参照下面给出的本公开的详细描述,本公开的上述和其他方面对于本公开所属领域的普通技术人员而言将变得更加清楚。

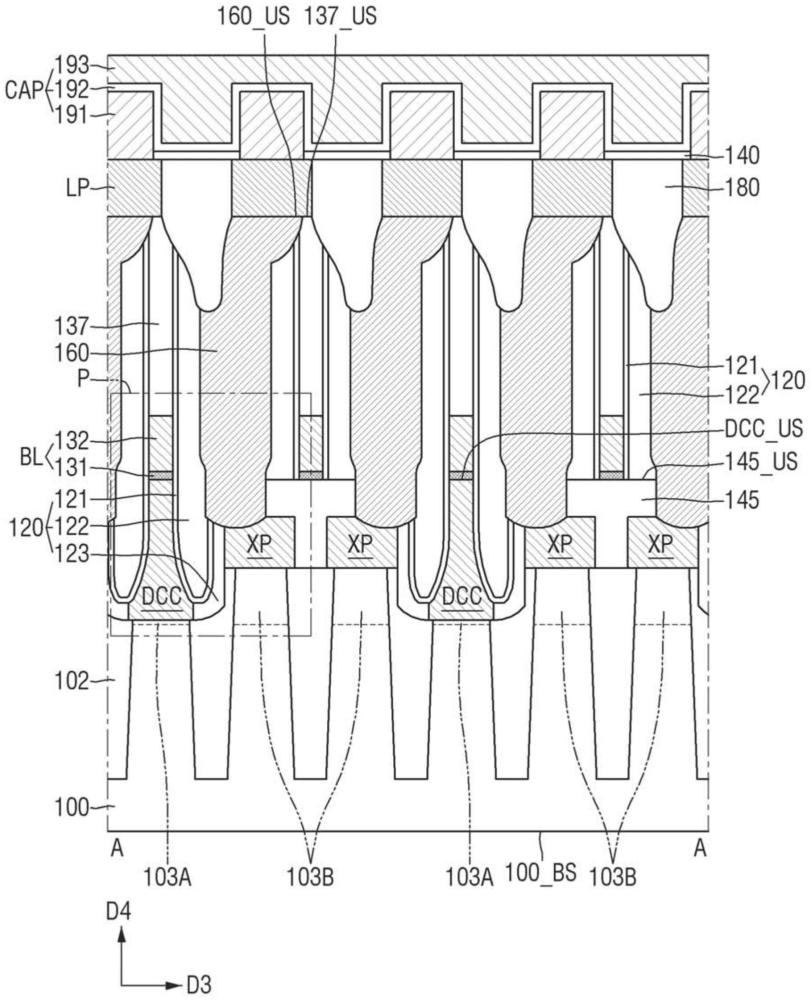

3、根据本公开的一些实施例,提供了一种半导体存储器件,包括:衬底;衬底中的隔离层;有源区,沿第一方向在隔离层中延伸,其中,有源区包括第一区域和第一区域的相对侧处的第二区域;位线,在衬底上沿与第一方向相交的第二方向延伸,其中,位线与有源区相交;在衬底与位线之间的位线接触部,其中,位线接触部电连接到第一区域;位线间隔物,包括在位线的侧表面上且在位线接触部的侧表面上的位线间隔物;衬底上在位线间隔物的横向侧上的节点焊盘,其中,节点焊盘电连接到第二区域;以及存储接触部,包括在节点焊盘上且在位线间隔物的侧表面上的存储接触部,其中,存储接触部包括沿与第一方向和第二方向相交的第三方向具有第一宽度的第一部分、以及相对于衬底的底表面在第一部分下方的第二部分,并且其中,第二部分电连接到节点焊盘并且沿第三方向具有第二宽度,该第二宽度不同于第一宽度。

4、根据本公开的一些实施例,提供了一种半导体存储器件,包括:衬底;隔离层中的多个有源区,其中,多个有源区沿第一方向延伸,并且其中,多个有源区均包括第一区域和第一区域的相对侧上的第二区域;位线,在衬底上沿与第一方向相交的第二方向延伸,其中,位线与多个有源区相交;节点焊盘,在衬底上沿第三方向与位线间隔开,并且电连接到有源区的第二区域,其中,第三方向与第一方向和第二方向相交;以及节点焊盘上的存储接触部,在第三方向上与位线间隔开,其中,存储接触部包括:第一侧表面,沿与第一方向、第二方向和第三方向相交的第四方向延伸,其中,第二方向、第三方向和第四方向彼此垂直相交,并且其中,第一方向以小于90度的角度与第三方向相交;倾斜表面,相对于衬底的底表面在第一侧表面下方,其中,倾斜表面从第一侧表面弯折或弯曲;以及第二侧表面,相对于衬底的底表面在倾斜表面下方,其中,第二侧表面从倾斜表面弯折或弯曲,并且其中,第一侧表面与第二侧表面彼此不重叠。

5、根据本公开的一些实施例,提供了一种半导体存储器件,包括:衬底,包括隔离层中沿第一方向延伸的多个有源区,其中,多个有源区均包括第一区域和第一区域的相对侧处的第二区域;位线,在衬底上沿与第一方向相交的第二方向延伸,其中,位线与多个有源区相交;在衬底与位线之间的位线接触部,其中,位线接触部电连接到有源区的第一区域;位线间隔物,包括在位线的侧表面和位线接触部的侧表面上的位线间隔物;衬底上在位线间隔物的横向侧上的节点焊盘,其中,节点焊盘电连接到有源区的第二区域;存储接触部,包括在节点焊盘上且在位线间隔物的侧表面上并电连接到节点焊盘的存储接触部;以及围栏图案,沿第二方向在存储接触部之间以及沿与第一方向和第二方向相交的第三方向在位线间隔物之间,其中,存储接触部包括:第一侧表面,沿与第一方向、第二方向和第三方向相交的第四方向延伸,其中,第二方向、第三方向和第四方向彼此垂直相交,并且其中,第一方向以小于90度的角度与第三方向相交;倾斜表面,相对于衬底的底表面在第一侧表面下方,其中,倾斜表面从第一侧表面弯折或弯曲;以及第二侧表面,相对于衬底的底表面在倾斜表面下方,其中,第二侧表面从倾斜表面弯折或弯曲,其中,第一侧表面和第二侧表面彼此不重叠,其中,存储接触部和节点焊盘均包括金属材料,并且其中,在沿第二方向截取的截面图中,存储接触部的底表面为线性并且围栏图案的底表面为圆形。

6、应当注意,本公开的效果不限于上述那些,并且根据以下描述,本公开的其他效果将是清楚的。

技术特征:

1.一种半导体存储器件,包括:

2.根据权利要求1所述的半导体存储器件,其中,所述第一宽度大于所述第二宽度。

3.根据权利要求1所述的半导体存储器件,其中,所述位线的所述侧表面与所述第一部分的侧表面之间在所述第三方向上的第一距离大于所述位线的所述侧表面与所述第二部分的侧表面之间在所述第三方向上的第二距离。

4.根据权利要求1所述的半导体存储器件,其中,所述存储接触部和所述节点焊盘均不包括硅化物。

5.根据权利要求1所述的半导体存储器件,其中,所述存储接触部和所述节点焊盘均包括金属材料。

6.根据权利要求1所述的半导体存储器件,其中,相对于所述衬底的底表面,所述位线接触部的底表面低于所述节点焊盘的底表面。

7.根据权利要求1所述的半导体存储器件,还包括沿所述第二方向在所述存储接触部之间及沿所述第三方向在所述位线间隔物之间的围栏图案,

8.根据权利要求1所述的半导体存储器件,其中,在沿所述第二方向截取的截面图中,所述存储接触部的底表面为线形。

9.根据权利要求1所述的半导体存储器件,其中,所述存储接触部还包括所述第一部分与所述第二部分之间的倾斜部分,所述倾斜部分由所述第一部分和所述第二部分限定,并且具有倾斜的侧表面。

10.根据权利要求1所述的半导体存储器件,其中,所述位线接触部在距所述衬底的底表面的第一高度处具有第三宽度,并且在相对于所述衬底的底表面低于所述第一高度的第二高度处具有第四宽度,并且

11.根据权利要求1所述的半导体存储器件,还包括:

12.根据权利要求1所述的半导体存储器件,其中,相对于所述衬底的底表面,所述位线间隔物向下延伸得比所述节点焊盘的底表面更远。

13.一种半导体存储器件,包括:

14.根据权利要求13所述的半导体存储器件,还包括:

15.根据权利要求13所述的半导体存储器件,其中,所述第一侧表面与所述位线的侧表面之间在所述第三方向上的第一距离小于所述第二侧表面与所述位线的所述侧表面之间在所述第三方向上的第二距离。

16.根据权利要求13所述的半导体存储器件,其中,所述存储接触部包括具有所述第一侧表面的第一部分,

17.根据权利要求16所述的半导体存储器件,其中,所述存储接触部还包括沿所述第一侧表面延伸但不沿所述第二侧表面延伸的钝化层。

18.根据权利要求13所述的半导体存储器件,其中,所述存储接触部和所述节点焊盘均包括金属材料。

19.根据权利要求13所述的半导体存储器件,其中,在沿所述第二方向截取的截面图中,所述存储接触部的底表面为线形。

20.一种半导体存储器件,包括:

技术总结

提供一种半导体存储器件,包括:有源区,在单元隔离层中延伸,其中,有源区包括第一区域和第二区域;位线,与有源区相交;在衬底与位线之间的位线接触部,其中,位线接触部电连接到第一区域;位线间隔物,在位线和位线接触部的侧表面上;在位线间隔物的横向侧上的节点焊盘,其中,节点焊盘电连接到第二区域;存储接触部,在节点焊盘上和位线间隔物的侧表面上,其中,存储接触部包括具有第一宽度的第一部分和具有第二宽度的第二部分,第二宽度不同于第一宽度。

技术研发人员:崔祐荣,金熙中,成祉勋,崔佳银,宣潒珪

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!