一种提升SRAM比特率的方法与流程

本发明涉及半导体,特别是涉及一种提升sram比特率的方法。

背景技术:

1、随着半导体技术尺寸的按比例缩小,vdd也会降低功率,这导致snm(静态噪声边限,读取干扰边限的关键指标)越来越小。

2、比特率的定义(sram单元比率)=ion_pd/ion_pg,比特率越大,snm越大。传统的比特率调整方法:(1)有源区aa的cd调整,如pg(传输门晶体管)的cd与pd(下拉管)的cd;(2)在pg区域施加单元电压vt以减小lon-_pg。固定fin的数量和纳米限额数量以提升比特率。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种提升sram比特率的方法,用于解决现有技术中器件尺寸等比例缩小导致静态噪声边限变小的问题。

2、为实现上述目的及其他相关目的,本发明提供一种提升sram比特率的方法,至少包括:

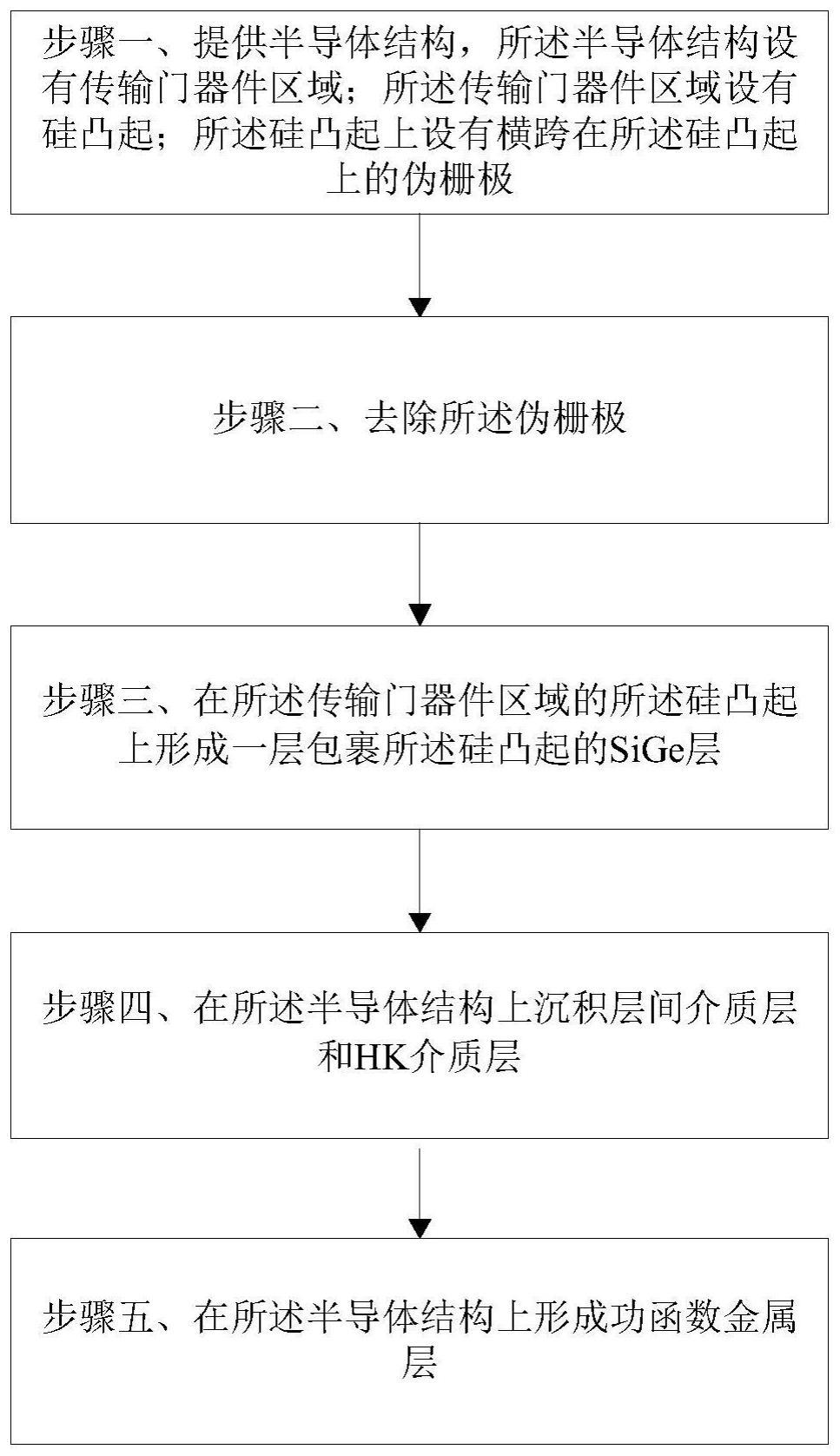

3、步骤一、提供半导体结构,所述半导体结构设有传输门器件区域;所述传输门器件区域设有硅凸起;所述硅凸起上设有横跨在所述硅凸起上的伪栅极;

4、步骤二、去除所述伪栅极;

5、步骤三、在所述传输门器件区域的所述硅凸起上形成一层包裹所述硅凸起的sige层;

6、步骤四、在所述半导体结构上沉积层间介质层和hk介质层;

7、步骤五、在所述半导体结构上形成功函数金属层。

8、优选地,步骤一中的所述伪栅极为多晶硅。

9、优选地,步骤一中的所述硅凸起为设在所述半导体结构的衬底上沿横向排列的条状结构,所述条状结构的长度方向沿纵向。

10、优选地,步骤三中依次通过光刻和刻蚀的方法在所述传输门器件区域的所述硅凸起上形成一层包裹所述硅凸起的sige层。

11、优选地,步骤三中先在所述半导体结构上沉积一层sige,之后通过设有sige图形的光罩,通过曝光和显影将所述sige图形转移至光刻胶上,形成光刻胶图形;之后按照所述光刻胶图形刻蚀所述sige,形成覆盖在所述硅凸起上的sige层。

12、一种提升sram比特率的方法,至少包括:

13、步骤一、提供半导体结构,所述半导体结构设有传输门器件区域;所述传输门器件区域设有纳米线;

14、步骤二、在所述纳米线上形成一层包裹所述纳米线的sige层;

15、步骤三、在所述sige层上形成一层sio层以包裹所述纳米线;

16、步骤四、在所述sio层上形成一层hfo层以及包裹所述纳米线。

17、优选地,步骤一中的所述纳米线为硅纳米线。

18、优选地,步骤二中是通过光刻和刻蚀的方法在所述纳米线上形成一层包裹所述纳米线的sige层。

19、优选地,所述半导体结构是用于形成sram器件。

20、如上所述,本发明的提升sram比特率的方法,具有以下有益效果:本发明在sram器件中,在传输门的finfet结构中的fin结构上形成sige层以包裹fin结构,或者在sram中的纳米线外包裹一层sige层,通过压缩应力减小传输门的迁移率,从而增加比特率和静态噪声边限。

技术特征:

1.一种提升sram比特率的方法,其特征在于,至少包括:

2.根据权利要求1所述的提升sram比特率的方法,其特征在于:步骤一中的所述伪栅极为多晶硅。

3.根据权利要求1所述的提升sram比特率的方法,其特征在于:步骤一中的所述硅凸起为设在所述半导体结构的衬底上沿横向排列的条状结构,所述条状结构的长度方向沿纵向。

4.根据权利要求1所述的提升sram比特率的方法,其特征在于:步骤三中依次通过光刻和刻蚀的方法在所述传输门器件区域的所述硅凸起上形成一层包裹所述硅凸起的sige层。

5.根据权利要求4所述的提升sram比特率的方法,其特征在于:步骤三中先在所述半导体结构上沉积一层sige,之后通过设有sige图形的光罩,通过曝光和显影将所述sige图形转移至光刻胶上,形成光刻胶图形;之后按照所述光刻胶图形刻蚀所述sige,形成覆盖在所述硅凸起上的sige层。

6.一种提升sram比特率的方法,其特征在于,至少包括:

7.根据权利要求6所述的提升sram比特率的方法,其特征在于:步骤一中的所述纳米线为硅纳米线。

8.根据权利要求6所述的提升sram比特率的方法,其特征在于:步骤二中是通过光刻和刻蚀的方法在所述纳米线上形成一层包裹所述纳米线的sige层。

9.根据权利要求1或6所述的提升sram比特率的方法,其特征在于:所述半导体结构是用于形成sram器件。

技术总结

本发明提供一种提升SRAM比特率的方法,提供半导体结构,半导体结构设有传输门器件区域;传输门器件区域设有硅凸起;硅凸起上设有横跨在硅凸起上的伪栅极;去除伪栅极;在传输门器件区域的硅凸起上形成一层包裹硅凸起的SiGe层;在半导体结构上沉积层间介质层和HK介质层;在半导体结构上形成功函数金属层。本发明在SRAM器件中,在传输门的硅凸起结构上形成SiGe层以包裹,或者在SRAM中的纳米线外包裹一层SiGe层,通过压缩应力减小传输门的迁移率,从而增加比特率和静态噪声边限。

技术研发人员:王寅

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!