阵列基板及显示面板的制作方法

本申请涉及显示,具体涉及一种阵列基板及显示面板。

背景技术:

1、相关技术中,液晶面板的像素排列方式主要是stripe架构排列方式和flip架构排列方式。其中,stripe架构排列方式中像素为列反转,一条数据线驱动同一列相同颜色的像素。flip架构排列方式中像素为点反转,一条数据线同时驱动相邻两列中两种颜色的像素,相邻两行薄膜晶体管开口朝向相反。

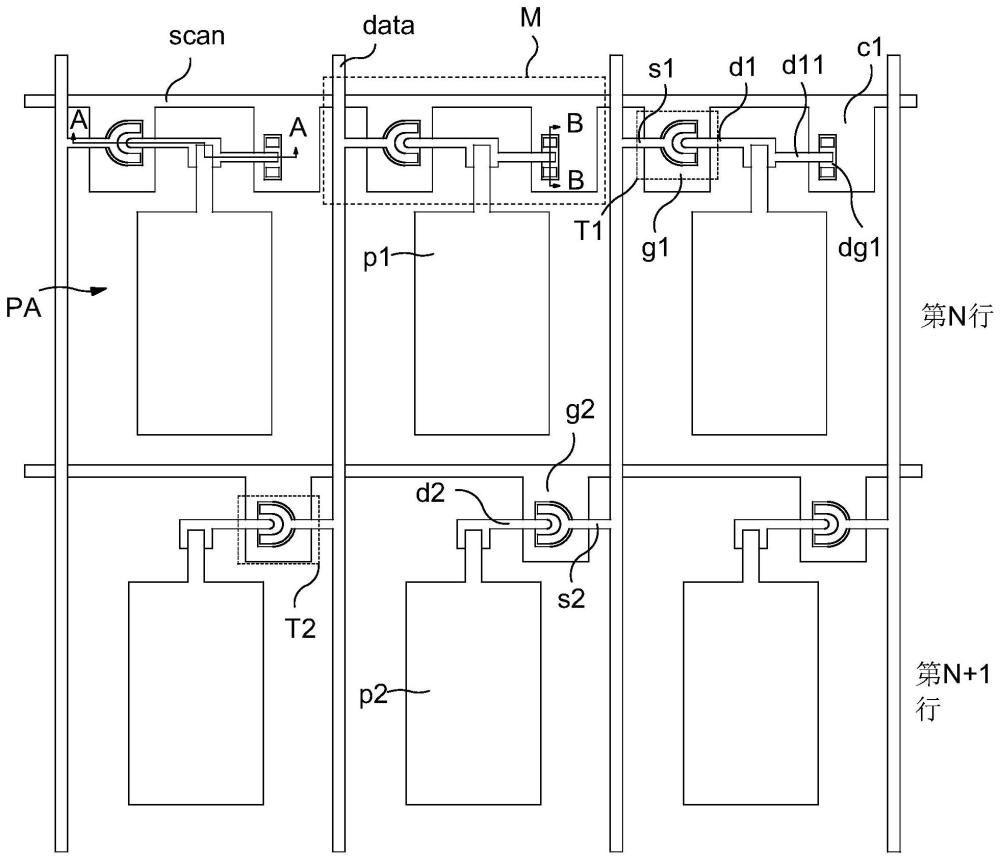

2、如图1所示,在flip架构中,在制备阵列基板时,当制备第二金属层m2相较于第一金属层m1向右偏移时,导致偶数行(左侧)补偿电容变大,奇数行(右侧)的补偿电容变小。相邻两行之间的补偿电容大小不同。

技术实现思路

1、本申请实施例提供一种阵列基板及显示面板,可以提高相邻两行补偿电容的均一性。

2、本申请实施例提供一种阵列基板,其包括:

3、扫描线和数据线,所述扫描线和所述数据线异层设置,所述扫描线和所述数据线交叉设置形成多个像素区;以及

4、像素电极,所述像素电极设置在所述像素区内,所述像素电极包括第一像素电极和第二像素电极;

5、在相邻的两行所述像素电极中,所述第一像素电极设置在第n行,所述第二像素电极设置在第n+1行,n为正整数,所述第一像素电极通过第一薄膜晶体管连接于所述数据线,所述第二像素电极通过第二薄膜晶体管连接于所述数据线;

6、在相邻的两行所述像素区中,一所述数据线同时连接所述第一薄膜晶体管的输入极和所述第二薄膜晶体管的输入极,所述第一薄膜晶体管和所述第二薄膜晶体管位于一所述数据线的相对侧,所述第一薄膜晶体管的输出极与所述第一薄膜晶体管的栅极重叠面积小于所述第二薄膜晶体管的输出极与所述第二薄膜晶体管的栅极重叠面积;

7、所述第一薄膜晶体管的输出极的延伸段与所述扫描线的凸出段重叠形成补偿电容,所述延伸段和所述凸出段之间设置有垫高部,所述垫高部与所述延伸段的部分重叠设置。

8、可选的,在本申请的一些实施例中,所述第一薄膜晶体管的输出极包括依次连接的输出主体段、第一连接段和所述延伸段,所述第一连接段连接于所述第一像素电极,所述延伸段连接于所述第一连接段远离所述输出主体段的一侧,所述第一薄膜晶体管还包括有源部,所述输出主体段的部分层叠设置在所述有源部上,所述垫高部和所述有源部同层且间隔设置。

9、可选的,在本申请的一些实施例中,所述第一薄膜晶体管的输入极包括第二连接段、中间段和第一侧段,所述第二连接段的一端连接于所述数据线,所述第二连接段的另一端连接于所述中间段,所述中间段与所述输出主体段的端部相对设置,所述第一侧段连接于所述中间段的一侧且与所述输出主体段的一侧面相对设置;

10、所述阵列基板还包括与所述垫高部重叠设置的第一冗余部,所述第一冗余部与所述延伸段同层且间隔设置,所述第一冗余部与所述延伸段的一侧面相对设置。

11、可选的,在本申请的一些实施例中,所述第一薄膜晶体管的输入极还包括第二侧段,所述第二侧段连接于所述中间段的另一侧且与所述输出主体段的另一侧面相对设置,所述阵列基板还包括与所述垫高部重叠设置的第二冗余部,所述第二冗余部与所述延伸段同层且间隔设置,所述第二冗余部与所述延伸段的另一侧面相对设置。

12、可选的,在本申请的一些实施例中,所述垫高部分别与所述第一冗余部、所述延伸段和所述第二冗余部绝缘设置。

13、可选的,在本申请的一些实施例中,所述阵列基板包括基板、第一绝缘层、第二绝缘层、第三绝缘层,所述扫描线、所述第一薄膜晶体管的栅极同层设置在所述基板上,所述第一绝缘层覆盖所述扫描线和所述第一薄膜晶体管的栅极,所述有源部和所述垫高部设置在所述第一绝缘层上,所述第二绝缘层覆盖所述有源部和所述垫高部,所述数据线、所述第一薄膜晶体管的输入极和所述输出极、所述第一冗余部和所述第二冗余部设置在所述第二绝缘层上,所述第三绝缘层覆盖所述数据线、所述第一薄膜晶体管的输入极和所述输出极、所述第一冗余部和所述第二冗余部,所述像素电极设置在所述第三绝缘层上。

14、可选的,在本申请的一些实施例中,所述垫高部分别与所述第一冗余部、所述延伸段和所述第二冗余部连接设置。

15、可选的,在本申请的一些实施例中,所述阵列基板包括基板、第一绝缘层和第二绝缘层,所述扫描线、所述第一薄膜晶体管的栅极同层设置在所述基板上,所述第一绝缘层覆盖所述扫描线和所述第一薄膜晶体管的栅极,所述有源部和所述垫高部设置在所述第一绝缘层上,所述第一薄膜晶体管的输入极和所述输出极连接设置在所述有源部上,所述输出极的所述延伸段、所述第一冗余部和所述第二冗余部连接设置在所述垫高部上,所述第二绝缘层覆盖所述数据线、所述第一薄膜晶体管的输入极和所述输出极、所述第一冗余部和所述第二冗余部,所述像素电极设置在所述第二绝缘层上。

16、可选的,在本申请的一些实施例中,所述输出主体段的延伸方向平行或重合于所述延伸段的延伸方向。

17、可选的,在本申请的一些实施例中,所述有源部的边界到所述第一薄膜晶体管的栅极的边界的距离为第一距离,所述垫高部的边界到所述凸出段的边界的距离为第二距离,所述第一距离等于所述第二距离。

18、可选的,在本申请的一些实施例中,在所述扫描线的延伸方向上,所述垫高部具有第一宽度,所述有源部具有第二宽度,所述有源部与所述输出主体段重叠的部分具有第三宽度,所述第一宽度大于或等于所述第三宽度且小于或等于所述第二宽度。

19、相应的,本申请实施例还提供一种显示面板,其包括如上述任意一项实施例所述的阵列基板。

20、本申请实施例的阵列基板采用flip架构,在相邻的两行像素区中,在较小电容的一行像素区中设置补偿电容,使得相邻的两行像素区的电容趋于一致;另外,采用垫高部设置在第一薄膜晶体管的输出极的延伸段和扫描线的凸出段之间,垫高部与延伸段的部分重叠设置以垫高第一薄膜晶体管的输出极的延伸段,使得延伸段的地势跟第一薄膜晶体管的输出极的输出主体段的地势趋于一致,当在蚀刻形成第一薄膜晶体管的输出极时,蚀刻液在上述两个相似地形处具有相近的蚀刻效果,以降低第一薄膜晶体管的输出极延伸段的宽度偏小的风险,从而降低了补偿电容偏小的风险。

技术特征:

1.一种阵列基板,其特征在于,包括:

2.根据权利要求1所述的阵列基板,其特征在于,所述第一薄膜晶体管的输出极包括依次连接的输出主体段、第一连接段和所述延伸段,所述第一连接段连接于所述第一像素电极,所述延伸段连接于所述第一连接段远离所述输出主体段的一侧,所述第一薄膜晶体管还包括有源部,所述输出主体段的部分层叠设置在所述有源部上,所述垫高部和所述有源部同层且间隔设置。

3.根据权利要求2所述的阵列基板,其特征在于,所述第一薄膜晶体管的输入极包括第二连接段、中间段和第一侧段,所述第二连接段的一端连接于所述数据线,所述第二连接段的另一端连接于所述中间段,所述中间段与所述输出主体段的端部相对设置,所述第一侧段连接于所述中间段的一侧且与所述输出主体段的一侧面相对设置;

4.根据权利要求3所述的阵列基板,其特征在于,所述第一薄膜晶体管的输入极还包括第二侧段,所述第二侧段连接于所述中间段的另一侧且与所述输出主体段的另一侧面相对设置,所述阵列基板还包括与所述垫高部重叠设置的第二冗余部,所述第二冗余部与所述延伸段同层且间隔设置,所述第二冗余部与所述延伸段的另一侧面相对设置。

5.根据权利要求4所述的阵列基板,其特征在于,所述垫高部分别与所述第一冗余部、所述延伸段和所述第二冗余部绝缘设置。

6.根据权利要求5所述的阵列基板,其特征在于,所述阵列基板包括基板、第一绝缘层、第二绝缘层、第三绝缘层,所述扫描线、所述第一薄膜晶体管的栅极同层设置在所述基板上,所述第一绝缘层覆盖所述扫描线和所述第一薄膜晶体管的栅极,所述有源部和所述垫高部设置在所述第一绝缘层上,所述第二绝缘层覆盖所述有源部和所述垫高部,所述数据线、所述第一薄膜晶体管的输入极和所述输出极、所述第一冗余部和所述第二冗余部设置在所述第二绝缘层上,所述第三绝缘层覆盖所述数据线、所述第一薄膜晶体管的输入极和所述输出极、所述第一冗余部和所述第二冗余部,所述像素电极设置在所述第三绝缘层上。

7.根据权利要求4所述的阵列基板,其特征在于,所述垫高部分别与所述第一冗余部、所述延伸段和所述第二冗余部连接设置。

8.根据权利要求7所述的阵列基板,其特征在于,所述阵列基板包括基板、第一绝缘层和第二绝缘层,所述扫描线、所述第一薄膜晶体管的栅极同层设置在所述基板上,所述第一绝缘层覆盖所述扫描线和所述第一薄膜晶体管的栅极,所述有源部和所述垫高部设置在所述第一绝缘层上,所述第一薄膜晶体管的输入极和所述输出极连接设置在所述有源部上,所述输出极的所述延伸段、所述第一冗余部和所述第二冗余部连接设置在所述垫高部上,所述第二绝缘层覆盖所述数据线、所述第一薄膜晶体管的输入极和所述输出极、所述第一冗余部和所述第二冗余部,所述像素电极设置在所述第二绝缘层上。

9.根据权利要求1-8任意一项所述的阵列基板,其特征在于,所述输出主体段的延伸方向平行或重合于所述延伸段的延伸方向。

10.根据权利要求2-8任意一项所述的阵列基板,其特征在于,所述有源部的边界到所述第一薄膜晶体管的栅极的边界的距离为第一距离,所述垫高部的边界到所述凸出段的边界的距离为第二距离,所述第一距离等于所述第二距离。

11.根据权利要求2-8任意一项所述的阵列基板,其特征在于,在所述扫描线的延伸方向上,所述垫高部具有第一宽度,所述有源部具有第二宽度,所述有源部与所述输出主体段重叠的部分具有第三宽度,所述第一宽度大于或等于所述第三宽度且小于或等于所述第二宽度。

12.一种显示面板,其特征在于,包括如权利要求1-11任意一项所述的阵列基板。

技术总结

本申请实施例公开了一种阵列基板及显示面板,阵列基板采用flip架构,在相邻的两行像素区中,在较小电容的一行像素区中设置补偿电容,使得相邻的两行像素区的电容趋于一致;另外,采用垫高部设置在第一薄膜晶体管的输出极的延伸段和扫描线的凸出段之间,垫高部与延伸段的部分重叠设置以垫高第一薄膜晶体管的输出极的延伸段,使得延伸段的地势跟第一薄膜晶体管的输出极的输出主体段的地势趋于一致,当在蚀刻形成第一薄膜晶体管的输出极时,蚀刻液在上述两个相似地形处具有相近的蚀刻效果,以降低第一薄膜晶体管的输出极延伸段的宽度偏小的风险,从而降低了补偿电容偏小的风险。

技术研发人员:陈亚妮,湛志明

受保护的技术使用者:惠州华星光电显示有限公司

技术研发日:

技术公布日:2024/2/8

- 还没有人留言评论。精彩留言会获得点赞!