一种高精度ADC的后台校准方法

本发明属于电子电路,具体的说,涉及一种高精度adc的后台校准方法。

背景技术:

1、高速(≥1m)高精度(≥16b)模数转换器adc在医疗成像领域需求较大。良好的图像质量需要adc极低的积分非线性和低噪声,而快速的采样率提高了通道密度,从而降低了成本。受益于较低的功耗、较快的翻转速度,两步式逐次逼近寄存器(sar)模数转换器(adc)成为了高速高精度奈奎斯特adc的首选。两步式sar的工作原理主要是电容式数模转换器(cdac)的充放电以及级间增益放大器对余量的放大,工艺引起的电容误差和放大器的增益误差会极大影响sar adc的精度,因此研究校准算法来消除以上两种误差是十分必要的。而随着数字工艺的发展,数字电路在密度、速度、集成度获得了很大的优势。因此数字电路的校准算法成为了一大研究热点。

2、目前现有的两步式sar adc大部分进行的都是高位电容的校准。2014年,adi的alan bannon等人提出了一次性的高低位电容校准[1],并利用电容注入的方式提升adc的差分非线性dnl、积分非线性inl性能,最后在180nm工艺下实现了5m/s采样速率,98.6信噪失真比(sndr),0.4ppm的dnl与2ppm的inl。2017年,adi的derek hummerston等人基于[1]提出了事件驱动的输入开关[2],并解决了输入开关电阻非线性问题,将fom(figure ofmerit)值提高到179.9db ,thd达到107db。2018年,adi的hongxing li等人引入“簇间分裂电容阵列”概念[3],通过洗牌器控制簇间电容的交换进行高位电容的校准,且校准性能与输入信号无关,在16k点数内收敛,sndr为101.5db,inl缩小至0.25ppm。2019年,来自俄勒冈州立大学的ahmed elshater等人利用低阈值电压(lvt)和高阈值电压(hvt)提出了双死区输出级的ring amp[4],降低了偏置电压的敏感度,极大增大了ring amp的稳定性和线性度,在15m采样率下,sndr达到90.8db,fom值达到179.7db。2022年,adi的jespersteensgaard等人在[1]的基础上运用零阶误差整形、ring amp两次对称放大[5]等技术进一步提升了sar adc的性能,其sndr达到105.3db,fom值达到186.0db。2023年,俄勒冈州立大学的manxin li等人提出了有预测能力的片内输入缓冲器[6],并进行了前台校准,在12m采样率下对4m信号进行采样,sndr达到91.3db。

3、参考文献

4、[1] a. bannon, c. p. hurrell, d. hummerston and c. lyden, "an 18 b 5ms/s sar adc with 100.2 db dynamic range," proc. vlsi, pp. 1-2, jun. 2014.

5、[2] d. hummerston and p. hurrell, "an 18-bit 2ms/s pipelined sar adcutilizing a sampling distortion cancellation circuit with −107db thd at100khz," proc. vlsi, pp. 280-281, jun. 2017.

6、[3] h. li, m. maddox, m. c. w. coin, w. buckley, d. hummerston and n.naeem, "a signal-independent background-calibrating 20b 1ms/s sar adc with0.3ppm inl,", isscc dig. tech. papers, pp. 242-244, feb. 2018.

7、[4] a. elshater et al., "a 10-mw 16-b 15-ms/s two-step sar adc with95-db dr using dual-deadzone ring amplifier," ieee j. solid-state circuits,pp. 3410-3420, dec. 2019.

8、[5] j. steensgaard, r. reay, r. perry, d. thomas, g. tu and g.reitsma, "a 24b 2ms/s sar adc with 0.03ppm inl and 106.3db dr in 180nm cmos," isscc dig. tech. papers, pp. 168-170, feb. 2022.

9、[6] m. li, c.y. lee, a. elshater, y. miyahara, k. sobue, k. tomioka,and u. moon, "a rail-to-rail 12ms/s 91.3db sndr 94.1db dr two-step sar adcwith integrated input buffer using predictive level-shifting," isscc dig. tech. papers, pp. 172-173, feb. 2023.

技术实现思路

1、针对现有技术的不足,本发明的目的在于公开一种应用于两步式流水线结构的pipeline-sar的高精度adc的后台校准算法。其高位sar采用簇间交换和簇内交换的思想,可将电容误差占主导的高位电容误差完全消除掉。放大器采用注入技术,利用最小均方lms(least mean square)迭代,成功将放大器误差收敛到0.1%。低位电容也采取了自注入校准模式,既能消除低位电容误差,还能进一步提升高位电容和放大器倍数的收敛精度。最终,在tsmc180nm工艺下,数字电路功耗仅为1.55mw,校准点数控制在8k以内。相比其他校准算法,本发明以更小的功耗获得了更快的校准速度。

2、本发明的技术方案具体介绍如下。

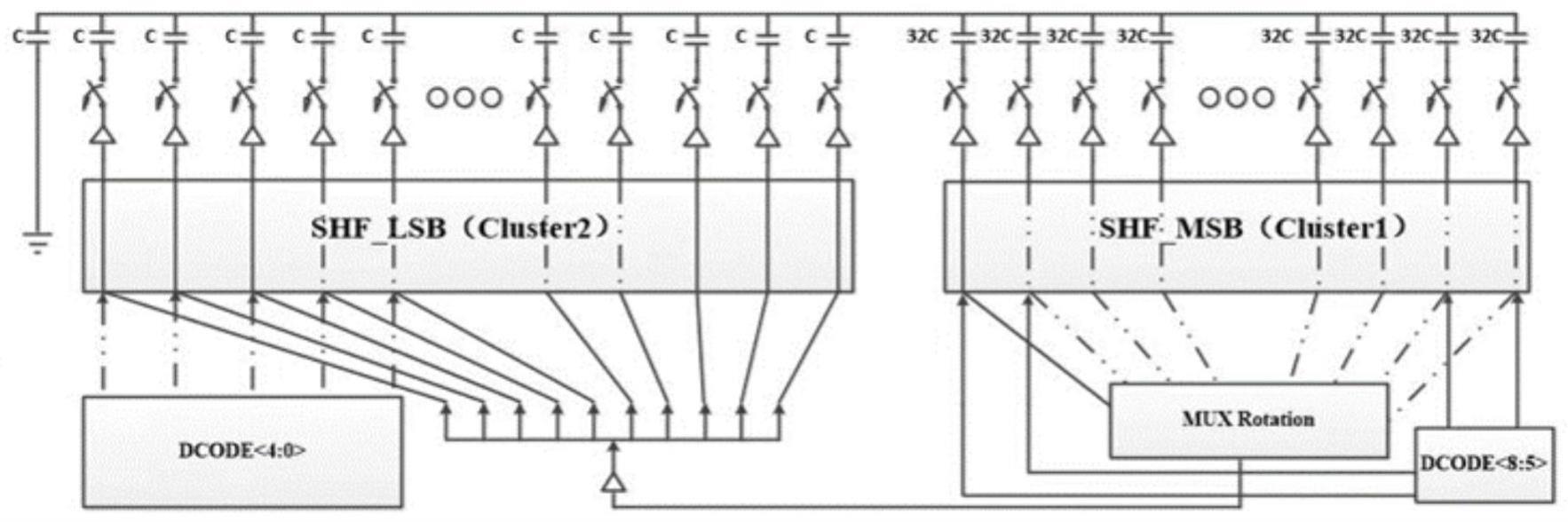

3、一种高精度adc的后台校准方法,其采用pipeline-sar结构,内部电路包括高位sar校准、放大器校准、低位sar校准三部分,高位sar校准时序和放大器校准时序相同,高位sar校准和放大器校准均依赖于低位sar的转换结果,这三部分得到校准信息后迭代各自的系数,利用校准后的系数得到更准确的数字输出;其中:高位sar中的高位电容阵列划分为互不相关的两簇簇1和簇2,簇1为高位msb(most significant bit,最高有效位)簇,簇2为高位lsb(least significant bit,最低有效位))簇,高位sar校准时注入簇间交换和簇内交换的余量,放大器校准时取高位最后一位对应的电容取反注入,在高位电容阵列的簇2中选取若干个电容进行切换对余量注入一个值,低位sar顶板采样,采用自注入的校准。

4、本发明中,前段采样引入mini-adc以提高高位sar转换速度。

5、本发明中,簇1和簇2的伪随机数生成模块中采用顺序循环。

6、本发明中,高位sar校准时,第一次转换为无注入的正常转换,第二次转换通过高位电容阵列的切换对余量注入一个值,经过放大器放大,低位转换从而得到高位电容信息,其注入的是簇间交换和簇内交换的余量;高位sar中,当簇2中每位为全1或者全0时,簇2中所有电容形成一个整体,与簇1中一个特定电容进行簇间交换,簇间交换注入的特定电容寻找方式采取倒叙寻找,挑选最大序号电容。

7、本发明中,低位sar在余量上注入一个与低位电容大小相关的值;在进行校准时,第

8、一次转换前注入一个正值,第二次转换前注入一个相等的负值,以此抑制偶数次谐波,这两次转换得到的结果相减除2即为相应电容大小,相加除2即为放大器放大后的余量值;具体实施例中,噪声会降低3db。

9、本发明中,放大器校准时首先高低位进行一次正常转换,随后簇2最低位取反注入,由低位转换得到变化后的余量,放大器前后输入变化为簇2最低位电容的权重,输出变化为低位转换得到余量,二者相除即为放大倍数;为了避免除法增大资源,引入lms(leastmean square)迭代。

10、本发明中,每次采样有两次转换,最后的输出是两次转换的平均值;具体实施例中,精度会有3db的提升。

11、和现有技术相比,本发明的有益效果在于:

12、(1)在伪随机数生成模块中,本算法采用了低功耗的顺序循环,这对数字功耗非常友好。

13、(2)本发明在没有引入冗余电容的情况下实现了簇间校准,没有冗余电容意味着没有动态范围损失、更低的数字模拟功耗以及更快的校准速度。

14、(3)本发明对簇的结构进行了改进,簇的数目缩小为两簇。簇的数目越少,电容误差传递的越快,校准速度则越快。

15、(4)本发明的适用于pipeline-sar的放大器后台校准算法,能在不影响adc工作的情况下,得到的放大器增益与实际值相差在0.1%内,而trimming的最小误差约为3%。

- 还没有人留言评论。精彩留言会获得点赞!