系统、扫描正反器装置以及产生预定义输入或输出的方法与流程

本揭露涉及一种系统、扫描正反器装置以及用于扫描正反器链的方法。

背景技术:

1、当今大部分电子设备依赖于半导体装置或芯片操作。半导体芯片可常常由数个集成电路(integrated circuit;ic)构成。为了使电子设备适当地起作用,ic必须适当地起作用。对ic执行功能性测试确保其按设计操作。

技术实现思路

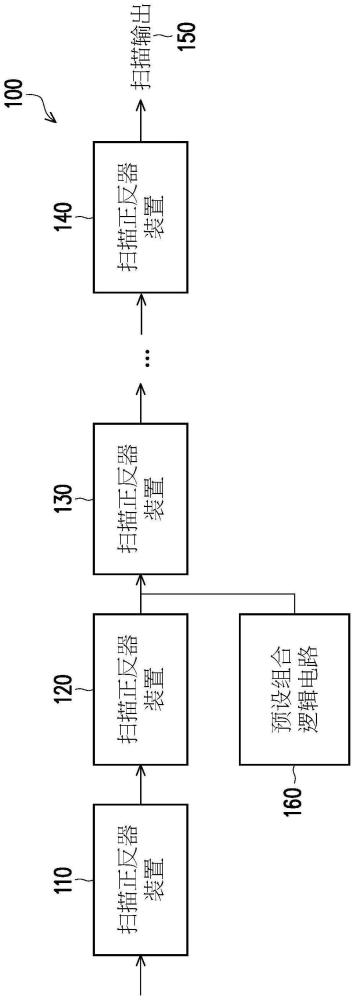

1、在本揭露的一实施例中,系统包括多个正反器装置以及第一预设组合逻辑电路。所述多个正反器装置串联耦接在一起。所述多个正反器装置接收扫描输入信号,基于扫描输入信号而捕获自所述多个正反器装置中的各正反器装置输出的数据,且产生包括经捕获数据的扫描输出信号。第一预设组合逻辑电路耦接至所述多个正反器装置的第一正反器装置。第一预设组合逻辑电路包括多个晶体管。第一预设组合逻辑电路基于所述多个晶体管的选择性操作而覆写及设定至第一正反器装置的扫描输入信号或第一正反器装置的扫描输出信号。

2、在本揭露的一实施例中,扫描正反器装置包括多个晶体管、多个反相器以及预设组合逻辑电路。所述多个晶体管及所述多个反相器互连在一起。所述多个晶体管及所述多个反相器接收扫描输入信号,基于扫描输入信号而捕获自所述多个正反器装置中的各正反器装置输出的数据,且产生包括经捕获数据的扫描输出信号。预设组合逻辑电路耦接至所述多个晶体管的子集或所述多个反相器中的一者。预设组合逻辑电路覆写及预设扫描输入信号或扫描输出信号。

3、在本揭露的一实施例中,产生用于扫描正反器链预设操作模式的预定义输入或输出的方法包括:由互连在一起的多个晶体管接收包括逻辑高或逻辑低的输入信号;基于逻辑高或逻辑低而选择性地操作所述多个晶体管;基于选择性地操作多个晶体管的经捕获数据而产生输出信号;以及由耦接至所述多个晶体管的子集的预设组合逻辑电路覆写待设定成逻辑高或逻辑低的输入信号或输出信号。

技术特征:

1.一种系统,其特征在于,所述系统包括:

2.根据权利要求1所述的系统,其特征在于,所述第一预设组合逻辑电路经配置以在所述第一预设组合逻辑电路耦接于所述第一正反器装置的前端上时覆写及设定所述扫描输入信号,且所述第一预设组合逻辑电路经配置以在所述第一预设组合逻辑电路耦接于所述第一正反器装置的后端上时覆写及设定所述扫描输出信号。

3.根据权利要求1所述的系统,其特征在于,所述多个晶体管包括第一晶体管的集合及第二晶体管的集合,其中所述第一晶体管的集合及所述第二晶体管的集合在共享耦接点处耦接在一起,且所述第一预设组合逻辑电路更包括经由反相器的输入端耦接至所述共享耦接点的所述反相器,所述反相器的输出提供所述扫描输出信号或所述扫描输入信号。

4.根据权利要求1所述的系统,其特征在于,所述多个晶体管包括第一晶体管的集合及第二晶体管的集合,且其中所述第一晶体管的集合在类型上不同于所述第二晶体管的集合,且其中所述第一晶体管的集合中的各者接收第一控制信号、第二控制信号以及输入信号,且所述第二晶体管的集合中的各者接收所述第一控制信号、所述第二控制信号以及所述输入信号。

5.根据权利要求1所述的系统,其特征在于,所述系统更包括第二预设组合逻辑电路,所述第二预设组合逻辑电路在所述第二正反器装置的前端或所述第二正反器装置的后端上耦接至所述多个正反器装置的第二正反器装置,所述第二预设组合逻辑电路经配置以基于所述第二预设组合逻辑电路内的晶体管的选择性操作而覆写及设定至所述第二正反器装置的输入信号或所述第二正反器装置的输出信号。

6.一种扫描正反器装置,其特征在于,所述扫描正反器装置包括:

7.根据权利要求6所述的扫描正反器装置,其特征在于,所述预设组合逻辑电路经配置以在所述预设组合逻辑电路耦接于所述多个晶体管的前端上时覆写及设定所述扫描输入信号,且所述预设组合逻辑电路经配置以在所述预设组合逻辑电路耦接于所述多个晶体管的后端上时覆写及设定所述扫描输出信号。

8.根据权利要求6所述的扫描正反器装置,其特征在于,所述预设组合逻辑电路包括在共享耦接点处耦接在一起的第一晶体管的集合及第二晶体管的集合,且所述预设组合逻辑电路更包括经由反相器的输入端耦接至所述共享耦接点的所述反相器,所述反相器的输出提供所述扫描输出信号或所述扫描输入信号。

9.根据权利要求8所述的扫描正反器装置,其特征在于,所述第一晶体管的集合在类型上不同于所述第二晶体管的集合,且其中所述第一晶体管的集合中的各者接收第一控制信号、第二控制信号以及输入信号,且所述第二晶体管的集合中的各者接收所述第一控制信号、所述第二控制信号以及所述输入信号。

10.一种产生用于扫描正反器链预设操作模式的预定义输入或输出的方法,其特征在于,所述方法用于扫描正反器链预设操作模式,其中所述方法包括:

技术总结

本揭露提供一种系统、扫描正反器装置以及产生预定义输入或输出的方法。系统包括多个正反器装置及第一预设组合逻辑电路。多个正反器装置串联耦接在一起且经配置以接收扫描输入信号,基于扫描输入信号而捕获自多个正反器装置中的各正反器装置输出的数据,且产生包括经捕获数据的扫描输出信号。第一预设组合逻辑电路耦接至多个正反器装置中的第一正反器装置。第一预设组合逻辑电路包括多个晶体管且经配置以基于多个晶体管的选择性操作而覆写及设定至第一正反器装置的扫描输入信号或第一正反器装置的扫描输出信号。

技术研发人员:黎家豪,陈胜雄,林姿颖,高章瑞,简永溱,陈向东

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/3/5

- 还没有人留言评论。精彩留言会获得点赞!