包括包含铁电材料的阻挡电介质层的半导体装置的制作方法

本发明总体上涉及一种半导体装置,更具体地说,涉及一种包括阻挡电介质层的半导体装置。

背景技术:

1、随着半导体芯片的特征尺寸减小,设置在半导体芯片中的电容器器件或晶体管器件的单元器件的尺寸也会减小。然而,尽管单元器件的尺寸减小了,但是构成单元器件的电介质层所需的电容需要超过一定的参考值,以保证单元器件的操作可靠性。因此,正在进行各种研究,以改善应用于单元器件的电介质层的电容特性。

2、作为提高电介质层的电容的代表性方法,已经尝试了一种将高k材料应用于薄厚度的单元器件的电介质层的方法。然而,当电介质层的厚度过度减小时,存在的困难在于,泄漏电流特性和电介质层的击穿电压特性会变差。因此,需要改善的技术来应对这些技术挑战。

技术实现思路

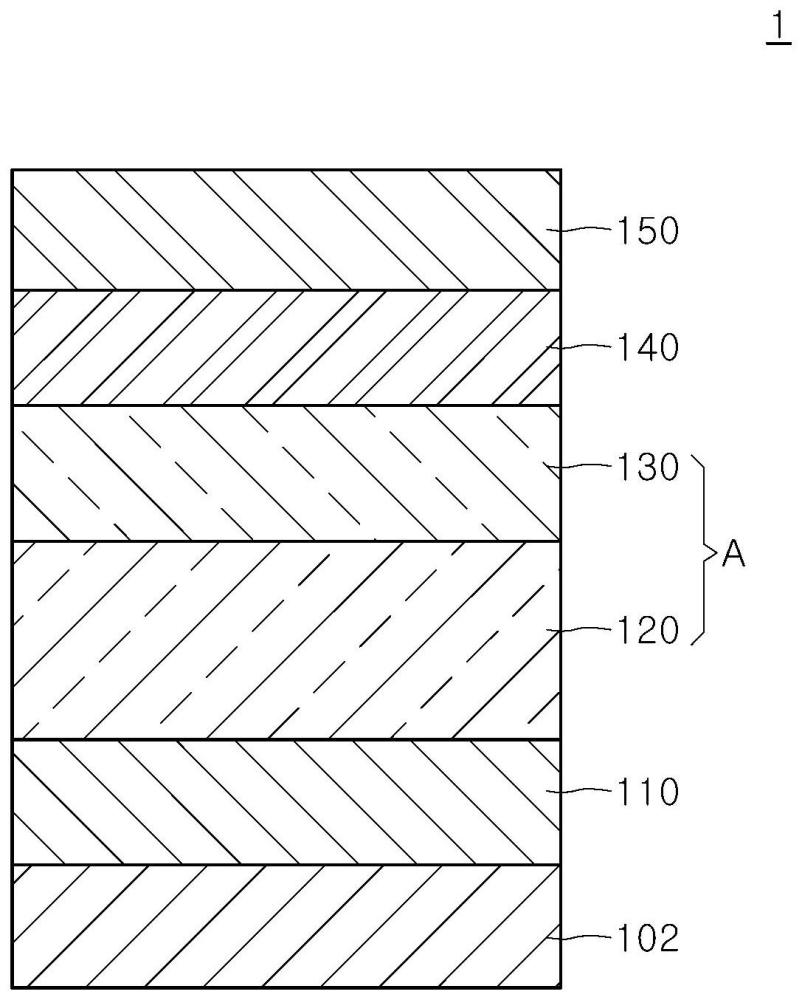

1、根据本公开的一个实施例的半导体装置可以包括:第一电极和第二电极,所述第一电极和第二电极相互间隔开;电容器电介质结构,其设置在所述第一电极与所述第二电极之间;以及阻挡电介质层,其设置在所述第一电极和第二电极中的一个与所述电容器电介质结构之间。所述电容器电介质结构可以包括铁电层和电介质层。所述阻挡电介质层可以包括铁电材料。

2、根据本公开的另一个实施例的半导体装置可以包括:衬底,其包括沟道区;栅电介质结构,其设置在所述沟道区之上;栅电极,其设置在所述栅电介质结构之上;以及阻挡电介质层,其设置在所述沟道区与所述栅电介质结构之间,或者在所述栅电介质结构与所述栅电极之间。所述电容器电介质结构可以包括铁电层和电介质层。所述阻挡电介质层可以包括铁电材料。

3、根据本公开的一个实施例的半导体装置可以包括:衬底;有源层,其设置在所述衬底之上;栅电介质结构,其设置在所述有源层之上;栅电极,其设置为与所述栅电介质结构相邻;以及阻挡电介质层,其设置在所述有源层与所述栅电介质结构之间,或者所述栅电介质结构与所述栅电极之间。所述栅电介质结构可以包括铁电层和电介质层。所述阻挡电介质层可以包括铁电材料。

技术特征:

1.一种半导体装置,其包括:

2.根据权利要求1所述的半导体装置,其中,所述阻挡电介质层接触所述电容器电介质结构。

3.根据权利要求1所述的半导体装置,其中,所述铁电层和所述电介质层在所述第一电极与所述第二电极之间串联电连接。

4.根据权利要求1所述的半导体装置,其中,所述铁电层的电容的绝对值大于所述电介质层的电容的绝对值。

5.根据权利要求1所述的半导体装置,

6.根据权利要求1所述的半导体装置,

7.根据权利要求1所述的半导体装置,

8.根据权利要求1所述的半导体装置,

9.根据权利要求1所述的半导体装置,

10.根据权利要求1所述的半导体装置,其中,所述阻挡电介质层具有1nm至5nm的厚度。

11.根据权利要求1所述的半导体装置,其中,所述阻挡电介质层包括氧化铪锆。

12.根据权利要求1所述的半导体装置,进一步包括掺杂在所述阻挡电介质层中的掺杂剂,

13.根据权利要求1所述的半导体装置,其中,所述铁电层包括氧化铪锆。

14.根据权利要求1所述的半导体装置,进一步包括掺杂在所述铁电层中的掺杂剂,

15.根据权利要求1所述的半导体装置,其中,所述电介质层包括氧化铝、氧化钇、氧化铪、氧化锆和氧化铪锆中的至少一个。

16.根据权利要求1所述的半导体装置,

17.根据权利要求1所述的半导体装置,

18.根据权利要求17所述的半导体装置,进一步包括结晶种子层,其设置在所述第一电极与所述铁电层之间。

19.根据权利要求18所述的半导体装置,其中,所述结晶种子层包括从氧化锆、氧化铪、氮化锆、氮化铪、氧化镁和氧化铌中选择的至少一个。

20.根据权利要求17所述的半导体装置,进一步包括界面绝缘层,其设置在所述阻挡电介质层与所述第二电极之间。

21.一种半导体装置,其包括:

22.根据权利要求21所述的半导体装置,其中,所述栅电介质结构和所述阻挡电介质层设置为相互接触。

23.根据权利要求21所述的半导体装置,其中,所述铁电层和所述电介质层在所述衬底与所述栅电极之间串联电连接。

24.根据权利要求21所述的半导体装置,其中,所述铁电层的电容的绝对值大于所述电介质层的电容的绝对值。

25.根据权利要求21所述的半导体装置,

26.根据权利要求21所述的半导体装置,其中,所述阻挡电介质层的电容的绝对值大于所述栅电介质结构的电容的绝对值,以及

27.根据权利要求21所述的半导体装置,其中,所述阻挡电介质层的电容的绝对值大于所述铁电层的电容的绝对值。

28.根据权利要求21所述的半导体装置,其中,所述阻挡电介质层具有1nm至5nm的厚度。

29.根据权利要求21所述的半导体装置,其中,所述阻挡电介质层包括氧化铪锆。

30.根据权利要求21所述的半导体装置,进一步包括掺杂在所述阻挡电介质层中的掺杂剂,

31.根据权利要求21所述的半导体装置,其中,所述铁电层包括氧化铪锆。

32.根据权利要求21所述的半导体装置,进一步包括掺杂在所述铁电层中的掺杂剂,

33.根据权利要求21所述的半导体装置,其中所述电介质层包括氧化铝、氧化钇、氧化铪、氧化锆和氧化铪锆中的至少一个。

34.根据权利要求21所述的半导体装置,

35.根据权利要求21所述的半导体装置,其中,所述栅电介质结构、所述阻挡电介质层和所述栅电极中的每个的至少一部分设置在从衬底的表面起形成于所述衬底内部的凹陷区域中。

36.根据权利要求35所述的半导体装置,其中,所述栅电介质结构、所述阻挡电介质层和所述栅电极中的每个的顶表面位于比所述衬底的顶表面低的水平上。

37.一种半导体装置,其包括:

38.根据权利要求37所述的半导体装置,其中,所述阻挡电介质层接触所述栅电介质结构。

39.根据权利要求37所述的半导体装置,其中,所述铁电层和所述电介质层在所述有源层与所述栅电极之间串联电连接。

40.根据权利要求37所述的半导体装置,其中,所述铁电层的电容的绝对值大于所述电介质层的电容的绝对值。

41.根据权利要求37所述的半导体装置,

42.根据权利要求37所述的半导体装置,

43.根据权利要求37所述的半导体装置,其中,所述阻挡电介质层的电容的绝对值大于所述铁电层的电容的绝对值。

44.根据权利要求37所述的半导体装置,其中,所述阻挡电介质层具有1nm至5nm的厚度。

45.根据权利要求37所述的半导体装置,其中,所述有源层具有设置在所述衬底之上的鳍结构的形式。

46.根据权利要求37所述的半导体装置,其中,所述有源层具有在与所述衬底的表面实质上垂直的方向上延伸的柱体结构的形式。

47.根据权利要求37所述的半导体装置,其中,所述有源层包括在所述柱体结构内在与所述衬底的表面实质上垂直的方向上延伸的沟道区。

技术总结

本发明提供一种半导体装置。根据实施例的半导体装置包括:第一电极和第二电极,所述第一电极和第二电极相互间隔开;电容器电介质结构,其设置在第一电极与第二电极之间;以及阻挡电介质层,其设置在第一电极和第二电极中的一个与电容器电介质结构之间。电容器电介质结构可以包括铁电层和电介质层。阻挡电介质层可以包括铁电材料。

技术研发人员:徐东益,具元泰

受保护的技术使用者:爱思开海力士有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!