一种小面积高精度电压型R-2R结构DAC

本发明涉及模拟集成电路领域,具体为一种小面积高精度电压型r-2r结构dac。

背景技术:

1、真实世界的信号是模拟信号,而计算机处理的信号是数字信号。dac(数字-模拟转换器)作为连接数字世界和模拟世界的桥梁,将计算机处理好的数字信号转换成所需要的模拟信号。dac在人类社会的方方面面都发挥着不可或缺的作用,从与大众息息相关的消费类电子产品,到关乎国家安全的国防军事等等,随处可见dac的身影。随着集成电路向着高集成度低功耗发展,尤其是现在物联网与可穿戴设备的兴起,在面临多通道高集成度时,更加要求dac面积进一步缩小。所以缩小dac的面积具有现实意义和应用价值。

2、r-2r结构dac利用二进制权重的r-2r电阻网络进行数模转换,电路结构简单,功耗较低。但是传统r-2r结构dac面临两个问题:一是高精度dac面积大,传统r-2r结构dac(对应图1)由低位到高位每一位mos开关管为了匹配,提升dac性能,需要由低位到高位每一位mos开关管宽度w加倍也即面积加倍,当dac位数较高时mos开关管的面积会非常大;二是r-2r结构dac难以实现较高的转换精度,r-2r结构dac由于单位电阻误差和mos开关管导通电阻失配等非理想效应,dac静态性能与动态性能都会受到影响,高精度r-2r结构dac设计面临挑战。

3、现有r-2r结构dac为了解决上述两个问题,虽然已采取多种技术手段提高了部分性能指标,但是会带来其他参数指标性能的降低。例如,通过数字校正技术改善失配下dac的动态性能与提升dac精度,但是需要额外设计数字电路,这增加了设计复杂性、芯片功耗、芯片面积。一些针对r-2r结构dac的模拟校准方法也可以提升dac性能:比如针对mos开关的模拟校准,但是这种校准因为每一位mos开关尺寸不同,需要设计的校准模块也有差异,也即n位dac需要n个校准模块,这同样也增加了设计复杂性、芯片功耗、芯片面积。一些针对r-2r结构dac的模拟校准方法可以减小dac面积:比如在高位与低位中间的某两位间桥接电阻,可以使高位mos开关面积不需要成倍递增也可以达到电阻匹配的效果,但是这种方式下桥接电阻本身会波动,使dac性能不稳定,尤其针对高精度dac,不能满足dac精度要求。

4、此外,r-2r结构dac分为电压型r-2r结构dac与电流型r-2r结构dac,电压型r-2r结构dac相较于电流型r-2r结构dac有多个优点:如电阻网络输出阻抗稳定,对后级运放的稳定性要求不高,开关切换时输出波形毛刺较小。以上优点使得电压型r-2r结构dac适用于多种场合,所以研究电压型r-2r结构dac尤为重要。

技术实现思路

1、针对上述存在的问题或不足,本发明提供了一种小面积高精度电压型r-2r结构dac,以解决现有电压型r-2r结构dac电路面积大、高精度难以实现的问题。

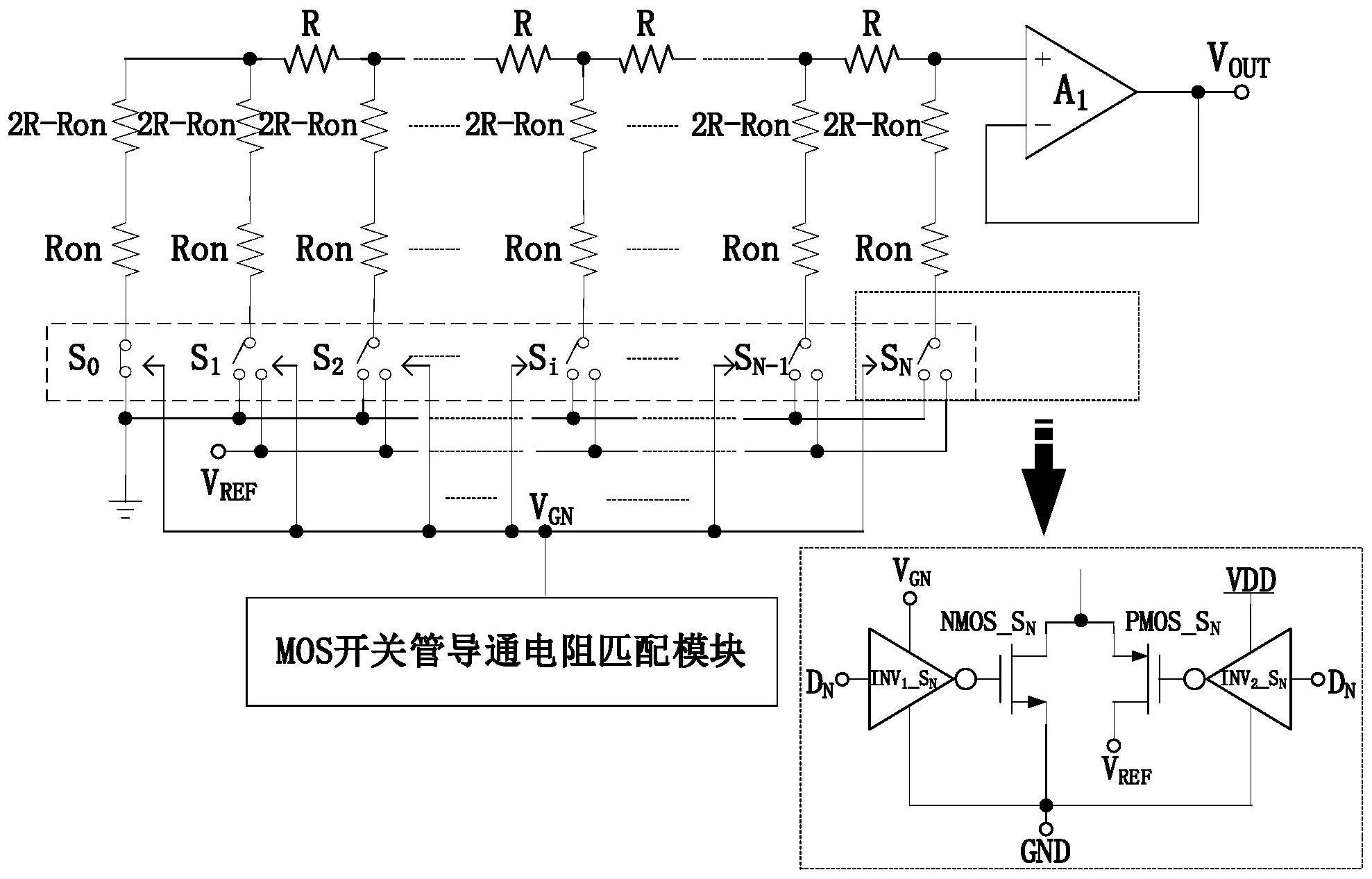

2、一种小面积高精度电压型r-2r结构dac,dac最高位为n,对任意位数电压型r-2r结构dac均适用,包括r-2r电阻网络和mos开关管导通电阻匹配模块。

3、所述r-2r电阻网络为梯形的网状电阻网络(如图2与图4所示),包括n-1个阻值均为r的电阻rj,1,j=1,2…n-1;n+1个阻值均为2r-ron的电阻ri,2,i=0,1,2…n;n+1个开关s0,s1,s2…sn,每1个开关由1个nmos开关管nmos_si、1个pmos开关管pmos_si和2个cmos反相器inv1_si、inv2_si组成,且每个开关的电阻阻值均表示为一个阻值为ron的导通电阻roni;则共计有n+1个nmos开关管、n+1个pmos开关管、2(n+1)个cmos反相器。

4、每一个开关si中mos开关管所表示的导通电阻roni,以其一端一一对应的串联ri,2构成一条支路,另一端选择参考高电位vref或者参考低电位gnd,共计n+1条支路;其中,开关s0总是选择参考低电位gnd导通。

5、具体的,每一位开关si包括1个nmos开关管、1个pmos开关管、2个cmos反相器inv1_si、inv2_si,以最高位开关sn为例,其他位除输入数字码字di不同外均相同,反相器inv1_sn的高电位为mos开关管导通电阻匹配模块产生的nmos1开关管导通栅端电位vgn,低电位为参考低电位gnd,输入为数字码字dn,输出连接开关管nmos_sn;反相器inv2_sn的高电位为vdd,低电位为参考低电位gnd,输入也为数字码字dn,输出连接开关管pmos_sn。

6、rj,1之间为串联关系,对于n-1个电阻rj,1以r1,1左端起为节点1,相邻两个电阻之间以及rn-1,1右端至为节点n,共计节点1,2,…,n处;将开关s0和s1对应两条支路电阻ri,2的另一端接入节点1,其余开关s2…sn对应支路电阻ri,2的另一端依次一一对应的接入节点2,…,n处,形成梯形的网状电阻网络,最后在最高位的rn,2与rn-1,1并联节点n处输出电压vout。

7、从r-2r电阻网络的最低位lsb向最高位msb依次看去,依次有n+1个开关s0,s1,s2…sn,每1个开关si中每次数字码字di控制只有一个mos开关管导通,另一个mos开关管关断。nmos开关管导通传输参考低电位gnd,pmos开关管导通传输参考高电位vref。r-2r电阻网络产生与输入数字码字对应的电压;输入信号分别为控制各位开关导通的输入数字码字d1…dn、参考高电位vref、参考低电位gnd、电源电位vdd、mos开关管导通电阻匹配模块产生的nmos1开关管导通栅端电位vgn;输出信号为dac输出vout。

8、所述mos开关管导通电阻匹配模块由采样模块和钳位运放构成(如图3所示),包括4个电阻r1、r2、r3、r4,1个pmos开关管pmos1,1个nmos开关管nmos1和钳位运放a0。

9、采样模块包括电阻r1、r2、r3、r4,1个pmos开关管pmos1,1个nmos开关管nmos1,其中r3=r4,r1=r2;pmos1的源端连接参考高电位vref,栅端接参考低电位gnd,漏端接电阻r2;r2与r1相连,相连处为节点a,r1另一端与nmos1的漏端相接;nmos1的源端接参考低电位gnd,栅端接钳位运放a0的输出记为nmos1开关管导通栅端电位vgn;r3一端与参考高电位vref相连,另一端与r4相连,r3与r4相连处为节点b,r4另一端接参考低电位gnd;采样模块负责采集其开关管pmos1与nmos1都导通时nmos1开关管导通栅端电位vgn。

10、钳位运放a0的正端连接节点a,负端连接节点b,输出与nmos1的栅端nmos1开关管导通栅端电位vgn相连,也与反相器inv1_sn的高电位相连;负责使采样模块中节点a与节点b的电位相同,从而使开关管pmos1与nmos1都导通时导通电阻相同。

11、mos开关管导通电阻匹配模块使得每1个nmos开关管与pmos开关管开关导通电阻匹配,进行模拟校准,从而提高dac的性能与精度;其输入为参考高电位vref、参考低电位gnd,输出信号为nmos1开关管导通栅端电位vgn。

12、进一步的,所述采样模块中mos开关管和r-2r电阻网络中mos开关管均处于线性区;且采样模块与r-2r电阻网络的每个开关中的nmos开关管nmos1、nmos_si尺寸均相同(w均为wn、l均为ln、w/l均为(w/l)n),pmos开关管pmos1、pmos_si尺寸均相同(w均为wp、l均为lp、w/l均为(w/l)p)。

13、dac最高位为n,只有第m位有效时,控制第m位的pmos开关管导通nmos开关管断开,此时第m位的pmos开关管与nmos开关管的栅端电位均为参考低电位gnd;其他位pmos开关管均断开nmos开关管均导通,此时其他位的pmos开关管栅端电位均为电源电压vdd,nmos开关管的栅端电位均为mos开关管导通电阻匹配模块产生的nmos1开关管导通栅端电位vgn。可以计算出,只有第m位有效时对vout贡献的电压为vref/2n-m,m=1,2…n,由叠加定理可知有dac传递函数vout=vref(2-n×d1+2-(n-1)×d2+2-(n-2)×d3+…+2-1×dn);其中d1到dn是由低到高输入的数字码字,取值均为1或0。

14、进一步的,所述输出电压节点n处还串联一个单位增益缓冲器a1,以增加带载能力。

15、本发明选择一个nmos开关管与一个pmos开关管组成一位开关的原因是:nmos开关管可以传输的高参考电位vrefh上限受阈值电压限制,即高参考电位vrefh与nmos1开关管导通栅端电位vgn之差必须大于nmos开关管阈值电压vthn,也即高参考电位vrefh必须小于nmos1开关管导通栅端电位vgn与vthn之差;pmos开关管可以传输的低参考电位vrefl下限受阈值电压限制,即低参考电位vrefl与pmos开关管栅端电位vgp之差(绝对值)必须大于pmos开关管阈值电压vthp(绝对值),也即低参考电位vrefl必须大于vthl与vg p之差,也即低参考电位vrefl不能低到参考低电位gnd;故不能选择2个nmos开关管作为一位的开关,也不能选择2个pmos开关管作为一位的开关,选则一个nmos开关管与一个pmos开关管组成一位的开关最合适,这样可以拓宽参考电位的取值范围。

16、本发明电压型r-2r结构dac与传统电压型r-2r结构dac面积作比较:

17、设传统的n位电压型r-2r结构dac中最低位nmos开关管宽为wn、长为ln、宽长比为(w/l)n,最低位pmos开关管宽为wp、长为lp、宽长比为(w/l)p,最低位开关作为单位开关,由低位到高位每一位mos开关宽度w加倍可知,最终传统的n位r-2r结构dac的单位开关个数为(20+20+21+22+23+…+2n-1)×2=2n+1个,面积为(2n×wn×ln+2n×wp×lp)。

18、本发明的n位电压型r-2r结构dac的所有nmos开关管宽、长、宽长比均相同,所有pmos开关管宽、长、宽长比均相同。则本发明所有nmos开关管宽长比均为(w/l)n,所有pmos开关管宽长比均为(w/l)p,则(n+1)条支路由(n+1)×2个单位开关,面积为((n+1)×wn×ln+(n+1)×wp×lp),即面积缩小了2n/(n+1)倍。可见这种改变传统2r电阻的阻值为(2r-ron)的技术可以大幅缩小dac芯片面积。mos开关面积的大幅缩小使得mos的寄生电容大幅缩小,使dac速度更快。

19、mos开关管导通电阻匹配模块由采样模块和钳位运放构成(如图3所示),其中,采样模块中由于mos开关管的串联电阻r1、r2很大,参考电位固定,电流很小即mos开关管的ids很小,故mos开关管处于线性区,同理r-2r电阻网络中mos开关管也处于线性区。采样模块与每个开关中的nmos开关管nmos1、nmos_sn尺寸均相同(w均为wn、l均为ln、w/l均为(w/l)n),pmos开关管pmos1、pmos_sn尺寸均相同(w均为wp、l均为lp、w/l均为(w/l)p)。

20、设计r3=r4,由于钳位运放a0的“虚断”作用,r3与r4串联支路上的电流从参考高电位vref到参考低电位gnd完全流过r3与r4,故节点b处电位为vref/2。又由于钳位运放a0的“虚短”作用使得节点a处电位等于节点b处电位为vref/2。

21、设计r1=r2,同样由于钳位运放a0的“虚断”作用,r1、r2、pmos1、nmos1串联支路上的电流从参考高电位vref到参考低电位gnd完全流过r1、r2、pmos1、nmos1,即r1、r2、pmos1、nmos1电流相同,故在节点a处由基尔霍夫节点电流方程kcl可知(vref-va)/(ron,pmos1+r1)=(va-0)/(ron,nmos1+r2),va=vref/2,r1=r2即ron,pmos1=ron,nmos1。

22、通过这种对pmos1与nmos1施加相同电流与电压的方式,由ron=vds/ids可知,迫使nmos1和pmos1工作在相同的漏源电压vds和漏源电流ids下,使nmos1和pmos1的导通电阻相匹配,此时pmos1的栅端接参考低电位gnd,得到此时nmos1开关管导通栅端电位vgn。

23、以校准最高位开关sn为例,其他开关同理共用一个mos开关管导通电阻匹配模块。

24、与nmos_sn相连的反相器inv1_sn中pmos开关管源端接nmos1开关管导通栅端电位vgn,inv1_sn中nmos开关管源端接参考低电位gnd,pmos开关管与nmos开关管的栅端相连接输入信号,pmos开关管与nmos开关管的漏端相连接输出信号,可以使得当开关的nmos开关管需要开启时把nmos1开关管导通栅端电位vgn传输到nmos_sn的栅端,当开关的nmos开关管需要关断时把参考低电位gnd传输到nmos_sn的栅端。

25、与pmos_sn相连的cmos反相器inv2_sn中pmos开关管源端接vdd,inv2_sn中nmos开关管源端接参考低电位gnd,pmos开关管与nmos开关管的栅端相连接输入信号,pmos开关管与nmos开关管的漏断相连接输出信号,可以使得当开关的pmos开关管需要开启时把参考低电位gnd传输到pmos_sn的栅端,当开关的pmos开关管需要关断时把vdd传输到pmos_sn的栅端。

26、由以上描述可知,每一位开关只会导通一种mos开关管,不会有pmos开关管与nmos开关管同时导通的情况。比如输入的数字码字di=0,此时nmos开关管导通pmos开关管关断;输入的数字码字di=1,此时pmos开关管导通nmos开关管关断。

27、在采样模块中,pmos开关管与nmos开关管同时导通且导通电阻相同,pmos1的栅源电压vgs_pmos1=vref,nmos1的栅源电压vgs_nmos1=vgn。由于在开关sn中pmos_sn导通时的处于深线性区,mos压降vds非常小,可以近似认为pmos_sn导通时的vg s_pmos_sn=vref,nmos_sn导通时的vgs_nmos_sn=vgn。

28、由于设计采样模块与开关sn中的nmos开关管nmos1与nmos_sn尺寸相同均为(w/l)n,pmos开关管pmos1与pmos_sn尺寸相同均为(w/l)p。所以由mos导通电阻公式ron=1/[un/pcox(w/l)n/p(vgs-vth)]可知,nmos_sn与nmos1的工艺参数、尺寸、过驱动电压(vgs-vth)均相同也即导通电阻ron_n相同,pmos_sn与pmos1的工艺参数、尺寸、过驱动电压(vgs-vth)均相同也即导通电阻ron_p相同。

29、在采样模块中nmos1和pmos1的导通电阻相匹配,通过上述分析也可得nmos1和nmos_sn、pmos1和pmos_sn的导通电阻相匹配,最终对于nmos1、nmos_sn、pmos1、pmos_sn这4个mos的导通电阻均相同,这个阻值记为ron。

30、特别地,如图4本发明电压型r-2r结构dac总体结构示意图所示,由于本发明的每一位mos开关阻值均相同,所以由低位到高位所有位数均可以共用一个mos开关管导通电阻匹配模块,为所有位提供nmos1开关管导通栅端电位vgn,解决了每一位nmos开关管与pmos开关管导通电阻不匹配的问题。

31、在面对pvt变化时,传统的mos开关都会受pvt影响大,从而恶化dac的性能与精度。但是在本发明中,通过匹配nmos开关管与pmos开关管的漏源电压与漏源电流,达到nmos开关管与pmos开关管导通电阻匹配效果,较少受到pvt影响,只需要让运放a0钳位准确即可。mos开关管导通电阻匹配模块共用方式降低了校准模块的功耗,同时极大减小了模拟校准模块电路的面积,在优化dac性能提高dac精度同时又不过多增加过芯片面积。

32、综上所述,本发明通过选择一个nmos开关管和一个pmos开关管组成一位开关,拓宽了参考电位的取值范围;通过改变传统2r电阻的阻值为(2r-ron)后,实现由低位到高位mo s开关尺寸相同不需要倍增,达到小面积的目的,同时mos开关面积的大幅缩小使得mos的寄生电容大幅缩小使dac速度更快;通过由低位到高位所有mos开关共用一个mos开关管导通电阻匹配模块,使得r-2r电阻网络匹配很好,可以减小pvt变化对dac的影响,且这种共用方式降低了校准模块的功耗,同时达到既提升dac性能与精度又不占用太大面积的目的。本发明实现电压型r-2r结构dac电路面积小、精度高,且对任意位数电压型r-2r结构dac均适用。

- 还没有人留言评论。精彩留言会获得点赞!