延迟自校准电路、直接数字频率合成器及延迟自校准方法与流程

本发明涉及集成电路,特别是涉及一种延迟自校准电路、直接数字频率合成器及延迟自校准方法。

背景技术:

1、随着社会的发展科技的进步,信息吞吐率的要求水涨船高。直接数字频率合成器(dds)是现代数字通信系统的重要组成部分,为了提高最高工作频率,业界提出了多路分时交替并行技术,基于此技术的数控振荡器(nco)可产生低速的多路的相位分别滞后的数字正弦波信号,然后多通道合成一路高速数字信号,再通过高速数模转换器(dac)转换成模拟信号输出。分时交替式的直接数字频率合成系统降低了数控振荡器的速率要求,但提升了电路的复杂性,引入了更多的寄生延时,需要额外增加n合1多路复接器(mux)、提供相应的多相时钟,同时系统工作速率的瓶颈也转移到了高速锁存器。

2、随着工作频率的进一步提高,采样时钟的周期减小,与每个单元实际工作时的门级延迟相比拟,如果数据与采样时钟不能满足一定的时序要求,则在数据的传输过程会产生误码,导致最终输出的波形出错。

3、为保证电路采样时刻的可控,现有技术技术提出了一种基于延迟锁相原理的时序调整电路,构成基于锁相环的反馈环路,调节两个输入信号间的延迟,获得期望的固定的相位差。但是,对于不同的时钟频率,特别是如今越来越高的采样速率,时钟间的固定相位差不能保证电路随时工作在最佳采样位置,这是因为环外的数据链路、时钟链路上的单元也会引入一定延迟,并受工艺波动、温度漂移、时钟变化等因素影响。这使得现有技术存在局限性。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种对直接数字频率合成器或者数模转换器电路中的数据与采样时钟的延迟进行闭环的、自动的、连续跟踪的调节电路,这种自校准电路基于延迟锁相原理,辅助主体部分工作,使得电路在工艺波动、温度波动、时钟变化等各种情况下,电路能够获取数据与采样时钟的准确相位关系,自动调节二者之间的延迟,满足正确采样的时序要求,避免误码产生,有利于直接数字频率合成器电路工作在更高的时钟频率下获得更好的高速性能。

2、为实现上述目的及其他相关目的,本发明提供的技术方案如下。

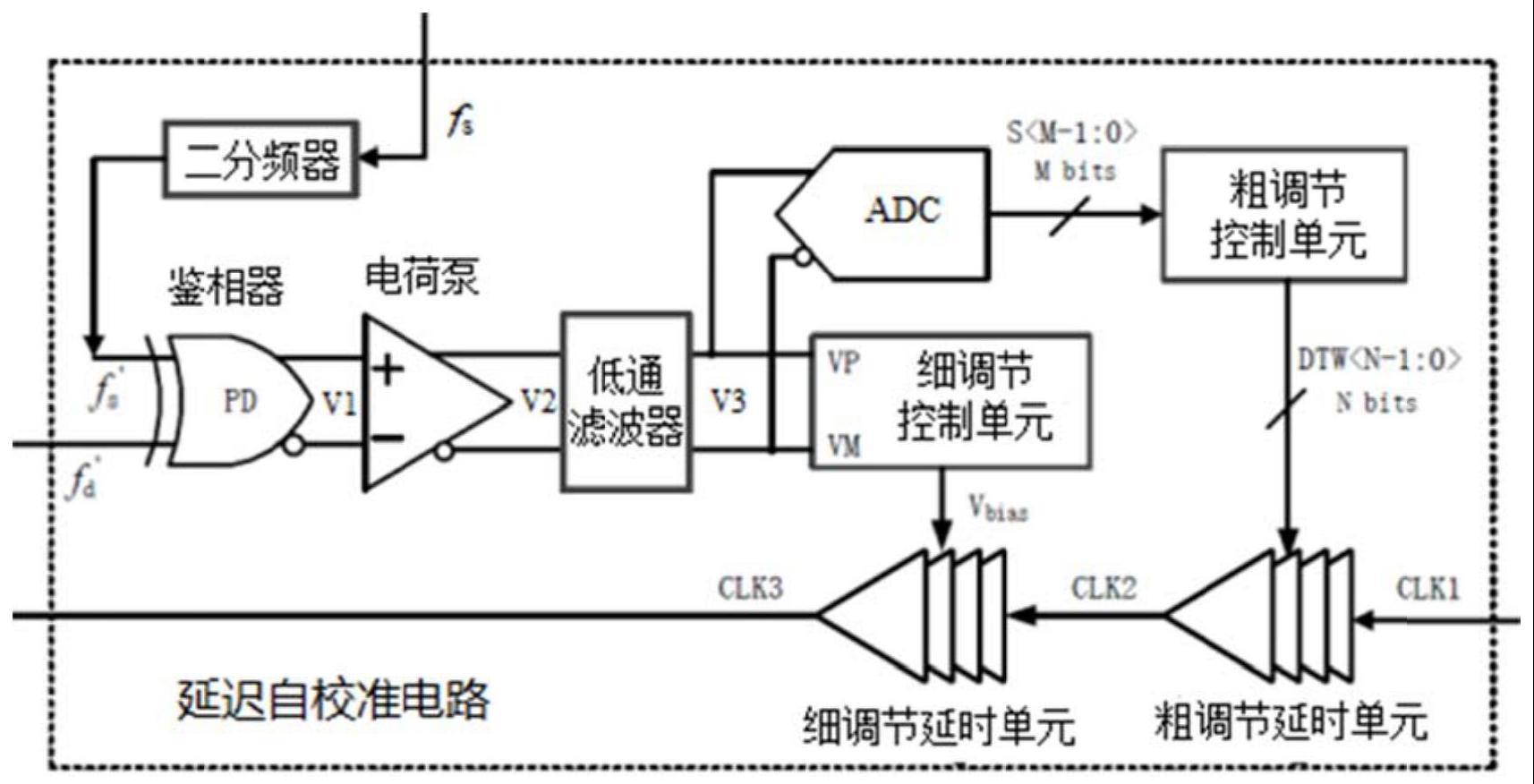

3、一种延迟自校准电路,用于调节校准数据信号与采样时钟之间的延迟,包括:

4、鉴相器,接收数据采样信号及时钟采样信号,对所述数据采样信号及所述时钟采样信号的相位差进行比较输出,得到第一差分信号;

5、电荷泵,对所述第一差分信号进行存储转换,得到第二差分信号;

6、低通滤波器,在所述第二差分信号的控制下进行充放电处理,得到第三差分信号;

7、模数转换器,对所述第三差分信号进行模数转换处理,得到数字控制码;

8、粗调节控制单元,对所述数字控制码进行逻辑处理,得到时钟反相使能信号和n位粗调节延时控制码;

9、粗调节延时单元,接收所述时钟反相使能信号、所述采样时钟及n位所述粗调节延时控制码,在所述时钟反相使能信号及n位所述粗调节延时控制码的控制下,对所述采样时钟的延时进行调节,得到粗调采样时钟;

10、细调节控制单元,对所述第三差分信号进行转换处理,得到偏置电压;

11、细调节延时单元,接收所述偏置电压及所述粗调采样时钟,在所述偏置电压的控制下,对所述粗调采样时钟的延时进行调节,得到细调采样时钟;

12、其中,所述数据采样信号与所述数据信号相关,所述时钟采样信号与所述采样时钟相关,所述细调采样时钟用于生成多相时钟以控制所述数据信号的相位,n为大于或者等于2的整数。

13、可选地,所述延迟自校准电路还包括二分频器,所述采样时钟经缓冲延时后输入所述二分频器,所述二分频器输出所述时钟采样信号。

14、可选地,所述鉴相器包括异或门。

15、可选地,所述粗调节延时单元包括同或门及n级依次级联的粗调节延时子单元,所述同或门的第一输入端接所述采样时钟,所述同或门的第二输入端接所述时钟反相使能信号,所述同或门的输出端接第1级所述粗调节延时子单元的输入端,第i+1级所述粗调节延时子单元的输入端接第i级所述粗调节延时子单元的输出端,第n级所述粗调节延时子单元的输出端输出所述粗调采样时钟,n级所述粗调节延时子单元的控制端与n位所述粗调节延时控制码一一对应连接,其中,i为1~n-1的整数。

16、可选地,所述粗调节延时子单元包括两路复用器及延时结构,所述两路复用器的第一输入端接所述延时结构的输入端,所述延时结构的输出端接所述两路复用器的第二输入端,所述两路复用器的控制端接所述粗调节延时控制码,所述两路复用器的第一输入端作为所述粗调节延时子单元的输入端,所述两路复用器的输出端作为所述粗调节延时子单元的输出端,所述两路复用器的控制端作为所述粗调节延时子单元的控制端。

17、可选地,在第j级所述粗调节延时子单元中,所述延时结构包括2(j-1)个依次级联的反相器,其中,j为1~n的整数。

18、可选地,所述细调节控制单元包括运算放大器、pmos管及nmos管,所述运算放大器的同相输入端及所述运算放大器的反相输入端分别接所述第三差分信号的差分两端,所述pmos管的源极接电源电压,所述运算放大器的输出端接所述pmos管的栅极,所述pmos管的漏极接所述nmos管的漏极,所述nmos管的栅极接所述nmos管的漏极,所述nmos管的源极接地,所述nmos管的栅极输出所述偏置电压。

19、可选地,所述细调节延时单元包括s级依次级联的电流模反相器,第1级所述电流模反相器的输入端接所述粗调采样时钟,第k级所述电流模反相器的输入端接第k-1级所述电流模反相器的输出端,第s级所述电流模反相器的输出端输出所述细调采样时钟,所述偏置电压作为各级所述电流模反相器的尾电流偏置电压,其中,s为大于或者等于2的整数,k为2~s的整数。

20、一种直接数字频率合成器,包括:

21、数控振荡器,根据数据信号产生多路相位分别滞后的数字正弦波信号;

22、多路复用器,x+1个所述多路复用器并行设置,x个所述多路复用器的各个输入端与各个所述数字正弦波信号一一对应连接,一个所述多路复用器的各个输入端接收预设二进制码,各个所述多路复用器的控制端分别接多相时钟信号;

23、锁存器,x个所述锁存器并行设置,x个所述锁存器的输入端与x个接收所述数字正弦波信号的所述多路复用器的输出端一一对应连接;

24、数模转换器,其输入端与各个所述锁存器的输出端连接,输出模拟信号;

25、时钟分频模块,根据系统时钟产生所述采样时钟;

26、第一缓冲器,输入端接所述采样时钟,输出端接各个所述锁存器的时钟控制端;

27、第二缓冲器,输入端接所述采样时钟;

28、如权利要求2-8中任一项所述的延迟自校准电路,与所述第二缓冲器的输出端、接收所述预设二进制码的所述多路复用器的输出端及所述时钟分频模块的输出端分别连接,得到并输出所述细调采样时钟;

29、多相时钟生成模块,根据所述细调采样时钟生成所述多相时钟信号;

30、其中,x为大于或者等于2的整数。

31、一种延迟自校准方法,应用于上述任一项所述的延迟自校准电路,包括:

32、关闭所述细调节控制单元,使能所述粗调节控制单元,产生n位所述粗调节延时控制码,通过所述粗调节控制单元进行调节,基于所述粗调节控制单元的调节反馈,找出使得所述数字控制码靠近1/2量程处的n位所述粗调节延时控制码并保持,以使所述数据采样信号与所述时钟采样信号的相位差靠近-ts/2;

33、保持所述粗调节控制单元,并使能所述细调节控制单元,结合所述粗调节控制单元及所述细调节控制单元进行调节,通过所述细调节控制单元的调节反馈,使得所述数据采样信号与所述时钟采样信号的相位差进一步靠近-ts/2;

34、其中,ts为所述采样时钟的周期。

35、如上所述,本发明提供的延迟自校准电路、直接数字频率合成器及延迟自校准方法,至少具有以下有益效果:

36、结合“鉴相器+电荷泵+低通滤波器+模数转换器+粗调节控制单元+粗调节延时单元+细调节控制单元+细调节延时单元”的结构设计延迟自校准电路,形成了基于延迟锁相原理的闭环跟踪的延时校准调节,能够获取数据信号与采样时钟之间的延迟或者相位关系,并根据实际需求自动结合粗调与细调对二者之间的延迟进行调节,即使在工艺波动、温度波动、时钟变化等各种情况下,也能通过该延迟自校准电路自动准确调节数据信号与采样时钟之间的延迟或者相位差,满足正确采样的时序要求,避免采样误码产生,将其应用在直接数字频率合成器中时,有利于直接数字频率合成器电路工作在更高的时钟频率下获得更好的高速性能。

- 还没有人留言评论。精彩留言会获得点赞!