集成光学开关的制作方法

本发明的实施例涉及开关设备,例如但不限于在模数转换设备中使用的开关设备,特别是涉及在采样保持电路中使用的开关设备。

背景技术:

1、采样保持电路是这样的设备,该设备对模拟信号进行采样、并且周期性地将该模拟信号的值保持在恒定的水平上一段确定的时间。

2、出于该目的,采样保持电路可以例如包括开关,该开关由周期性脉冲信号控制并且被耦合到电容性元件,并且该开关被配置为接收待采样的模拟信号作为输入,以及递送经采样的信号作为输出。

3、常规地,周期脉冲信号由电子时钟信号生成器生成。

4、在这种类型的信号中,通常会观察到抖动(jitter)现象,抖动现象对应于在所生成的信号的脉冲与考虑到时钟信号生成器的理论频率而应当观察到的理论脉冲之间的时间偏移。特别地,抖动可能是由电磁干扰引起的,并且可能导致数据传输中的错误。

5、例如,可能观察到在生成信号的某些脉冲与相同频率的理论信号之间的50飞秒量级的变化。

6、该问题的一种解决方案包括使用脉冲光学信号,例如,该脉冲光学信号由激光器发射,并且被传输给光电导体体部,光电导体体部的电阻率的变化由光学信号来计时。取决于所使用的激光器,该解决方案可能使抖动现象减少为五分之一。

7、然而,这种类型的开关表现出关断状态中的光电导体的电阻率与接通状态中的光电导体的电阻率不佳的比率,而这导致开关损失效率。

技术实现思路

1、因此,根据一个实施例,提供了一种开关,该开关例如可以在采样保持电路中被使用,其表现有限的抖动效应,并且具有关断状态中的电阻率与在接通状态中的电阻率的高比率。

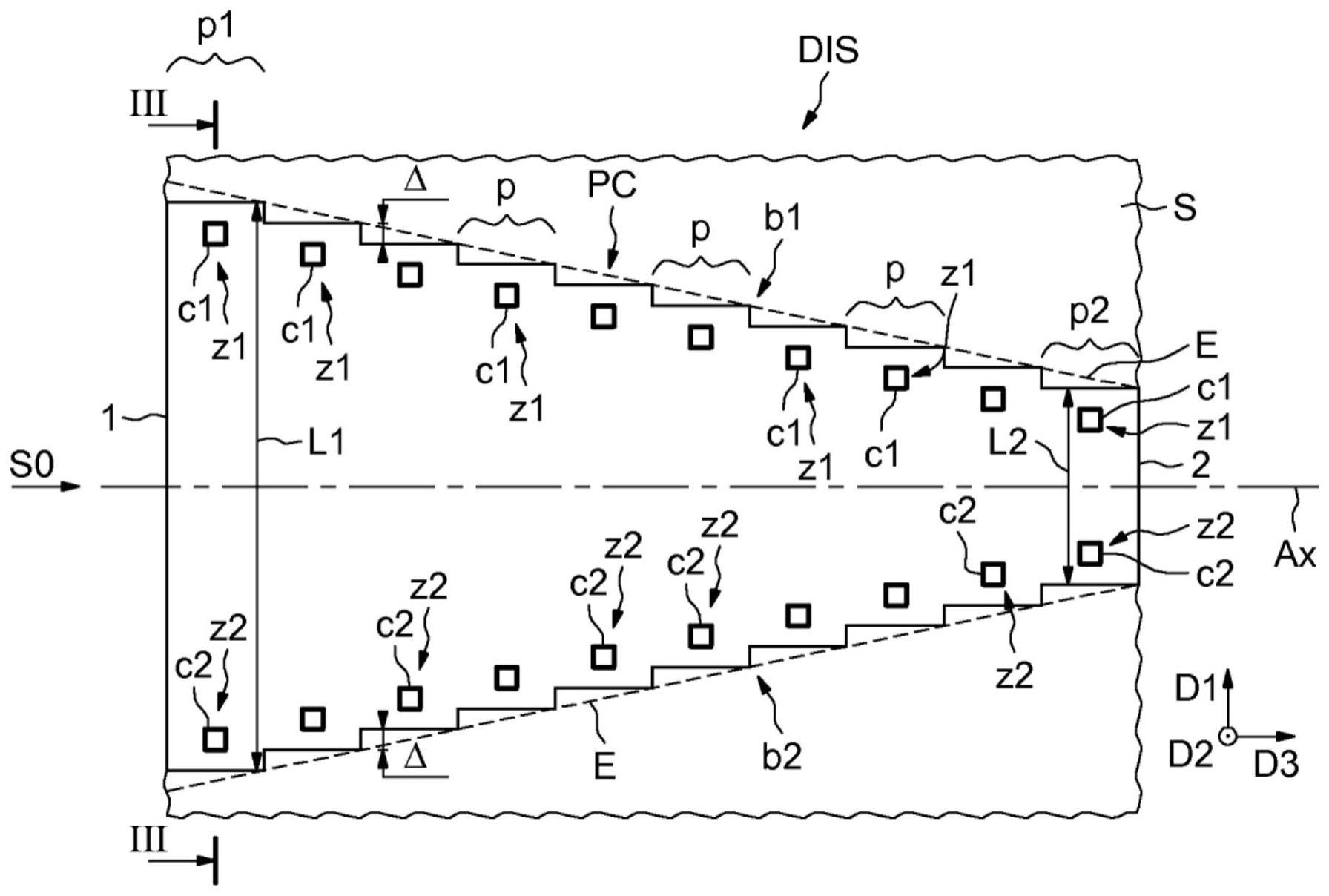

2、根据一方面,提供了一种集成光学开关,其在半导体衬中和在半导体衬底上制造,该集成光学开关包括光电导体体部,光电导体体部包括第一端和第二端,该第一端被配置为接收电输入信号,该第二端被配置为递送电输出信号,光电导体体部具有通过存在光学信号来激活的电接通状态、以及通过不存在光学信号来激活的电关断状态,其中从第一端到第二端的方向限定了纵向方向。

3、光电导体体部具有沿纵向方向从第一端向第二端逐渐减小的、与纵向方向正交的横截面。

4、发明人已经观察到光电导体体部的电阻率的降低特别取决于所吸收的光子的数量。此外,由于所吸收的光子数目沿光电导体体而减少,所以由光学信号照射的恒定横截面光电导体体部表现出不均匀的电阻率,并且更具体地,该电阻率在第一和第二端之间增加。

5、因此,逐渐减小光电导体体部的截面使得能够补偿这种电阻率增加,并且因此降低导通状态中的光电导体体部的电阻。光电导体体部在接通状态中的电阻率与在关断状态中的电阻率的比率因此被改进。

6、根据一个实施例,该横截面具有沿第一方向呈现的第一尺寸(例如其宽度),以及沿与第一方向正交的第二方向呈现的第二尺寸(例如其高度),并且光电导体体部的横截面的第一尺寸逐渐减小,而第二尺寸保持恒定。

7、换言之,可以仅变化光电导体体部的宽度,其高度保持恒定。

8、如上文所提及的,第一尺寸可以是横截面的宽度,该横截面的宽度平行于衬底的上表面测量,并且第二尺寸可以是横截面的高度,该横截面的高度垂直于衬底的上表面测量。

9、光电导体体部的第一尺寸可以沿包络阶梯式地减小,该包络在纵向方向上随相对于第一端的距离线性而线性地减小。

10、阶梯式地减小有利地使得能够使用常规cmos制备工艺来制造该设备。

11、光电导体体部的第一尺寸可以沿包络阶梯式地减小,该包络在纵向方向上随相对于第一端的距离而指数地减小。

12、发明人还观察到沿光电导体体部所吸收的光子数目呈指数减少。光电导体体部的宽度指数地减小,使得光电导体体部的形状能够适合在光电导体体部上的给定位置处所吸收的光子的数目,并且从而改进导通状态中的沿光电导体体部的电阻率的均匀性。接通状态中的电阻率与在关断状态中的电阻率的比率因此进一步被改进。

13、根据一个实施例,光电导体体部的包络的第一尺寸随如下项的乘积而指数地减小:光电导体体部的吸收系数和相对于在纵向方向上相对于第一端的距离。

14、材料的吸收系数是当该材料被照射时,所吸收的光子数目与未被吸收的光子数目或入射光子数目的比率。这种比率因材料而异。

15、因此,光电导体体部的形状被进一步适配于光子吸收率,光子吸收率取决于光电导体体部的材料的吸收系数。

16、光电导体体部可以包括多个并置部分,该多个并置部分沿着纵向方向被布置在第一端和第二端之间,该部分被配置为使得在第一方向上测量的该部分相应横截面的第一尺寸随所述阶梯而减小。

17、光学信号可以在第一端处被递送,并且旨在沿纵向方向传播。

18、根据一个实施例,该衬底是绝缘体上硅衬底,该衬底包括在掩埋绝缘层上制造的半导体膜,掩埋绝缘层是在载体衬底上制造的,并且第一方向与掩埋绝缘层平行,并且第二方向与掩埋绝缘层正交,并且光电导体体部是在半导体膜中制造的。

19、根据另一方面,提供了集成电子电路,该集成电子电路包括至少一个诸如上文所描述的光学开关。

20、该集成电子电路可以是采样保持电路。

技术特征:

1.一种集成电子电路,包括:

2.根据权利要求1所述的集成电子电路,还包括:

3.根据权利要求1所述的集成电子电路,其中所述集成电子电路是采样保持电路。

4.根据权利要求1所述的集成电子电路,其中沿第一方向测量的所述第一系列接触部到所述第二系列接触部之间的距离沿着从所述第一端到所述第二端的纵向方向基本上线性变化,所述第一方向与所述纵向方向正交。

5.根据权利要求1所述的集成电子电路,其中沿第一方向测量的所述第一系列接触部到所述第二系列接触部之间的距离沿着从所述第一端到所述第二端的纵向方向基本上指数式地变化,所述第一方向与所述纵向方向正交。

6.根据权利要求1所述的集成电子电路,其中沿所述第一方向测量的所述第一系列接触部到所述第二系列接触部之间的距离沿着从所述第一端到所述第二端的纵向方向阶梯式地变化,所述第一方向与所述纵向方向正交。

7.根据权利要求6所述的集成电子电路,其中以阶梯式相邻的台阶之间的阶梯高度在从所述第一端到所述第二端的方向上变化。

8.根据权利要求6所述的集成电子电路,其中以阶梯式相邻的台阶之间的台阶高度沿着从所述第一端到所述第二端的方向减小。

9.一种光学开关,包括:

10.根据权利要求9所述的开关,其中所述光电导体体部还包括在所述第一边缘处耦合到所述输入端子的第一系列接触部以及在所述第二边缘处耦合到所述输出端子的第二系列接触部。

11.根据权利要求9所述的开关,其中所述第一边缘和所述第二边缘之间的距离从所述第一距离到所述第二距离基本上线性变化。

12.根据权利要求9所述的开关,其中所述第一边缘和所述第二边缘之间的距离从所述第一距离到所述第二距离基本上指数式地变化。

13.根据权利要求9所述的开关,其中所述第一边缘和所述第二边缘之间的距离从所述第一距离到所述第二距离阶梯式地变化。

14.根据权利要求13所述的开关,其中以阶梯式相邻的台阶之间的阶梯高度在从所述第一端到所述第二端的方向上变化。

15.根据权利要求13所述的开关,其中以阶梯式相邻的台阶之间的台阶高度沿着从所述第一端到所述第二端的方向减小。

16.根据权利要求9所述的开关,其中所述第一距离小于所述第二距离。

技术总结

本公开涉及一种集成光学开关,其形成在半导体衬底中和在半导体衬底上,该集成光学开关包括光电导体体部(PC),光电导体部(PC)包括第一端(1)和第二端(2),第一端(1)被配置为接收电输入信号,该第二端(2)被配置为递送电输出信号,光电导体部(PC)具有通过存在光学信号(SO)激活的电接通状态、以及通过不存在光学信号(SO)激活的电关断状态,其中从第一端到第二端的方向限定了纵向方向(D3),并且光电导体部具有与纵向方向(D3)正交的横截面,该横截面沿纵向方向(D3)从第一端(1)向第二端(2)逐渐减小。

技术研发人员:H·泽格芒特,D·派彻,S·勒图尔,J-F·鲁,J-L·库塔

受保护的技术使用者:意法半导体有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!