一种NRLDPC部分校验矩阵编译码指示信息获取方法与流程

本发明涉及无线通信,特别是涉及一种nr ldpc部分校验矩阵编译码指示信息获取方法。

背景技术:

1、信道编码技术对于无线通信系统的性能有重要影响。nr系统中下行及上行业务信道均采用准循环低密度奇偶校验编码(quasi-cyslic low-density parity-check codes,qc-ldpc)作为信道编码方式。在nr系统embb场景下,业务数据的高吞吐率是硬性指标,而高速信道编译码的实现对提高吞吐率有重要意义。

2、nr标准3gpp ts 38.212中规定了nr系统业务信道比特级处理流程,其中信道编码使用qc-ldpc编码,其中包括两个基础矩阵bg1及bg2,并提供了51个提升因子zc,使其结合基础矩阵能够实现不同码块长度的编译码。其中,基础矩阵bg1为46行68列的基础矩阵,编码完成后前2*zc信息比特打孔,剩下66zc编码后数据进入后级速率匹配模块,即qc-ldpc编码效率为1/3,基础矩阵bg2为42行52列的基础矩阵,编码完后成前2*zc信息比特打孔,剩下50zc编码后数据进入后级速率匹配模块,即qc-ldpc编码效率为1/5。速率匹配模块包含两个作用,首先根据调度资源所能承载的比特长度,对编码后数据进行比特选择的操作,使编码后数据能够匹配物理资源;随后为了应对无线信道环境中的衰落现象,需要进行比特交织的操作。

3、在速率匹配模块的比特选择过程中,首先确定循环缓存的大小为ncb,随后将20zc的信息比特数据、校验比特数据依次输入循环缓存,随后基于harq冗余版本rv确定待发送数据的起始位置k0,最后从k0开始,取速率匹配长度e的比特信息输出,其中对于填充比特需要跳过,如图1所示。当e>=ncb时,整个循环缓存中的数据均会输出,并经过空口发送给接收端,但当e<ncb时,循环缓存中部分数据将会被打孔,即接收端对于这些位置的软比特信息置为0处理,基于以上比特选择的原理,可在编码前计算出哪些位置需要传输,哪些校验比特需要传输,而编码的时候,信息比特已知,校验比特可根据qc-ldpc结构进行对应需要传输比特的编码,而无需空口传输的校验比特则可不进行编码,从而提高编码器的效率,译码侧同理。

4、目前,业界内对于nr qc-ldpc编译码有如下两种做法:(1)基于38.212协议定义的bg1、bg2两个基础校验矩阵,对输入的信息比特进行完整的qc-ldpc编码操作,随后进入速率匹配模块进行比特选择及交织;而在译码侧,则首先解速率匹配及harq合并,随后利用基础校验矩阵进行完整的qc-ldpc译码;(2)基于38.212协议定义的bg1、bg2两个基础校验矩阵,根据速率匹配相关参数,对基础校验矩阵进行裁剪,输出参与qc-ldpc编译码的行及列的指示,指导qc-ldpc编译码的部分编译码操纵。

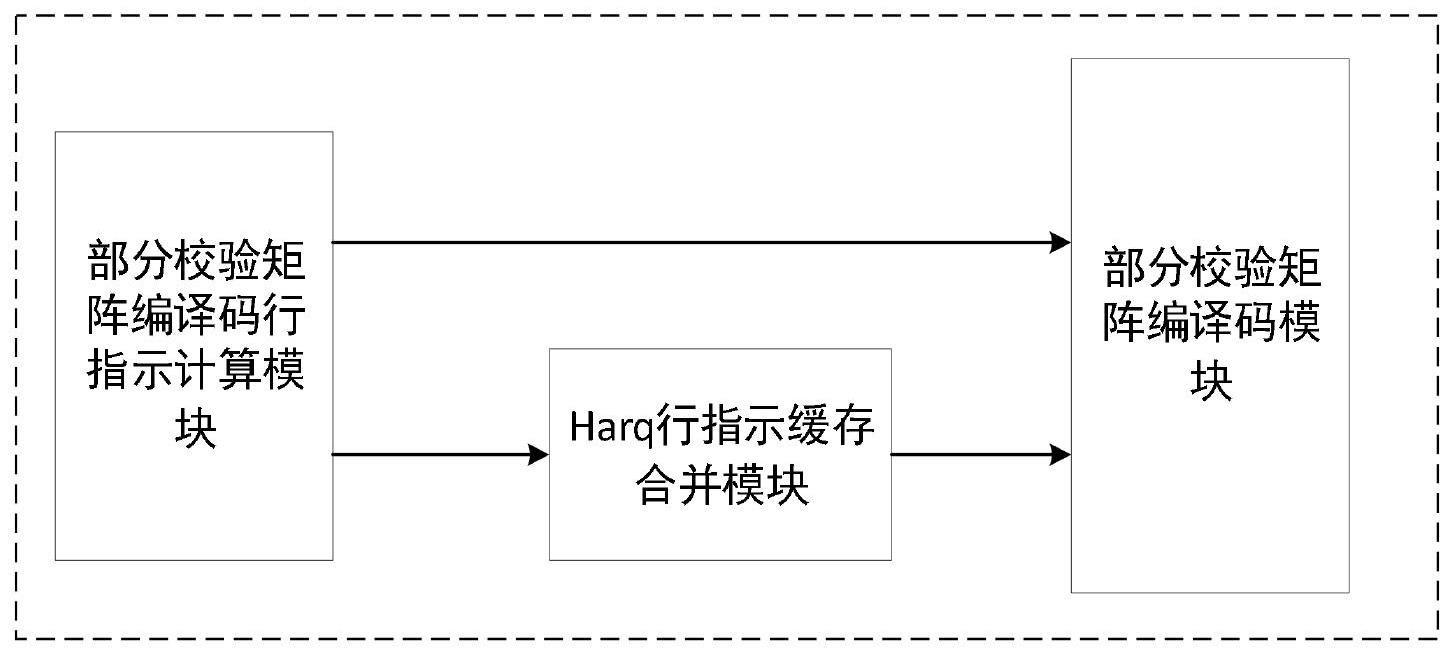

5、其中,业界内的两种实现方式,(1)为全矩阵qc-ldpc编译码,该方案完整输出编译码结果,但在速率匹配比特选择模块可能会将已经计算得到的部分校验比特数据打孔掉,因此对于这些数据,属于浪费资源计算,但实际没有传输;(2)为部分qc-ldpc编译码实现方案,该方案根据编译码参数以及速率匹配参数,提前计算出需要速率匹配输出结果中有效的传输比特信息,随后指示qc-ldpc编译码模块,类似于对基础校验矩阵进行了裁剪,从目前已有方案来看,部分矩阵编译码方案有两个不足,首先对校验矩阵的裁剪指示包括行列的指示,根据nr qc-ldpc校验矩阵的特点,可直接通过行指示就完成对应的指示,其次,目前已有部分矩阵编译码方案计算行列指示的过程复杂且难以理解,对于硬件实现来说,逻辑复杂度较高。

技术实现思路

1、本发明所要解决的技术问题是提供一种nr ldpc部分校验矩阵编译码指示信息获取方法,减少了高码率时硬件资源的消耗及时延的损耗。

2、本发明解决其技术问题所采用的技术方案是:提供一种nr ldpc部分校验矩阵编译码指示信息获取方法,包括以下步骤:

3、接收编译码及速率匹配相关参数;所述编译码及速率匹配相关参数包括提升因子zc、基础矩阵bg的类型、信息比特净荷长度kd、填充比特长度f、速率匹配缓存大小ncb、速率匹配起始位置k0、以及速率匹配长度er;

4、根据基础矩阵bg的类型确定进入速率匹配循环缓存中的信息比特及核心校验比特的长度;

5、根据进入速率匹配循环缓存中的信息比特、填充比特以及核心校验比特的相对位置关系,确定从速率匹配起始位置k0开始到速率匹配缓存大小ncb的过程中,扩展校验比特的起始位置exp_start,以及所包含的信息比特及核心校验比特长度syscore;

6、根据速率匹配长度er、速率匹配缓存大小ncb、以及扩展校验比特的起始位置exp_start、所包含的信息比特及核心校验比特长度syscore,确定编译码需要传输的扩展校验比特的行指示。

7、所述根据基础矩阵bg的类型确定进入速率匹配循环缓存中的信息比特及核心校验比特的长度,具体为:

8、如果基础矩阵bg的类型为bg1时,进入速率匹配循环缓存中的信息比特长度nsys=20zc,信息比特加核心校验比特长度nsyscore=24zc;

9、如果基础矩阵bg的类型为bg2时,进入速率匹配循环缓存中的信息比特长度nsys=8zc,信息比特加核心校验比特长度nsyscore=12zc;

10、其中,进入速率匹配循环缓存中的信息比特长度nsys及信息比特加核心校验比特长度nsyscore中均包含填充比特长度f。

11、所述根据进入速率匹配循环缓存中的信息比特、填充比特以及核心校验比特的相对位置关系,确定从速率匹配起始位置k0开始到速率匹配缓存大小ncb的过程中,扩展校验比特的起始位置exp_start,以及所包含的信息比特及核心校验比特长度syscore,具体为:

12、当速率匹配起始位置k0小于信息比特净荷长度kd时,所述扩展校验比特的起始位置exp_start为进入速率匹配循环缓存中的信息比特加核心校验比特长度nsyscore,所包含的信息比特及核心校验比特长度syscore为进入速率匹配循环缓存中的信息比特加核心校验比特长度nsyscore减去速率匹配起始位置k0再减去填充比特长度f;

13、当速率匹配起始位置k0大于信息比特净荷长度kd,且小于或等于进入速率匹配循环缓存中的信息比特长度nsys时,所述扩展校验比特的起始位置exp_start为进入速率匹配循环缓存中的信息比特加核心校验比特长度nsyscore,所包含的信息比特及核心校验比特长度syscore为进入速率匹配循环缓存中的信息比特加核心校验比特长度nsyscore减去进入速率匹配循环缓存中的信息比特长度nsys;

14、当速率匹配起始位置k0大于进入速率匹配循环缓存中的信息比特长度nsys,且小于或等于进入速率匹配循环缓存中的信息比特加核心校验比特长度nsyscore时,所述扩展校验比特的起始位置exp_start为进入速率匹配循环缓存中的信息比特加核心校验比特长度nsyscore,所包含的信息比特及核心校验比特长度syscore为进入速率匹配循环缓存中的信息比特加核心校验比特长度nsyscore减去速率匹配起始位置k0;

15、当速率匹配起始位置k0大于进入速率匹配循环缓存中的信息比特加核心校验比特长度nsyscore时,所述扩展校验比特的起始位置exp_start为速率匹配起始位置k0,所包含的信息比特及核心校验比特长度syscore为0。

16、所述根据速率匹配长度er、速率匹配缓存大小ncb、以及扩展校验比特的起始位置exp_start、所包含的信息比特及核心校验比特长度syscore,确定编译码需要传输的扩展校验比特的行指示,具体为:

17、当速率匹配长度er减去进入速率匹配循环缓存中的信息比特加核心校验比特长度nsyscore小于或等于所述扩展校验比特的起始位置exp_start到速率匹配缓存大小ncb的长度时,参与编译码的扩展校验比特行指示的开始位置start=(exp_start-nsyscore)/zc,参与编译码的扩展校验比特行指示的结束位置end=start+ceil((er-syscore)/zc);

18、当速率匹配长度er减去进入速率匹配循环缓存中的信息比特加核心校验比特长度nsyscore大于所述扩展校验比特的起始位置exp_start到速率匹配缓存大小ncb的长度时,扩展校验比特首先从所述扩展校验比特的起始位置exp_start开始,直到速率匹配缓存大小ncb结束,随后会继续从循环缓存的起始位置继续取数据,但如果只取用了部分信息比特及核心校验比特,没有再取到扩展校验比特时,则参与编译码的扩展校验比特行指示的开始位置start=(exp_start-nsyscore)/zc,参与编译码的扩展校验比特行指示的结束位置end=start+ceil((ncb-exp_start)/zc);当从循环缓存起始位置取数据,将信息比特及核心校验比特全部取出,并继续取用扩展校验比特,但未超过第一次取数据时扩展校验比特的起始位置exp_start时,参与编译码的第一次扩展校验比特行指示的开始位置start1=(exp_start-nsyscore)/zc,参与编译码的第一次扩展校验比特行指示的结束位置end1=start1+ceil((ncb-exp_start)/zc),参与编译码的第二次扩展校验比特行指示的开始位置start2=0,参与编译码的第二次扩展校验比特行指示的结束位置end2=start2+ceil((er-(ncb-exp_start+syscore+nsyscore-f))/zc);

19、当速率匹配长度er大于速率匹配缓存大小ncb减去填充比特长度f时,扩展校验比特全部都需要参与编译码,参与编译码的扩展校验比特行指示的开始位置start=0,参与编译码的扩展校验比特行指示的结束位置end=start+ceil((ncb-nsyscore)/zc);

20、其中,ceil()表示向上取整。

21、所述的nr ldpc部分校验矩阵编译码指示信息获取方法还包括根据所述编译码需要传输的扩展校验比特的行指示对42bit的行指示信息row_i进行赋值的步骤。

22、有益效果

23、由于采用了上述的技术方案,本发明与现有技术相比,具有以下的优点和积极效果:本发明基于qc-ldpc码编译码参数、速率匹配参数计算得到需要参与qc-ldpc编译码的指示信息,计算过程简化、实现逻辑简单且便于实现,即可选择在软件进行计算传递给硬件,也可在硬件直接完成计算,从而减少了高码率时硬件资源的消耗及时延的损耗,能够达到终端或基站节能的效果;本发明还基于nr系统qc-ldpc基础矩阵的特征,通过42bit的bitmap可指示哪些行需要参与编译码,减少了接口的资源,显著提高编译码器的处理速度,提高吞吐量。

- 还没有人留言评论。精彩留言会获得点赞!