集成电路器件及包括其的电子系统的制作方法

本发明构思涉及集成电路器件和包括其的电子系统,更具体地,涉及包括非易失性垂直存储器件的集成电路器件和包括该集成电路器件的电子系统。

背景技术:

1、为了满足高性能和经济可行性,期望增加集成电路器件的集成密度。具体地,存储器件的集成密度是决定产品经济可行性的重要因素之一。二维(2d)存储器件的集成密度可主要由存储单元单位的面积决定,因此可极大地受到微图案化技术水平的影响。然而,由于使用昂贵的设备来形成微图案并且芯片管芯的面积有限,因此2d存储器件的集成密度尽管在不断增加,但仍然受到限制。因此,需要具有三维(3d)结构的垂直存储器件。

技术实现思路

1、本发明构思提供了一种通过在具有三维(3d)结构的垂直存储器件中加宽具有高高宽比的沟道孔的上部并形成焊盘图案而具有改善的存储单元特性的集成电路器件以及包括该集成电路器件的电子系统。

2、本发明构思不限于上面提到的内容,并且本领域技术人员将从下面的描述中清楚地理解本发明构思。

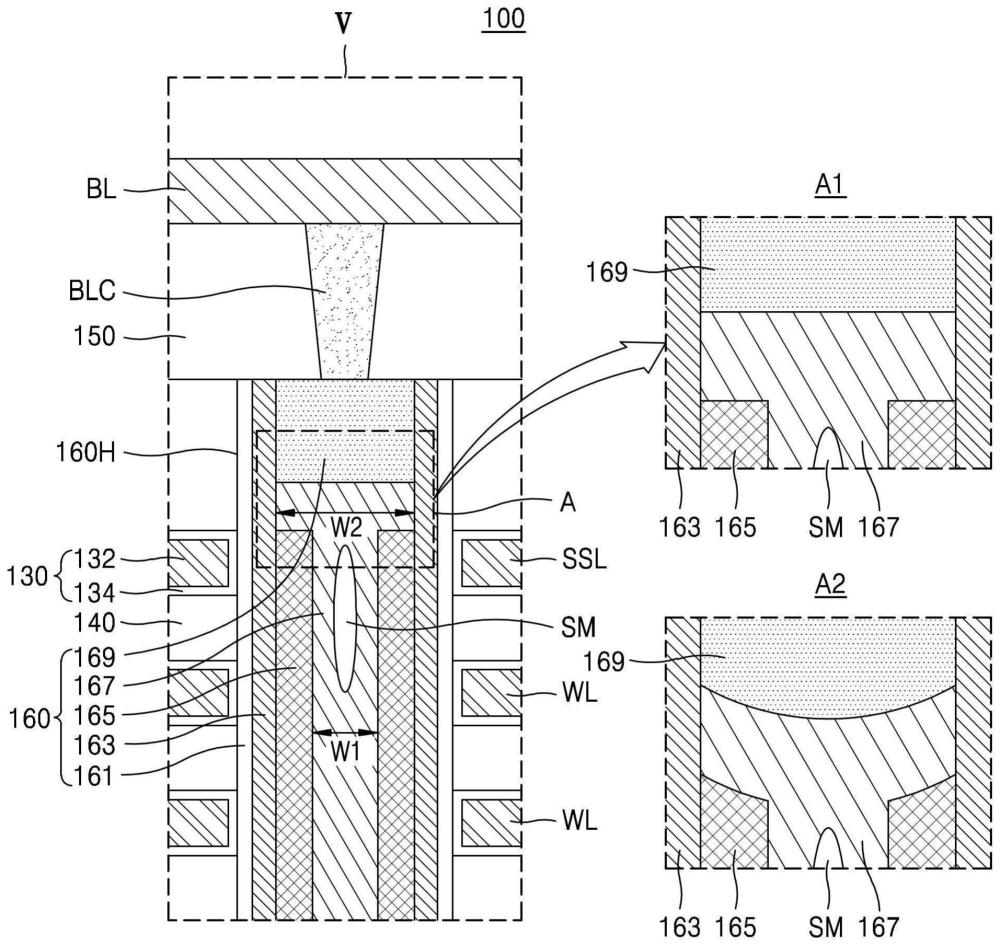

3、根据本发明构思的一方面,提供了一种集成电路器件,其包括在半导体衬底上在水平方向上延伸并在垂直方向上彼此重叠的多条导电线、与多条导电线交替并在水平方向上延伸的多个绝缘层、以及延伸穿过所述多条导电线和所述多个绝缘层的沟道结构,其中沟道结构包括核心绝缘层、在核心绝缘层的侧壁和底表面上的电阻变化层、在电阻变化层的外壁上的沟道层、以及在核心绝缘层的顶表面上(例如,覆盖核心绝缘层的顶表面)的焊盘图案,其中电阻变化层的最顶表面与核心绝缘层接触并与焊盘图案的最底表面间隔开。

4、根据本发明构思的另一方面,提供了一种集成电路器件,其包括:半导体衬底,包括单元区和与单元区相邻的连接区;栅极堆叠,在第一方向和第二方向上延伸,包括多条导电线和多个绝缘层,并且在连接区中具有台阶结构,第一方向和第二方向平行于半导体衬底的主表面并且彼此交叉,所述多条导电线和所述多个绝缘层在垂直于半导体衬底的主表面的第三方向上交替地堆叠;沟道结构,在单元区中并在第三方向上延伸穿过栅极堆叠;以及多个接触插塞,在连接区中并与所述多条导电线的相应端部接触,其中沟道结构包括核心绝缘层、在核心绝缘层的侧壁和底表面上的电阻变化层、在电阻变化层的外壁上的沟道层、在沟道层的外壁上的电介质层、以及在核心绝缘层的顶表面上(例如,覆盖核心绝缘层的顶表面)的焊盘图案,电阻变化层的最上表面与核心绝缘层接触并与焊盘图案的最底表面间隔开。

5、根据本发明构思的另一方面,提供了一种电子系统,其包括:主板;在主板上的集成电路器件;以及控制器,在主板上并电连接到集成电路器件,其中集成电路器件包括:多条导电线,在半导体衬底上在水平方向上延伸并在垂直方向上彼此重叠;多个绝缘层,与所述多条导电线交替并在水平方向上延伸;以及沟道结构,延伸穿过所述多条导电线和所述多个绝缘层,其中沟道结构包括核心绝缘层、在核心绝缘层的侧壁和底表面上的电阻变化层、在电阻变化层的外壁上的沟道层以及在核心绝缘层的顶表面上(例如,覆盖核心绝缘层的顶表面)的焊盘图案,电阻变化层的最顶表面与核心绝缘层接触并与焊盘图案的最底表面间隔开。

技术特征:

1.一种集成电路器件,包括:

2.根据权利要求1所述的集成电路器件,其中所述核心绝缘层包括第一部分和第二部分,所述第一部分包括所述侧壁的接触所述电阻变化层的部分,所述第二部分包括所述侧壁的接触所述沟道层的部分,以及

3.根据权利要求2所述的集成电路器件,其中所述核心绝缘层的所述第一部分包括空腔,

4.根据权利要求3所述的集成电路器件,其中所述电阻变化层的所述最顶表面具有弯曲形状,所述核心绝缘层的所述第二部分的所述最顶表面具有圆化形状,并且所述焊盘图案沿着所述核心绝缘层的所述第二部分的所述最顶表面延伸。

5.根据权利要求1所述的集成电路器件,其中从所述半导体衬底起,所述沟道层的最顶表面的垂直水平等于所述焊盘图案的最顶表面的垂直水平。

6.根据权利要求1所述的集成电路器件,其中所述焊盘图案在所述沟道层的最顶表面和所述核心绝缘层的最顶表面之间具有台阶。

7.根据权利要求6所述的集成电路器件,其中所述核心绝缘层包括第一部分和第二部分,所述第一部分包括所述侧壁的接触所述电阻变化层的部分,所述第二部分包括所述侧壁的接触所述沟道层的部分,

8.根据权利要求6所述的集成电路器件,其中所述焊盘图案包括在所述沟道层上的侧壁部分和在所述核心绝缘层上的中心部分,以及

9.根据权利要求8所述的集成电路器件,其中所述焊盘图案的所述中心部分的侧壁与所述沟道层的内壁接触,以及

10.根据权利要求1所述的集成电路器件,其中所述核心绝缘层包括第一部分和第二部分,所述第一部分具有第一水平宽度,所述第二部分将所述焊盘图案与所述第一部分分开并具有比所述第一水平宽度宽的第二水平宽度,以及

11.一种集成电路器件,包括:

12.根据权利要求11所述的集成电路器件,其中所述核心绝缘层的第一部分包括空腔,并且所述核心绝缘层的所述第一部分的侧壁与所述电阻变化层接触,

13.根据权利要求12所述的集成电路器件,其中所述核心绝缘层的所述第一部分的第一水平宽度窄于所述核心绝缘层的所述第二部分的第二水平宽度,以及

14.根据权利要求12所述的集成电路器件,其中所述沟道层的内壁与所述电阻变化层的所述外壁、所述核心绝缘层的所述第二部分的所述侧壁以及所述焊盘图案的侧壁接触,以及

15.根据权利要求11所述的集成电路器件,其中所述焊盘图案在所述沟道层的最顶表面和所述核心绝缘层的最顶表面之间具有台阶,

16.根据权利要求15所述的集成电路器件,其中所述焊盘图案的侧壁与所述沟道层的所述外壁共面,以及

17.根据权利要求11所述的集成电路器件,其中从所述半导体衬底起,所述焊盘图案的最顶表面的垂直水平等于所述电介质层的最顶表面的垂直水平,

18.根据权利要求11所述的集成电路器件,其中所述核心绝缘层包括硅氮化物,

19.一种电子系统,包括:

20.根据权利要求19所述的电子系统,其中所述主板包括将所述集成电路器件电连接到所述控制器的布线图案,

技术总结

一种集成电路器件包括:在半导体衬底上在水平方向上延伸并在垂直方向上彼此重叠的多条导电线、与所述多条导电线交替并在水平方向上延伸的多个绝缘层、以及延伸穿过所述多条导电线和所述多个绝缘层的沟道结构。沟道结构包括核心绝缘层、在核心绝缘层的侧壁和底表面上的电阻变化层、在电阻变化层的外壁上的沟道层、以及在核心绝缘层的顶表面上的焊盘图案。电阻变化层的最顶表面与核心绝缘层接触并与焊盘图案的最底表面间隔开。

技术研发人员:朴玄睦

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!