具有下电快速稳定电路的器件及下电快速稳定电路的制作方法

本技术涉及射频元器件,具体地,涉及一种具有下电快速稳定电路的器件及下电快速稳定电路。

背景技术:

1、射频开关和tuner(调谐器)是最常用的射频元器件。在射频链路中用作通道切换、收发状态切换,大量应用于物联网、通信基站、小基站、直放站、测试仪器、雷达、wifi、rfid等多个领域。射频天线开关,接在天线与射频处理电路之间,用于切换天线工作状态,用于切换频段以及接收、发射信号。通过开关,可以将不同频段、不同制式的信号分离,进而输出至手机的不同系统中进行处理,以减少不同信号之间的互相干扰,帮助提高信号接受灵敏度。射频开关是手机射频前端必不可少的关键器件,性能的优劣直接决定手机终端信号质量。由于soi工艺具有的高速、高隔离度特性和优良的抗辐射特性,有着gaas工艺无法媲美的优势。近年来,在无线通讯领域里,soi工艺已逐渐成为射频开关的首选工艺。射频开关和tuner(调谐器)需要驱动大尺寸的半导体开关,该大尺寸的半导体开关存在大的寄生电容,因此射频开关和tuner(调谐器)往往在电源下电后再次启动时候,需要等待非常长的时间。

2、其中,soi工艺的中文全称是“硅上绝缘体工艺”,也称为“soi cmos工艺”。gaas工艺的中文全称是“砷化镓工艺”,也称为“gaas mmic工艺”,是一种制备微波和毫米波器件的重要工艺。

3、因此,传统的射频开关和tuner(调谐器)在电源下电后再次启动时候,需要等待非常长的时间,是本领域技术人员急需要解决的技术问题。

4、在背景技术中公开的上述信息仅用于加强对本技术的背景的理解,因此其可能包含没有形成为本领域普通技术人员所知晓的现有技术的信息。

技术实现思路

1、本技术实施例提供了一种具有下电快速稳定电路的器件及下电快速稳定电路,以解决传统的器件在电源下电后再次启动时候,需要等待非常长的时间的技术问题。

2、本技术实施例提供了一种具有下电快速稳定电路的器件,包括下电快速稳定电路、驱动电路和器件电路本体;所述驱动电路的正压端连接正压pvdd且负压端连接负压nvdd,所述驱动电路与所述器件电路本体连接为所述器件电路本体供电;

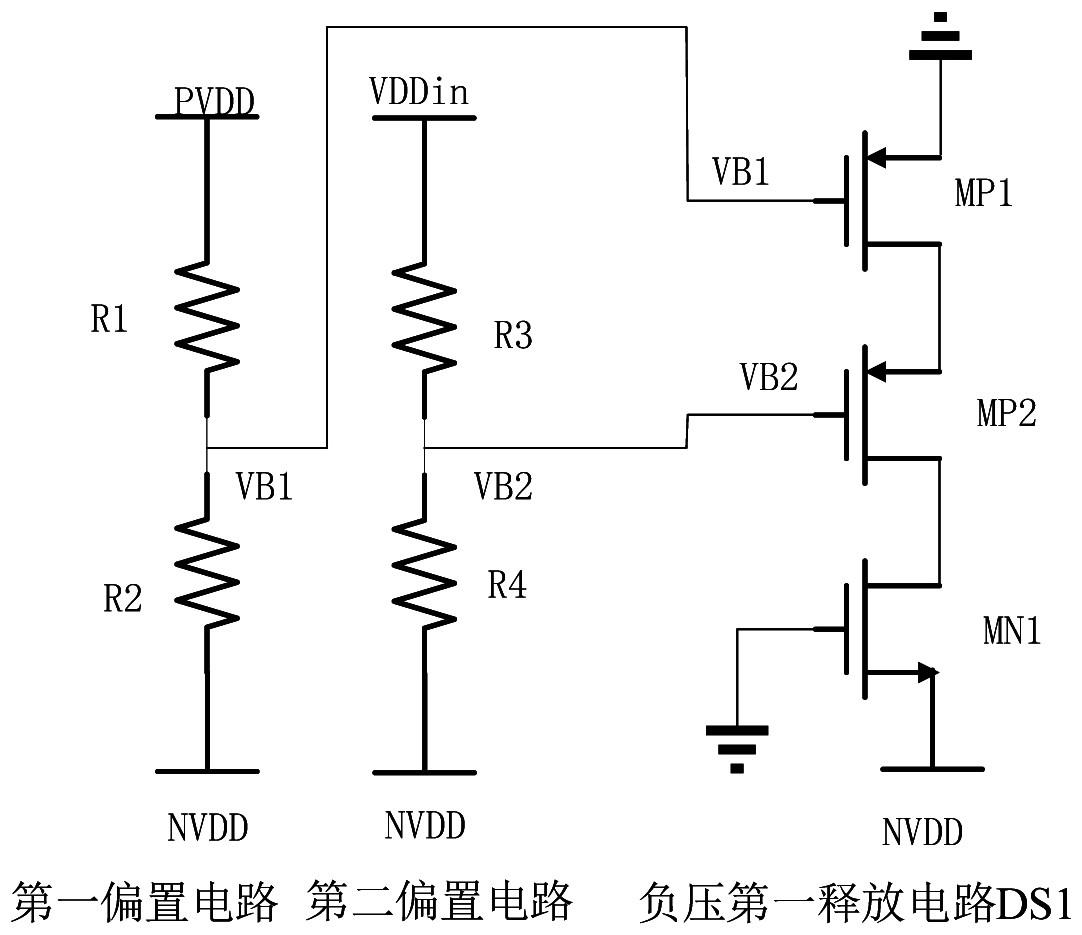

3、所述下电快速稳定电路包括负压第一释放电路,负压第一释放电路包括:

4、第一nmos管mn1,第一nmos管mn1的控制端接地,且所述第一nmos管mn1的源端接所述驱动电路的负压端;

5、第二pmos管mp2,所述第一nmos管mn1的漏端和所述第二pmos管mp2的漏端连接;

6、第一pmos管mp1,所述第二pmos管mp2的源端和所述第一pmos管mp1的漏端连接,所述第一pmos管mp1的源端接地;

7、当器件进入关闭状态时,第一nmos管mn1保持导通,控制第二pmos管mp2导通,控制第一pmos管mp1导通,使得负压第一释放电路放电。

8、实施中,当器件正常工作时,第一nmos管mn1导通,控制第二pmos管mp2关闭,控制第一pmos管mp1关闭,使得负压第一释放电路关闭。

9、实施中,具有下电快速稳定电路的器件还包括:

10、第一偏置电路,所述第一偏置电路包括在正压pvdd和负压nvdd之间顺序串联的第一电阻r1和第二电阻r2,其中,所述第一电阻r1和第二电阻r2连接处的电压作为第一偏置电压vb1;所述第一pmos管mp1的控制端连接第一偏置电压vb1;

11、第二偏置电路,所述第二偏置电路包括在输入电压vddin和负压nvdd之间顺序串联的第三电阻r3和第四电阻r4,其中,所述第三电阻r3和第四电阻r4连接处的电压作为第二偏置电压vb2;第二pmos管mp2的控制端连接第二偏置电压vb2。

12、实施中,第一电阻r1的阻值等于第二电阻r2的阻值,第三电阻r3的阻值等于第四电阻r4的阻值;

13、正压pvdd=-负压nvdd,输入电压vddin<正压pvdd。

14、实施中,具有下电快速稳定电路的器件还包括负压第二释放电路,所述负压第二释放电路包括:

15、第三nmos管mn3和第四pmos管mp4,所述第三nmos管mn3的漏端和所述第四pmos管mp4的漏端连接,所述第三nmos管mn3的源端连接所述驱动电路的负压端,第三nmos管mn3和第四pmos管mp4的控制端接地;

16、第三pmos管mp3和第二nmos管mn2,所述第三pmos管mp3的漏端和第二nmos管mn2的漏端连接,第三pmos管mp3的源端、所述第三pmos管mp3的控制端和第二nmos管mn2的控制端连接输入电压vddin,所述第二nmos管mn2的源端接地;

17、其中,所述第三pmos管mp3的漏端和所述第四pmos管mp4的源端连接。

18、实施中,具有下电快速稳定电路的器件还包括正压释放电路,所述正压释放电路包括:

19、反相器inv1;

20、第五pmos管mp5,所述第五pmos管mp5的源端接正压pvdd,所述第五pmos管mp5的控制端和漏端连接所述反相器inv1的电源;

21、第四nmos管mn4,所述第四nmos管mn4的漏端接正压pvdd,所述第四nmos管mn4的源端接地;

22、其中,所述反相器inv1的输入端连接使能信号en,所述反相器inv1的输出端连接第四nmos管mn4的控制端。

23、实施中,具有下电快速稳定电路的器件还包括:

24、输入电压vddin产生电路,所述输入电压vddin产生电路由使能信号en控制,接入电源电压vdd且输出输入电压vddin;

25、正压pvdd产生电路,连接在电源电压vdd和接地之间以产生正压pvdd;

26、负压nvdd产生电路,连接在电源电压vdd和接地之间以产生负压nvdd。

27、本技术实施例还提供以下技术方案:

28、一种下电快速稳定电路,包括负压第一释放电路,负压第一释放电路包括:

29、第一nmos管mn1,第一nmos管mn1的控制端接地,且所述第一nmos管mn1的源端接所述驱动电路的负压端;

30、第二pmos管mp2,所述第一nmos管mn1的漏端和所述第二pmos管mp2的漏端连接;

31、第一pmos管mp1,所述第二pmos管mp2的源端和所述第一pmos管mp1的漏端连接,所述第一pmos管mp1的源端接地;

32、当器件进入关闭状态时,第一nmos管mn1保持导通,控制第二pmos管mp2导通,控制第一pmos管mp1导通,使得负压第一释放电路放电;

33、当器件正常工作时,第一nmos管mn1导通,控制第二pmos管mp2关闭,控制第一pmos管mp1关闭,使得负压第一释放电路关闭。

34、实施中,下电快速稳定电路还包括:

35、第一偏置电路,所述第一偏置电路包括在正压pvdd和负压nvdd之间顺序串联的第一电阻r1和第二电阻r2,其中,所述第一电阻r1和第二电阻r2连接处的电压作为第一偏置电压vb1;所述第一pmos管mp1的控制端连接第一偏置电压vb1;

36、第二偏置电路,所述第二偏置电路包括在输入电压vddin和负压nvdd之间顺序串联的第三电阻r3和第四电阻r4,其中,所述第三电阻r3和第四电阻r4连接处的电压作为第二偏置电压vb2;第二pmos管mp2的控制端连接第二偏置电压vb2;

37、第一电阻r1的阻值等于第二电阻r2的阻值,第三电阻r3的阻值等于第四电阻r4的阻值;正压pvdd=-负压nvdd,输入电压vddin<正压pvdd。

38、实施中,下电快速稳定电路还包括负压第二释放电路,所述负压第二释放电路包括:

39、第三nmos管mn3和第四pmos管mp4,所述第三nmos管mn3的漏端和所述第四pmos管mp4的漏端连接,所述第三nmos管mn3的源端连接所述驱动电路的负压端,第三nmos管mn3和第四pmos管mp4的控制端接地;

40、第三pmos管mp3和第二nmos管mn2,所述第三pmos管mp3的漏端和第二nmos管mn2的漏端连接,第三pmos管mp3的源端、所述第三pmos管mp3的控制端和第二nmos管mn2的控制端连接输入电压vddin,所述第二nmos管mn2的源端接地;

41、其中,所述第三pmos管mp3的漏端和所述第四pmos管mp4的源端连接。

42、实施中,下电快速稳定电路还包括正压释放电路,所述正压释放电路包括:

43、反相器inv1;

44、第五pmos管mp5,所述第五pmos管mp5的源端接正压pvdd,所述第五pmos管mp5的控制端和漏端连接所述反相器inv1的电源;

45、第四nmos管mn4,所述第四nmos管mn4的漏端接正压pvdd,所述第四nmos管mn4的源端接地;

46、其中,所述反相器inv1的输入端连接使能信号en,所述反相器inv1的输出端连接第四nmos管mn4的控制端。

47、本技术实施例由于采用以上技术方案,具有以下技术效果:

48、驱动电路的正压端连接正压pvdd且负压端连接负压nvdd。在器件进入关闭状态时,正压pvdd和输入电压vddin都会被使能信号en快速拉到零电位,驱动电路的负压端的变化速度较慢。第一nmos管mn1的源端连接依然保持负压,第一nmos管mn1的控制端接地,此时第一nmos管mn1继续保持导通。第二偏置电压vb2控制第二pmos管mp2导通,第一偏置电压vb1控制第一pmos管mp1导通,使得负压第一释放电路放电。即在器件进入关闭状态时,第一nmos管mn1继续保持导通,第二pmos管mp2被控导通,第一pmos管mp1被控导通,整个负压第一释放电路连通,驱动电路的负压端被连接接地使得电位被降低到零,即驱动电路的负压端这个节点快速放电。驱动电路和器件电路本体连接,使得驱动电路和器件电路本体作为一个整体通过负压第一释放电路进行负压快速放电。因此器件在电源下电后很短的时间能够将器件内的寄生电容进行放电,使得能够再次快速启动。

- 还没有人留言评论。精彩留言会获得点赞!