时钟信号带宽调控电路及时钟信号带宽调控方法与流程

本发明涉及周期信号产生领域,特别是涉及一种时钟信号带宽调控电路及时钟信号带宽调控方法。

背景技术:

1、在数控装置和微处理机应用中,设备往往需要按照人们事先规定的顺序进行运算或操作,这就要求设备的控制部分不仅能正确地发出各种控制信号,而且要求这些控制信号在时间上有一定的先后顺序,即输出时序脉冲信号,以实现设备各部分的协调动作。通常采用的方法是,用脉冲信号进行时序控制。

2、现有的脉冲时钟产生电路均是通过输入时钟信号转换得到脉冲信号,这种脉冲信号会直接输出到后续器件。但是现有的脉冲时钟产生电路仅有一种工作模式(即:只能产生脉冲信号),当后续器件需要使用较大带宽的时钟信号时,脉冲时钟产生电路并不能提供相应的更大带宽的信号、存在使用的模式单一的问题。

3、基于此,本发明提供了一种新的时钟信号带宽调控电路,用以解决现有的脉冲时钟产生电路仅有一种工作模式的问题。

4、应该注意,上面对技术背景的介绍只是为了方便对本技术的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本技术的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种时钟信号带宽调控电路及时钟信号带宽调控方法,用于解决现有技术中脉冲时钟产生电路使用场景单一的问题。

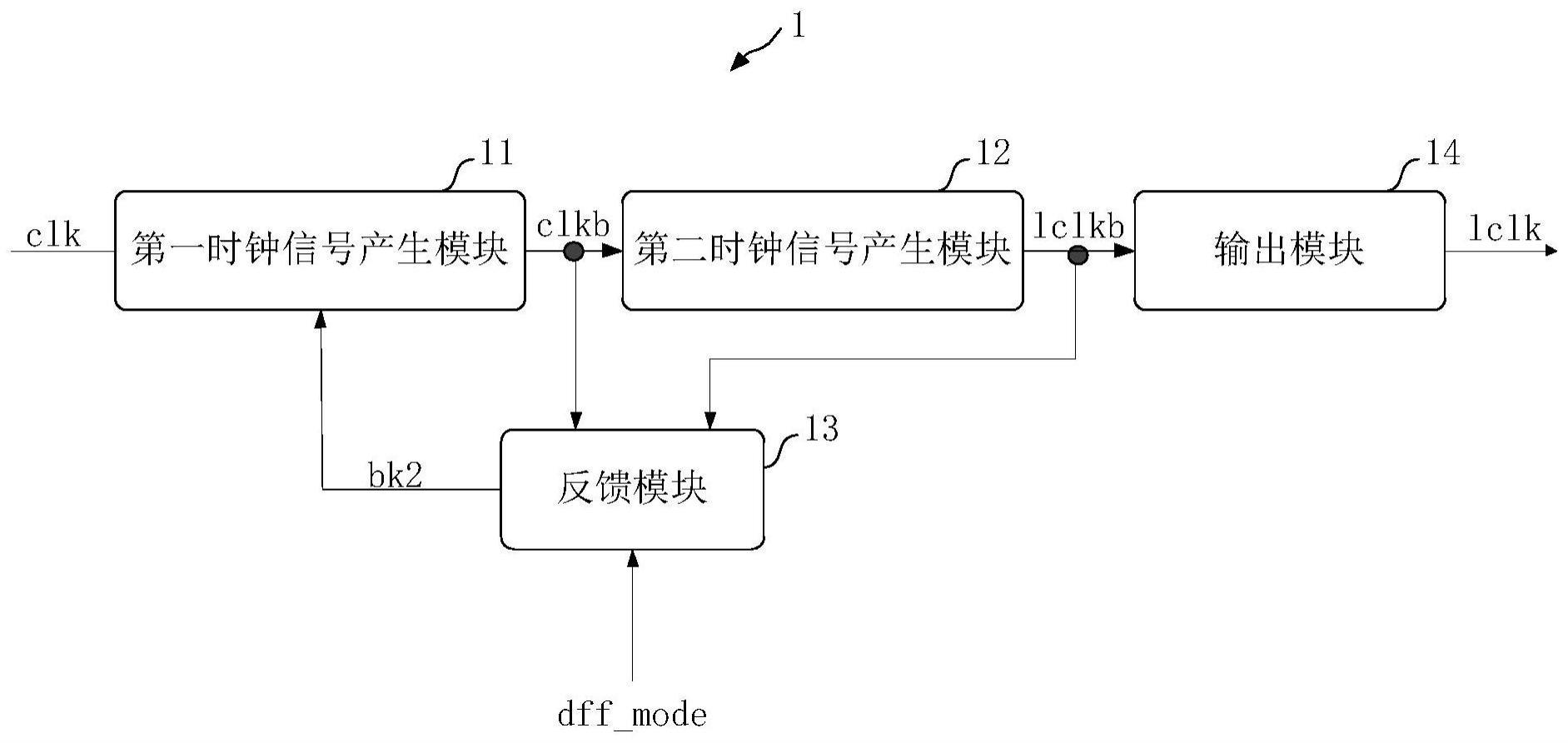

2、为实现上述目的及其他相关目的,本发明提供一种时钟信号带宽调控电路,包括:

3、第一时钟信号产生模块、第二时钟信号产生模块、反馈模块以及输出模块;

4、所述第一时钟产生模块连接所述反馈模块的输出端,并接收时钟信号,用于对所述时钟信号反相并延时得到第一时钟信号,并基于所述反馈模块输出的电平控制信号调控所述第一时钟信号的带宽;

5、所述第二时钟产生模块接收所述第一时钟信号,用于对所述第一时钟信号反相得到第二时钟信号;

6、所述反馈模块分别接收带宽控制信号、所述第一时钟信号以及所述第二时钟信号,在所述带宽控制信号作用下设置所述时钟信号带宽调控电路为窄带宽模式或宽带宽模式;在所述宽带宽模式下,所述反馈模块中的第二时钟信号失效,进而输出与所述第一时钟信号反相的电平控制信号,以维持所述第一时钟信号的带宽;在所述窄带宽模式下,所述反馈模块中的第二时钟信号有效,将所述第二时钟信号延时,并在延时的所述第二时钟信号的上升沿的预设时间内输出与所述第一时钟信号反相的电平控制信号,以缩短所述第一时钟信号的带宽;

7、所述输出模块连接所述第二时钟信号并输出。

8、可选地,所述第二时钟信号产生模块包括第一与非门与延时信号产生单元;所述延时信号产生单元连接所述第一时钟信号以及延时开关信号,当所述延时开关信号有效时,所述延时信号产生单元对所述第一时钟信号延时并得到延时信号;当所述延时开关信号无效时,所述延时信号无效;所述第一与非门的输入端分别接收所述第一时钟信号以及所述延时信号产生单元的输出信号,基于所述延时信号产生单元输出的信号得到所述第二时钟信号。

9、可选地,所述延时信号产生单元包括第二反相器以及第二与非门;所述第二反相器的输入端连接所述第一时钟信号;所述第二与非门的第一输入端连接所述第二反相器的输出端,第二输入端连接延时开关信号,输出端连接所述第一与非门,当所述延时开关信号有效时输出所述延时信号。

10、可选地,所述反馈模块包括第三反相器、第四nmos管、第五nmos管、第六nmos管、第四pmos管、第五pmos管、第六pmos管以及第三与非门;所述第三反相器的输入端连接所述带宽控制信号,输出端分别连接所述第四nmos管的栅极、第五nmos管的栅极以及所述第四pmos管的栅极;所述第四nmos管的源极接地,漏极连接所述第六nmos管的源极;所述第六nmos管的栅极连接所述第二时钟信号,漏极连接所述第七nmos管的栅极;所述第五pmos管的源极连接供电电压,栅极连接所述第二时钟信号,漏极连接所述第七nmos管的栅极;所述第五nmos管的源极接地,漏极连接所述第七nmos管的源极;所述第七nmos管的漏极连接所述第六pmos管的漏极;所述第六pmos管的源极连接所述供电电压,栅极连接所述第七nmos管的栅极,漏极连接所述第四pmos管的漏极;所述第四pmos管的源极连接所述供电电压,漏极连接所述第三与非门的第一输入端;所述第三与非门的第二输入端连接所述第一时钟信号,输出端作为所述反馈模块的输出端。

11、可选地,所述反馈模块还包括第一带宽调节单元;所述第一带宽调节单元设置于所述第五pmos管的源极与所述供电电压之间;所述第一带宽调节单元连接第一带宽调控信号,基于所述第一带宽调控信号调控所述电平控制信号的切换时间。

12、可选地,所述反馈模块还包括第二带宽调节单元;所述第二带宽调节单元连接于所述第五nmos管的漏极与参考地之间;所述第二带宽调节单元连接第二带宽调控信号,基于所述第二带宽调控信号调控所述电平控制信号的切换时间。

13、可选地,所述第一带宽调节单元包括第七pmos管以及第八pmos管,和/或,所述第二带宽调节单元包括第八nmos管;所述第一带宽调节单元中,所述第七pmos管的源极与所述第八pmos管的源极均连接所述供电电压,所述第七pmos管的漏极与所述第八pmos管的漏极均连接所述第五pmos管的源极;所述第七pmos管的栅极连接高电平电压;所述第八pmos管的栅极连接第一带宽调控信号。

14、可选地,所述第二带宽调节单元中,所述第八nmos管的源极接地,栅极连接所述第二带宽调控信号,漏极连接所述第五nmos管的漏极。

15、可选地,所述第一时钟产生模块包括第一pmos管、第二pmos管、第三pmos管、第一nmos管、第二nmos管、第三nmos管以及第一反相器;所述第一反相器的输入端连接所述时钟信号;所述第一nmos管的源极接地,栅极连接所述时钟信号,漏极作为所述第一时钟产生模块的输出端;所述第一pmos管的源极连接所述第二pmos管的漏极,栅极连接所述时钟信号,漏极连接所述第一nmos管的漏极;所述第二pmos管的源极连接供电电压,栅极连接所述第一反相器的输出端;所述第三pmos管的源极连接供电电压,栅极连接所述电平控制信号,漏极连接所述第二pmos管的漏极;所述第二nmos管的源极接地,栅极连接所述第一反相器的输出端,漏极连接所述第三nmos管的源极;所述第三nmos管的栅极连接所述电平控制信号,漏极连接所述第一nmos管的漏极。

16、可选地,所述输出模块包括第四反相器;所述第四反相器的输入端连接所述第二时钟信号,输出端作为所述输出模块的输出端。

17、为实现上述目的及其他相关目的,本发明提供一种时钟信号带宽调控方法,基于上述的时钟信号带宽调控电路实现,包括:

18、向所述时钟信号带宽调制电路提供时钟信号,并将所述时钟信号反相并延时得到第一时钟信号;

19、基于所述第一时钟信号反相得到第二时钟信号;

20、在所述带宽控制信号作用下设置所述时钟信号带宽调制电路为窄带宽模式或宽带宽模式;在所述宽带宽模式下,将输入到所述反馈模块中的第二时钟信号无效,进而输出与所述第一时钟信号反相的电平控制信号;在所述窄带宽模式下,将输入到所述反馈模块中的第二时钟信号延时并在延时的所述第二时钟信号的上升沿的预设时间内输出与所述第一时钟信号反相的电平控制信号;

21、基于所述电平控制信号调控所述第一时钟信号的带宽,进而将与所述第一时钟信号反相的所述第二时钟信号输出;在所述宽带宽模式下,所述第一时钟信号的带宽时间等于所述时钟信号的带宽时间;在所述窄带宽模式下,所述第一时钟信号的带宽时间等于所述预设时间;所述预设时间小于所述时钟信号的带宽时长。

22、可选地,基于所述第一时钟信号反相得到第二时钟信号时,所述时钟信号带宽调控方法还包括:提供一延时开关信号,当所述延时开关信号有效时,对所述第一时钟信号延时并反相得到第二时钟信号。

23、如上所述,本发明的时钟信号带宽调控电路及时钟信号带宽调控方法,具有以下有益效果:

24、1、本发明的时钟信号带宽调控电路及时钟信号带宽调控方法,通过设置了带宽控制信号,进而实现了时钟信号的窄带宽调制和宽带宽调制的切换,使得时钟信号产生电路使用场景更丰富。

25、2、本发明的时钟信号带宽调控电路及时钟信号带宽调控方法,通过设置了延时开关信号,可在后续使用过程中直接改变延时开关信号的高低电平,直接对时钟信号带宽调控电路的输出信号进行延时。

26、3、本发明的时钟信号带宽调控电路及时钟信号带宽调控方法,设置了第一带宽调控信号以及第二带宽调控信号,可在后续使用过程中直接改变这两种信号的高低电平,从而可进一步调控时钟信号带宽调控电路的输出窄带宽信号时的带宽。

27、4、本发明的时钟信号带宽调控电路及时钟信号带宽调控方法,结构简单、方法简便、能较好的推广应用。

- 还没有人留言评论。精彩留言会获得点赞!