一种存储器件的制造方法及存储器件与流程

本发明涉及半导体,特别是涉及一种存储器件的制造方法及存储器件。

背景技术:

1、在集成电路的应用过程中,各类器件的性能会受到各层材料之间的间距影响,尤其是存储器件,因为各层材料之间的间距,影响了器件的金属布线。

2、在实际操作过程中,本技术的研发人员发现,当前的半导体器件制造方案中,尤其是存储器件的制造,所形成的栅极结构的后道工艺中,金属布线精度要求较高,导致金属布线困难,影响了制造效率。

技术实现思路

1、本发明主要解决的技术问题是:提供一种存储器件的制造方法及存储器件,通过设置接触窗结构,能有效引出对应的源极和漏极,使得布线空间增大,降低金属布线精度要求,提高了制造效率。

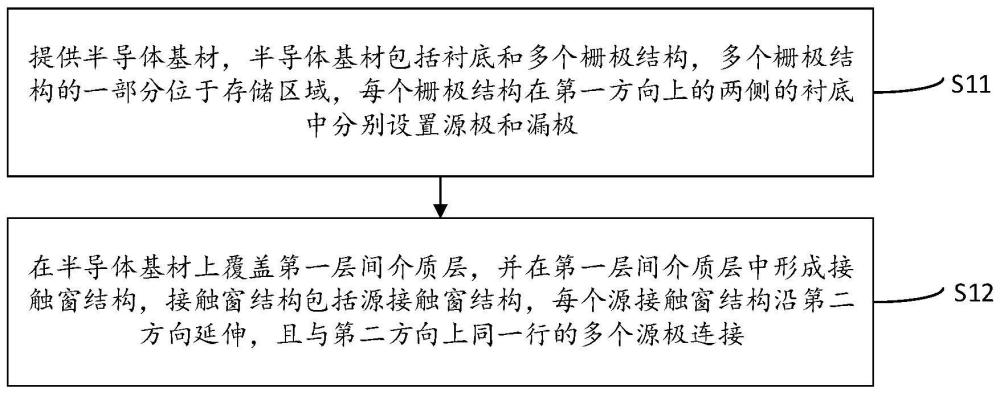

2、为解决上述技术问题,本技术采用的一技术方案是:提供一种半导体器件的制造方法,包括:提供半导体基材,所述半导体基材包括衬底和多个栅极结构,所述多个栅极结构的一部分位于存储区域,每个所述栅极结构在第一方向上的两侧的所述衬底中分别设置源极和漏极;在所述半导体基材上覆盖第一层间介质层,并在所述第一层间介质层中形成接触窗结构,所述接触窗结构包括源接触窗结构,每个所述源接触窗结构沿第二方向延伸,且与所述第二方向上同一行的多个所述源极连接。

3、在本技术一实施例中,所述多个栅极结构的另一部分位于引出区域,其中,所述存储区域的所述栅极结构位于所述衬底内,所述引出区域的所述栅极结构的至少部分位于所述衬底上。

4、在本技术一实施例中,所述提供半导体基材,包括:提供衬底,并在所述衬底上形成硬掩膜层;从所述硬掩膜层在所述衬底的有源区开设多个第一凹槽,所述多个第一凹槽的一部分位于所述存储区域,另一部分位于引出区域,其中,所述第一凹槽在所述衬底中的部分定义为基体凹槽;在所述基体凹槽的底部形成栅绝缘层和半浮栅,所述半浮栅的一部分与衬底接触,另一部分与所述衬底之间通过所述栅绝缘层隔离;在所述多个第一凹槽中分别形成栅间介质层和第一栅极层,移除所述存储区域的第一凹槽中的部分第一栅极层形成存储单元的控制栅,并以所述半浮栅和所述控制栅配合构成所述存储区域的所述栅极结构,保留所述引出区域的第一凹槽中的第一栅极层作为所述存储单元控制栅的引出线,所述引出线连接同一行的多个所述存储单元的所述控制栅,其中,以存储区域中的所述半浮栅和所述控制栅配合构成所述存储区域的所述栅极结构,并以引出区域的所述半浮栅和所述引出线配合构成所述引出区域的所述栅极结构。

5、在本技术一实施例中,在所述第二方向上,每隔预设数量的所述第一凹槽的所述引出区域的至少一个所述第一凹槽被屏蔽,保留所述引出区域的所述第一凹槽中部分的所述第一栅极层,其中,在所述第二方向上,同一行的所述第一凹槽中保留的所述第一栅极层,作为该行存储单元中所有控制栅的连接点,用于实现同一行存储单元的所述控制栅极层与外界的连接。

6、在本技术一实施例中,进一步包括:所述存储区域包括漏引出区域和源引出区域;在所述第一层间介质层上形成图案化的第一金属层,所述第一金属层包括源极线,所述源极线位于所述源引出区域,所述源极线沿所述第一方向延伸,与同一列的多个所述源接触窗结构连接。

7、在本技术一实施例中,所述在所述第一层间介质层上形成图案化的第一金属层,包括:在所述第一层间介质层上覆盖第二层间介质层,并在所述第二层间介质层中形成第一引出结构,所述第一引出结构包括源引出结构,所述源引出结构位于所述源引出区域,每个所述源引出结构对应一个所述源接触窗结构并与对应的所述源接触窗结构连接;在所述第二层间介质层上形成所述第一金属层,所述第一金属层中的所述源极线在所述源引出区域与同一列的多个所述源引出结构连接。

8、在本技术一实施例中,所述接触窗结构还包括漏接触窗结构,每个所述漏接触窗结构分别对应连接一个所述漏极;所述第一引出结构还包括漏引出结构,位于所述漏引出区域,每个所述漏引出结构分别连接对应一个所述漏接触窗结构;所述第一金属层还包括位线,位于所述漏引出区域,每个所述位线沿所述第一方向延伸,连接所述第一方向上同一列的多个所述漏引出结构。

9、在本技术一实施例中,所述多个栅极结构的另一部分位于引出区域;所述接触窗结构还包括控制栅接触窗结构,位于所述引出区域,每个所述控制栅接触窗结构与同一行的多个所述存储单元控制栅共用的引出线连接;所述第一引出结构还包括第一控制栅引出结构,位于所述引出区域,每个第一控制栅引出结构分别对应连接一个所述控制栅接触窗结构;所述第一金属层还包括控制栅触点,位于所述引出区域,每个所述控制栅触点分别连接一个所述第一控制栅引出结构。

10、在本技术一实施例中,进一步包括:在所述第一金属层上覆盖第三层间介质层,并在所述第三层间介质层中形成第二引出结构,所述第二引出结构包括第二控制栅引出结构,位于所述引出区域,每个所述第二控制栅引出结构分别对应连接一个所述控制栅触点;在所述第三层间介质层上形成图案化的第二金属层,所述第二金属层包括字线,每个所述字线沿所述第二方向延伸,并连接所述第二方向上同一行的所述控制栅触点。

11、为解决上述技术问题,本技术采用的另一技术方案是:提供一种存储器件,包括:衬底、多个栅极结构、第一层间介质层、多个源接触窗结构;其中,所述多个栅极结构的一部分位于存储区域,在每个所述栅极结构在第一方向上的两侧分别设置有漏极和源极;第一层间介质层覆盖所述衬底、所述栅极结构、所述漏极和所述源极;多个源接触窗结构位于所述第一层间介质层中,每个所述源接触窗结构沿第二方向延伸,并与所述第二方向上同一行的多个所述栅极结构对应的所述源极连接。

12、在本技术一实施例中,所述多个栅极结构的另一部分位于引出区域,其中,所述存储区域的所述栅极结构位于所述衬底内,所述引出区域的所述栅极结构的至少部分位于所述衬底上。

13、在本技术一实施例中,所述栅极结构包括:半浮栅,半浮栅位于所述衬底的基体凹槽的底部,所述半浮栅的一部分与所述衬底接触,另一部分通过栅绝缘层与所述衬底隔离,其中,所述存储区域的所述栅极结构还包括控制栅,所述控制栅位于所述半浮栅上,并通过栅间介质层与所述半浮栅隔离;所述引出区域的所述栅极结构还包括引出线,所述引出线的至少部分位于所述衬底上并作为存储单元控制栅的引出线,所述引出线连接同一行的多个存储单元的所述控制栅。

14、在本技术一实施例中,在所述第二方向上,每隔预设数量的所述控制栅至少设置一个对应的引出线,所述引出线作为连接点,用于实现同一行多个所述控制栅与外界的连接。

15、在本技术一实施例中,所述存储区域包括漏引出区域和源引出区域;所述存储器件还包括:第二层间介质层、多个源引出结构和第一金属层,其中,第二层间介质层覆盖所述第一层间介质层和所述第一金属层;多个源引出结构位于所述源引出区域的所述第二层间介质层中,每个所述源引出结构对应一个所述源接触窗结构,并与对应的源接触窗结构连接;第一金属层位于所述第二层间介质层上,所述第一金属层中的源极线在所述源引出区域与同一列的多个所述源引出结构连接。

16、在本技术一实施例中,还包括:多个漏接触窗结构、多个漏引出结构和多个位线;其中,多个漏接触窗结构位于所述第一层间介质层中,每个所述漏接触窗结构分别对应连接一个所述漏极;多个漏引出结构位于所述漏引出区域的所述第二层间介质层中,每个所述漏引出结构分别对应连接一个所述漏接触窗结构;所述第一金属层包括位于所述漏引出区域的多个位线,每个所述位线沿所述第一方向延伸,连接所述第一方向上同一列的多个所述漏引出结构。

17、在本技术一实施例中,还包括:多个控制栅接触窗结构、多个第一控制栅引出结构和多个控制栅触点;其中,多个控制栅接触窗结构位于所述第一层间介质层中,每个所述控制栅接触窗结构与同一行的多个存储单元控制栅共用的引出线在所述引出区域连接;多个第一控制栅引出结构位于所述引出区域的所述第二层间介质层中,每个所述第一控制栅引出结构分别对应连接一个所述控制栅接触窗结构;所述第一金属层包括位于所述引出区域上的多个控制栅触点,每个所述控制栅触点分别连接一个所述第一控制栅引出结构。

18、在本技术一实施例中,还包括:第三层间介质层、多个第二控制栅引出结构和第二金属层;其中,第三层间介质层覆盖在所述第一金属层上;多个第二控制栅引出结构位于所述引出区域的所述第三层间介质层中,每个所述第二控制栅引出结构分别对应连接一个所述控制栅触点;第二金属层位于所述第三层间介质层上,所述第二金属层中的字线沿第二方向延伸,并连接所述第二方向上同一行的所述控制栅触点。

19、区别于现有技术,本技术提供的存储器件的制造方法,包括:提供半导体基材,所述半导体基材包括衬底和多个栅极结构,所述多个栅极结构的一部分位于存储区域,另一部分位于源引出区域,每个所述栅极结构在第一方向上的两侧的所述衬底上分别设置源极和漏极;在所述半导体基材上覆盖第一层间介质层,并在所述第一层间介质层中形成接触窗结构,所述接触窗结构包括源接触窗结构,每个所述源接触窗结构沿第二方向延伸,且与所述第二方向上同一行的多个所述源极连接。即本技术中设置接触窗结构,能有效引出对应的源极和漏极,使得布线空间增大,降低金属布线精度要求,提高了制造效率。

- 还没有人留言评论。精彩留言会获得点赞!