多位宽二进制多路选择器及降低其扇出的方法和系统与流程

本申请涉及数字电路,特别涉及多位宽二进制多路选择器的设计。

背景技术:

1、本部分旨在为权利要求书中陈述的本申请的实施方式提供背景或上下文。本部分中的内容仅供参考,并不构成对其作为已被公开的现有技术的承认或确认。

2、二进制复用器(binary-mux)是数字电路设计中一种关键组件,它集数据路径和控制逻辑于一体。作为多路复用器(mux)的一种特殊形式,binary-mux的设计基于选择信号(sel)的位宽。当选择信号的位宽为n位时,该复用器可接收2n个输入信号。具体来说,这些输入信号可表示为d0、d1、d2…d(2n-1),而选择信号sel具有n位宽,输出信号则标记为out。binary-mux的标准电路结构,如图1所示,由(2n-1)个2-to-1mux(mux21)构成,实现2n选1的功能。

3、在实际应用中,binary-mux通常设计为多数据位宽形式。例如,若图1所示的binary-mux具有m位数据宽度,则其输入信号可表示为d0[m-1:0]、d1[m-1:0]、d2[m-1:0]…d(2n-1)[m-1:0],相应的输出信号则为out[m-1:0]。在这种情况下,图1中的每个mux21实际上代表m个单独的mux21,从而使得总的mux21数量增加至m*2n个。

4、图1中,sel[0]信号的扇出数量是整个电路中最大的,其值为m*2n-1。在数字电路的布局和布线过程中,信号的扇出数量直接影响设计的复杂度和电路的延时。扇出数量越大,布局和布线过程中的拥挤度越高,电路元件间的互连线越长,从而导致延时增加,进而降低电路的最大工作频率(fmax)。

5、为减少扇出,常见的做法是在电路中插入缓冲器(buf)元件,如图2所展示。在图2中,通过在sel[0]的输出端插入一个缓冲器,并重新调整电路结构,可以使sel[0]只驱动原来一半的mux21,而缓冲器则驱动剩余的mux21,实现将sel[0]的扇出数量减少50%。然而,这种传统的缓冲器插入方法的缺点在于,缓冲器自身作为额外的电路元件,需要布局和布线,占用了额外的资源。

技术实现思路

1、本申请的目的在于提供一种多位宽二进制多路选择器及降低其扇出的方法和系统,在不使用额外电路元件的前提下,降低多位宽二进制多路选择器的扇出最大值。

2、本申请公开了一种降低多位宽二进制多路选择器扇出的方法,其中,所述多路选择器的数据位宽为m,选择端位宽为n,m和n均为大于1的整数;所述方法包括:

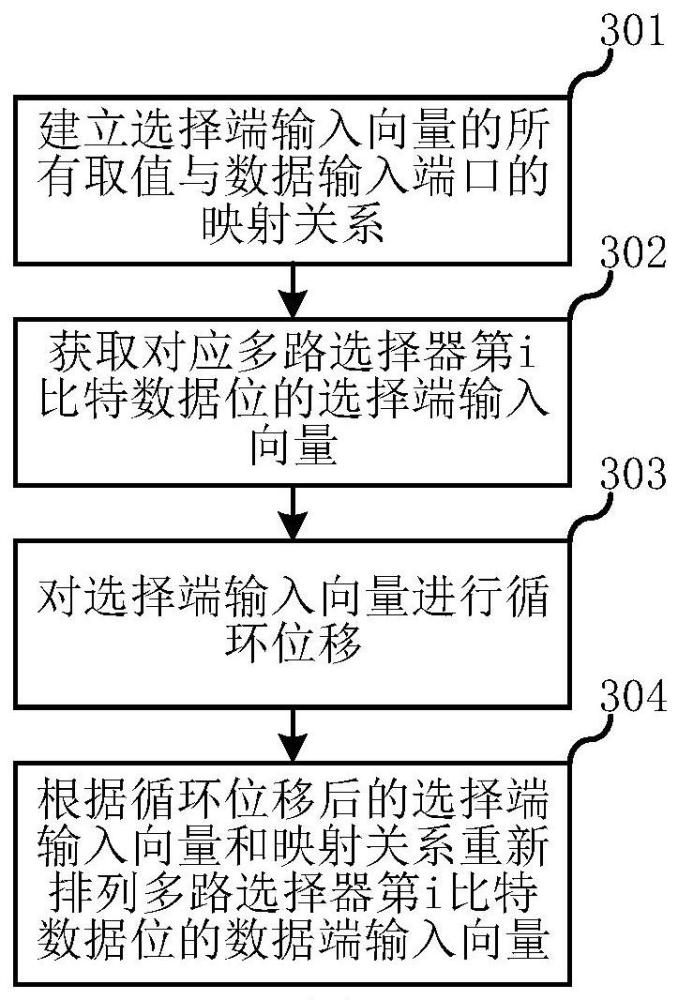

3、建立选择端输入向量的所有取值与数据输入端口的映射关系;

4、至少执行一次以下调整步骤:

5、获取对应所述多路选择器第i比特数据位的选择端输入向量;

6、对所述选择端输入向量进行循环位移;

7、根据循环位移后的选择端输入向量和所述映射关系重新排列所述多路选择器第i比特数据位的数据端输入向量,其中i是用于指示所述多路选择器m个比特数据位中一个比特数据位的整数。

8、可选的,根据循环位移后的选择端输入向量和所述映射关系重新排列所述多路选择器第i比特数据位的数据端输入向量,进一步包括:

9、根据循环位移后的选择端输入向量的2n个有序二进制数取值分别查询所述映射关系,获得对应的数据输入端口,将所得的各个数据输入端口排列后得到数据端输入向量。

10、可选的,对于所述多路选择器的m个比特数据位,分别执行所述调整步骤,使得对应多路选择器不同比特数据位的选择端输入向量各不相同。

11、可选的,所述调整步骤进一步包括:

12、获取对应所述多路选择器第1比特数据位的选择端输入向量,作为当前的选择端输入向量,初始化i,并且m次循环执行如下步骤:

13、对当前的选择端输入向量循环左移1比特,得到更新后的当前的选

14、择端输入向量;

15、根据所述更新后的当前的选择端输入向量和所述映射关系重新排

16、列所述多路选择器第i比特数据位的数据端输入向量;

17、i增加1。

18、可选的,在所述调整步骤之后,执行以下步骤以计算扇出最大值:

19、步骤a,初始化最大扇出变量和i变量;

20、步骤b,获取所述多路选择器的第i比特选择位;

21、步骤c,判断i是否小于n,如果是则进入步骤d,否则结束本流程,将当前的最大扇出变量作为扇出最大值输出;

22、步骤d,初始化扇出变量和j变量;

23、步骤e,获取所述多路选择器的第j比特数据位;

24、步骤f,判断j是否小于m,如果是则进入步骤g,否则进入步骤i;

25、步骤g,计算rem=(j+i)%n,扇出变量=扇出变量+2n-rem-1;

26、步骤h,j变量增加1,此后回到步骤f;

27、步骤i,判断所述扇出变量是否大于所述最大扇出变量,如果是则进入步骤j,否则进入步骤k;

28、步骤j,将所述最大扇出变量设置为所述扇出变量的值;

29、步骤k,i变量增加1,此后回到步骤b。

30、本申请还公开了采用上述方法得到一种多位宽二进制多路选择器。

31、本申请还公开了一种降低多位宽二进制多路选择器扇出的系统,包括:

32、存储器,用于存储计算机可执行指令;以及,

33、处理器,与所述存储器耦合,用于在执行所述计算机可执行指令时实现上述方法中的步骤。

34、本申请还公开了一种计算机可读存储介质,该计算机可读存储介质中存储有计算机可执行指令,所述计算机可执行指令被处理器执行时实现上述方法中的步骤。

35、本申请的实施方式中,通过对多位宽binary-mux的选择端输入与数据端输入进行重新排列,在不使用额外电路元件的前提下,大幅降低了多位宽binary-mux的扇出最大值。

36、上述

技术实现要素:

中公开的各个技术特征、在下文各个实施方式和例子中公开的各技术特征、以及附图中公开的各个技术特征,都可以自由地互相组合,从而构成各种新的技术方案(这些技术方案均应该视为在本说明书中已经记载),除非这种技术特征的组合在技术上是不可行的。例如,在一个例子中公开了特征a+b+c,在另一个例子中公开了特征a+b+d+e,而特征c和d是起到相同作用的等同技术手段,技术上只要择一使用即可,不可能同时采用,特征e技术上可以与特征c相组合,则,a+b+c+d的方案因技术不可行而应当不被视为已经记载,而a+b+c+e的方案应当视为已经被记载。

技术特征:

1.一种降低多位宽二进制多路选择器扇出的方法,其特征在于,所述多路选择器的数据位宽为m,选择端位宽为n,m和n均为大于1的整数;所述方法包括:

2.如权利要求1所述的降低多位宽二进制多路选择器扇出的方法,其特征在于,根据循环位移后的选择端输入向量和所述映射关系重新排列所述多路选择器第i比特数据位的数据端输入向量,进一步包括:

3.如权利要求1所述的降低多位宽二进制多路选择器扇出的方法,其特征在于,对于所述多路选择器的m个比特数据位,分别执行所述调整步骤,使得对应多路选择器不同比特数据位的选择端输入向量各不相同。

4.如权利要求3所述的降低多位宽二进制多路选择器扇出的方法,其特征在于,所述调整步骤进一步包括:

5.如权利要求1所述的降低多位宽二进制多路选择器扇出的方法,其特征在于,在所述调整步骤之后,执行以下步骤以计算扇出最大值:

6.如权利要求1所述的降低多位宽二进制多路选择器扇出的方法,其特征在于,所述步骤a中,将所述最大扇出变量和所述i变量都初始化为0。

7.如权利要求1所述的降低多位宽二进制多路选择器扇出的方法,其特征在于,所述步骤d中,将所述扇出变量和所述j变量都初始化为0。

8.一种多位宽二进制多路选择器,其特征在于,采用所述权利要求1-7中任意一项所述的方法得到。

9.一种降低多位宽二进制多路选择器扇出的系统,其特征在于,包括:

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质中存储有计算机可执行指令,所述计算机可执行指令被处理器执行时实现如权利要求1至7中任意一项所述的方法中的步骤。

技术总结

本申请涉及数字电路,公开了一种多位宽二进制多路选择器及降低其扇出的方法和系统,可以在不使用额外电路元件的前提下,降低多位宽二进制多路选择器的扇出最大值。该方法包括:建立选择端输入向量的所有取值与数据输入端口的映射关系;至少执行一次以下调整步骤:获取对应所述多路选择器第i比特数据位的选择端输入向量,对所述选择端输入向量进行循环位移,根据循环位移后的选择端输入向量和所述映射关系重新排列所述多路选择器第i比特数据位的数据端输入向量。

技术研发人员:金健,余建德

受保护的技术使用者:上海安路信息科技股份有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!