用于多电压域统一架构的多电平输出电路及方法与流程

本发明属于微电子领域,涉及一种多电平输出电路,尤其涉及一种用于多电压域统一架构的多电平输出电路及方法。

背景技术:

1、在高性能计算、通信和数据处理等电子系统中,尤其是在高性能电子系统中电源系统的噪声要求很高,且需要双电源3.3v和2.5v,需要适用不同的协议和电平标准,对应多个电源电压和电平类型。传统的设计方法是采用标准的三极管型电流模逻辑(cml结构)实现,通过对输出尾电流的配置实现lvpecl、lvds和cml等差分电平的输出。此方法与工艺密切相关,对器件要求极高,设计难度大。cmos工艺平台实现多数情况下需要分别对lvpecl、lvds以及cml等电平输出电路进行设计,以满足输出电平要求,但提高了电路和版图设计的复杂度,输出寄生较大,无法适用于高频高性能通信领域中。

技术实现思路

1、为了解决现有技术的问题,本发明提出了一种电路结构简单、电源适应性强以及工艺易实现的用于多电压域统一架构的多电平输出电路及方法。

2、为了实现上述目的,本发明采用如下技术方案:

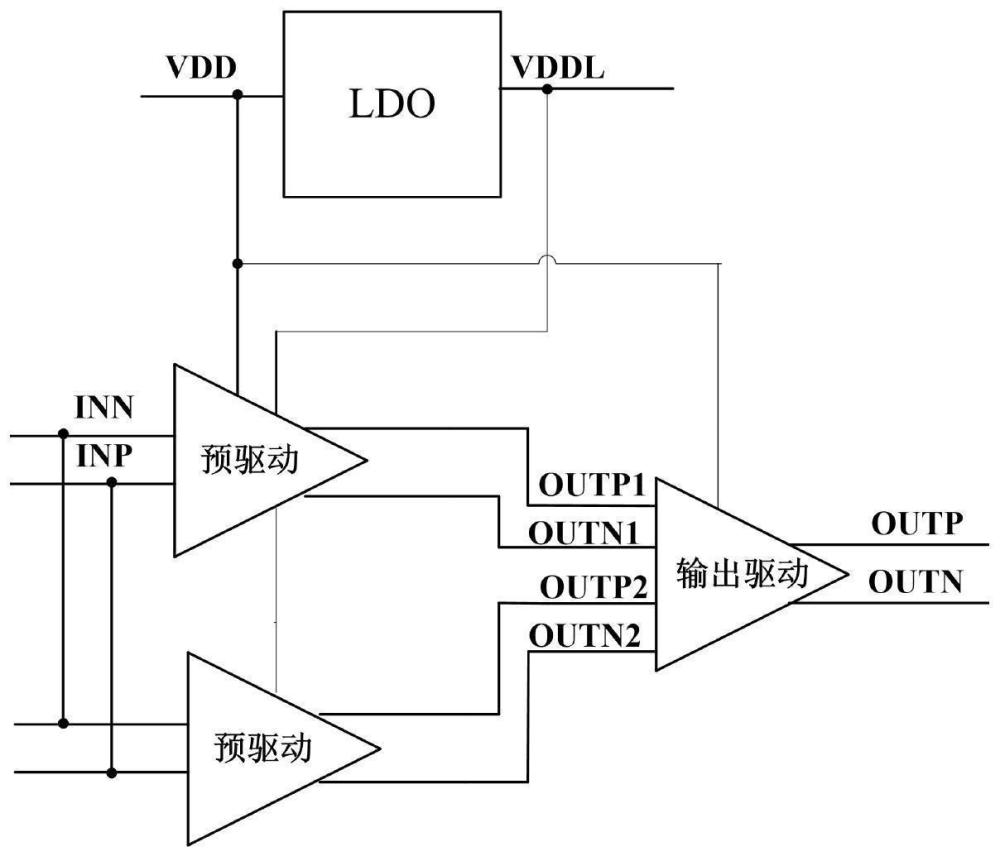

3、一种用于多电压域统一架构的多电平输出电路,其特征在于:所述用于多电压域统一架构的多电平输出电路包括正向差分信号inp输入端、负向差分信号inn输入端、电源供给电路、第一级预驱动电路、第二级预驱动电路、输出驱动电路、正向差分信号outp输出端以及负向差分信号outn输出端;所述正向差分信号inp输入端以及负向差分信号inn输入端分别通过第一级预驱动电路接入输出驱动电路;所述正向差分信号inp输入端以及负向差分信号inn输入端分别通过第二级预驱动电路接入输出驱动电路;所述电源供给电路分别与第一级预驱动电路、第二级预驱动电路以及输出驱动电路相连;所述输出驱动电路分别与正向差分信号outp输出端以及负向差分信号outn输出端相连。

4、上述电源供给电路包括电源vdd以及低压差线性稳压器ldo;所述电源vdd通过低压差线性稳压器ldo形成二次电源vddl;所述电源vdd分别接入第一级预驱动电路以及输出驱动电路;所述二次电源vddl分别接入第一级预驱动电路以及第二级预驱动电路。

5、上述第一级预驱动电路包括动态电流源i1、开关φ1、开关φ2、开关φ3、开关φ4、电阻r1、电阻r2、晶体管mn1、晶体管mn2、第一级预驱动正向差分信号outp1输出端以及第一级预驱动负向差分信号outn1输出端;所述动态电流源i1的一端接地,另一端分别与晶体管mn1以及晶体管mn2相连;所述正向差分信号inp输入端接入晶体管mn1;所述负向差分信号inn输入端接入晶体管mn2;所述电源vdd分别接入开关φ1以及开关φ2;所述二次电源vddl分别接入开关φ3以及开关φ4;所述晶体管mn1通过电阻r1接入开关φ1或开关φ3;所述晶体管mn2通过电阻r2接入开关φ2或开关φ4;所述电阻r1通过第一级预驱动负向差分信号outn1输出端接入输出驱动电路;所述电阻r2通过第一级预驱动正向差分信号outp1输出端接入输出驱动电路。

6、上述动态电流源i1分别与晶体管mn1的源极以及晶体管mn2的源极相连;所述正向差分信号inp输入端与晶体管mn1的栅极相连;所述负向差分信号inn输入端与晶体管mn2的栅极相连;所述晶体管mn1的漏极通过电阻r1接入开关φ1或开关φ3;所述晶体管mn2的漏极通过电阻r2接入开关φ2或开关φ4。

7、上述第二级预驱动电路包括电阻r3、电阻r4、晶体管mn3、晶体管mn4、第二级预驱动正向差分信号outp2输出端、第二级预驱动负向差分信号outn2输出端以及稳定电流源i2;所述稳定电流源i2的一端接地,另一端分别与晶体管mn3以及晶体管mn4相连;所述正向差分信号inp输入端接入晶体管mn3;所述负向差分信号inn输入端接入晶体管mn4;所述二次电源vddl通过电阻r3接入晶体管mn3;所述二次电源vddl通过电阻r4接入晶体管mn4;所述电阻r3通过第二级预驱动负向差分信号outn2输出端接入输出驱动电路;所述电阻r4通过第二级预驱动正向差分信号outp2输出端接入输出驱动电路。

8、上述稳定电流源i2分别与晶体管mn3的源极以及晶体管mn4的源极相连;所述正向差分信号inp输入端与晶体管mn3的栅极相连;所述负向差分信号inn输入端与晶体管mn4的栅极相连;所述晶体管mn3的漏极接入电阻r3;所述晶体管mn4的漏极接入电阻r4。

9、上述输出驱动电路包括开关φ5、开关φ6、开关φ7、开关φ8以及动态电流源i3;所述电源vdd分别与开关φ5以及开关φ6相连;所述动态电流源i3的一端接地,另一端分别与开关φ7和开关φ8相连;所述第一级预驱动正向差分信号outp1输出端通过开关φ5接入正向差分信号outp输出端;所述第一级预驱动负向差分信号outn1输出端通过开关φ6接入负向差分信号outn输出端;所述第二级预驱动正向差分信号outp2输出端通过开关φ8、开关φ6以及开关φ5接入正向差分信号outp输出端;所述第二级预驱动负向差分信号outn2输出端通过开关φ7、开关φ5以及开关φ6接入负向差分信号outn输出端。

10、一种基于如前所述的用于多电压域统一架构的多电平输出电路的多电平输出方法,其特征在于:所述方法包括以下步骤:

11、1)获取电源vdd以及二次电源vddl;

12、2)基于步骤1)获取得到的电源vdd以及二次电源vddl,根据待输出电平的类型分别调控第一级预驱动电路、第二级预驱动电路以及输出驱动电路;所述待输出电平的类型是lvpecl电平输出、lvds电平输出或cml电平输出;

13、3)根据调控结果分别进行lvpecl电平输出、lvds电平输出或cml电平输出。

14、上述步骤1)中,所述二次电源vddl的电压低于电源vdd的电压;所述电源vdd通过低压差线性稳压器ldo产生二次电源vddl。

15、上述待输出电平的类型是lvpecl电平输出时,所述步骤2)的具体实现方式是:在电源vdd或二次电源vddl作用下,通过晶体管mn1接收正向差分信号inp,通过晶体管mn2接收负向差分信号inn,控制开关φ1和φ2开启,开关φ3和φ4关断,同时增大动态电流源i1,形成并促使第一级预驱动正向差分信号outp1以及第一级预驱动负向差分信号outn1高电平升高;通过晶体管mn3接收正向差分信号inp,通过晶体管mn4接收负向差分信号inn,在二次电源vddl作用下,通过稳定电流源i2和电阻r3或电阻r4产生第二级预驱动正向差分信号outp2以及第二级预驱动负向差分信号outn2;

16、所述待输出电平的类型是lvds电平输出时,所述步骤2)的具体实现方式是:在二次电源vddl的作用下,通过晶体管mn1接收正向差分信号inp,通过晶体管mn2接收负向差分信号inn,控制开关φ3和φ4开启,开关φ1和φ2关断,同时减小动态电流源i1,形成并输出第一级预驱动正向差分信号outp1以及第一级预驱动负向差分信号outn1;通过晶体管mn3接收正向差分信号inp,通过晶体管mn4接收负向差分信号inn,在二次电源vddl下,通过稳定电流源i2和电阻r3或电阻r4产生第二级预驱动正向差分信号outp2以及第二级预驱动负向差分信号outn2;

17、所述待输出电平的类型是cml电平输出时,所述步骤2)的具体实现方式是:在二次电源vddl的作用下,通过晶体管mn1接收正向差分信号inp,通过晶体管mn2接收负向差分信号inn,控制开关φ3和φ4开启,开关φ1和φ2关断,同时减小动态电流源i1,形成并输出第一级预驱动正向差分信号outp1以及第一级预驱动负向差分信号outn1;通过晶体管mn3接收正向差分信号inp,通过晶体管mn4接收负向差分信号inn,在二次电源vddl下,通过稳定电流源i2和电阻r3或电阻r4产生第二级预驱动正向差分信号outp2以及第二级预驱动负向差分信号outn2。

18、本发明的优点是:

19、本发明提供了一种用于多电压域统一架构的多电平输出电路及方法,由两级预驱动电路和输出驱动电路组成,通过低压差线性稳压器ldo产生内部二次电源vddl,两级预驱动电路通过电源vdd、二次电源vddl与多组逻辑控制开关φ1~φ4、尾电流i1~i2的配合,输出两组差分对outp1/outn1和outp2/outn2,分别使输出驱动电路中φ5~φ6和φ7~φ8正常开断,其中φ5~φ8可以用nmos管、pmos管或者nmos管及pmos管组成的传输门实现;φ5~φ8开关管配合尾电流i3,通过开关管的输出阻抗和尾电流的大小实现lvpecl、lvds、cml等多种差分电平的驱动输出。本发明能够有效隔离电源噪声且适配性强,与多组逻辑控制开关、尾电流的配合,实现lvpecl、lvds、cml等多种差分电平的驱动输出,电路原理简单易实现,工艺移植性强,版图规模小且寄生小,尤其在ghz以上的通信应用中信号性能好。

- 还没有人留言评论。精彩留言会获得点赞!