一种基于芯片时钟信号检测与切换电路的芯片时钟电路的制作方法

本发明涉及芯片设计,更具体的说是涉及一种基于芯片时钟信号检测与切换电路的芯片时钟电路。

背景技术:

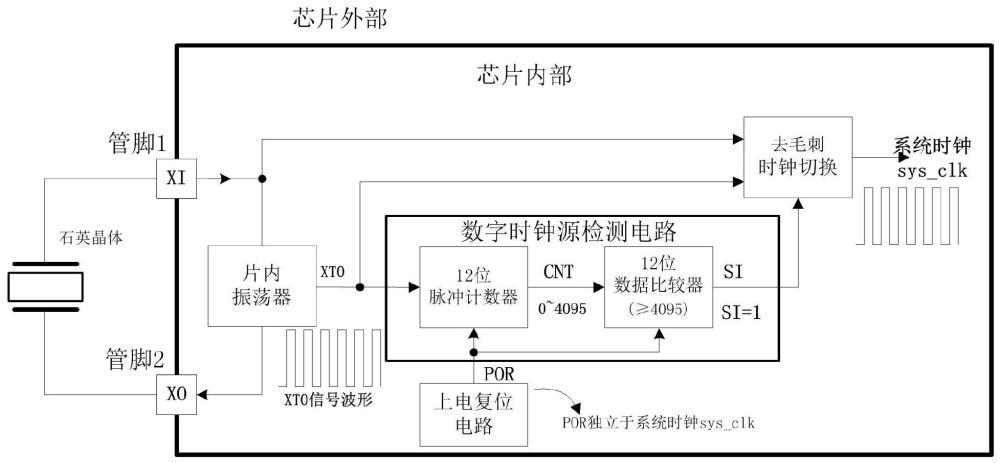

1、芯片系统时钟通常采用芯片内部的石英晶体振荡器电路(称为内部时钟信号模式,参见附图1所示)或者直接从芯片管脚输入时钟(称为外部时钟信号模式,参见附图2所示),内、外部两种时钟信号模式,可供芯片用户自由选择。

2、目前,芯片需要2个专用于内部时钟信号的芯片管脚xi,xo(xi,xo分别外接石英晶体振荡器的两个端子)、1个专用于外部时钟信号的芯片管脚ci、以及至少2个串行接口管脚,即芯片总共需要至少5个管脚才能实现时钟信号的检测和切换:用户通过串行接口配置方式,将当前使用的时钟信号模式配置到模式寄存器,芯片根据模式寄存器值,选用相应的时钟信号作为系统时钟,例如:当模式寄存器值为0,选用内部时钟信号、若模式寄存器值为1,则选用外部时钟信号作为系统时钟。可见,现有的芯片时钟信号检测和切换至少需要5个芯片管脚、并且要求用户配置芯片。

3、但是,芯片管脚数量增加,会导致芯片制造和封装成本的增加,特别对于芯片管脚数量小于8的芯片,每增加1个芯片管脚,芯片成本增加10%~15%以上。

4、因此,如何提供一种仅需2个芯片管脚就能实现时钟信号检测与切换的电路是本领域技术人员亟需解决的问题。

技术实现思路

1、有鉴于此,本发明提供了一种基于芯片时钟信号检测与切换电路的芯片时钟电路,解决了现有技术中需要至少5个管脚且需要用户通过串口配置时钟信号模式的问题,既降低了芯片成本,也提高了用户使用便捷性。

2、为了实现上述目的,本发明采用如下技术方案:

3、一种基于芯片时钟信号检测与切换电路的芯片时钟电路,包括:第一管脚、第二管脚、片内振荡器、数字时钟源检测电路、上电复位电路和去毛刺时钟切换电路;

4、所述第一管脚分别与所述片内振荡器的输入端和所述去毛刺时钟切换电路的第一输入端相连;

5、所述片内振荡器的第一输出端与所述第二管脚相连,所述片内振荡器的第二输出端与所述去毛刺时钟切换电路的第二输入端相连,所述片内振荡器的第三输出端与所述数字时钟源检测电路的输入端相连;

6、所述上电复位电路与所述数字时钟源检测电路的复位端相连;

7、所述数字时钟源检测电路的输出端与所述去毛刺时钟切换电路的第三输入端相连;

8、所述去毛刺时钟切换电路输出最终的系统时钟。

9、进一步的,所述数字时钟源检测电路中包括顺序串联的脉冲计数器和数据比较器;

10、所述片内振荡器的第三输出端与所述脉冲计数器的输入端相连;

11、所述脉冲计数器的输出端与所述数据比较器的输入端相连;

12、所述数据比较器的输出端与所述去毛刺时钟切换电路的第三输入端相连;

13、所述上电复位电路分别与所述脉冲计数器的清零端和所述数据比较器的复位端相连。

14、进一步的,所述去毛刺时钟切换电路包括第一与门、第二与门、第三与门、第四与门、或门、反相器、第一d触发器和第二d触发器;

15、所述数字时钟源检测电路的输出信号输入所述第一与门的一输入端,所述第一与门的另一输入端与所述第二d触发器的一输出端相连,所述第一与门的输出端与所述第一d触发器的一输入端相连,所述第一d触发器的一输出端与所述第四与门的一输入端相连,所述第一d触发器的另一输出端与所述第二与门的一输入端相连;

16、所述数字时钟源检测电路的输出信号经所述反相器与所述第二与门的另一输入端相连,所述第二与门的输出端与所述第二d触发器的一输入端相连,所述第二d触发器的另一输出端与所述第三与门的一输入端相连;

17、所述片内振荡器的输出信号分别输入所述第一d触发器的另一输入端和所述第四与门and4的另一输入端;

18、所述第一管脚分别与所述第二d触发器的另一输入端和所述第三与门的另一输入端相连;

19、所述第三与门的输出端和所述第四与门的输出端分别与所述或门的两个输入端相连;

20、所述或门输出最终的系统时钟。

21、进一步的,内部时钟信号模式下,内部时钟信号模式下,所述第一管脚与所述第二管脚分别外接晶体振荡器的两个端子;

22、外部时钟信号模式下,所述第一管脚外接片外时钟源,所述第二管脚浮空。

23、进一步的,内部时钟信号模式下:

24、所述脉冲计数器将所述片内振荡器输出的xto脉冲作为计数时钟,每出现一个xto脉冲,所述脉冲计数器的计数值加1,并将所述计数值发送给所述数据比较器,当所述计数值累加到预设值时停止计数;

25、所述数据比较器将接收到的所述计数值与所述预设值进行比较,当所述计数值≥所述预设值时,所述数据比较器输出高电平。

26、进一步的,外部时钟信号模式下:

27、所述片内振荡器始终输出低电平,所述计数值始终为0,即所述计数值<所述预设值,所述数据比较器输出低电平。

28、进一步的,所述预设值为十进制数据4095。

29、经由上述的技术方案可知,与现有技术相比,本发明公开提供了一种基于芯片时钟信号检测与切换电路的芯片时钟电路,仅通过2个芯片管脚、且无需用户通过串口配置时钟信号模式,便可自动检测芯片的时钟信号模式,并将检测到的时钟信号切换为系统时钟源,降低了芯片成本,也提高了用户使用便捷性。

技术特征:

1.一种基于芯片时钟信号检测与切换电路的芯片时钟电路,其特征在于,包括:第一管脚、第二管脚、片内振荡器、数字时钟源检测电路、上电复位电路和去毛刺时钟切换电路;

2.根据权利要求1的一种基于芯片时钟信号检测与切换电路的芯片时钟电路,其特征在于,所述数字时钟源检测电路中包括顺序串联的脉冲计数器和数据比较器;

3.根据权利要求1的一种基于芯片时钟信号检测与切换电路的芯片时钟电路,其特征在于,所述去毛刺时钟切换电路包括第一与门、第二与门、第三与门、第四与门、或门、反相器、第一d触发器和第二d触发器;

4.根据权利要求1的一种基于芯片时钟信号检测与切换电路的芯片时钟电路,其特征在于,内部时钟信号模式下,所述第一管脚与所述第二管脚分别外接晶体振荡器的两个端子;

5.根据权利要求2的一种基于芯片时钟信号检测与切换电路的芯片时钟电路,其特征在于,内部时钟信号模式下:

6.根据权利要求5的一种基于芯片时钟信号检测与切换电路的芯片时钟电路,其特征在于,外部时钟信号模式下:

7.根据权利要求5或6的一种基于芯片时钟信号检测与切换电路的芯片时钟电路,其特征在于,所述预设值为十进制数据4095。

技术总结

本发明公开了一种基于芯片时钟信号检测与切换电路的芯片时钟电路,包括:第一管脚、第二管脚、片内振荡器、数字时钟源检测电路、上电复位电路和去毛刺时钟切换电路;第一管脚分别与片内振荡器的输入端和去毛刺时钟切换电路的输入端相连;片内振荡器输出端分别与第二管脚、去毛刺时钟切换电路的输入端以及数字时钟源检测电路的输入端相连;上电复位电路与数字时钟源检测电路的复位端相连;数字时钟源检测电路的输出端与去毛刺时钟切换电路的输入端相连;去毛刺时钟切换电路输出最终的系统时钟。本发明仅通过2个芯片管脚、且无需用户通过串口配置时钟信号模式,便可自动检测芯片的时钟信号模式,并将检测到的时钟信号切换为系统时钟源。

技术研发人员:付永文,王耀亮

受保护的技术使用者:英彼森半导体(珠海)有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!