电压缓冲电路、参考电压产生装置、输入缓冲装置及系统的制作方法

本技术涉及集成电路,尤其涉及一种电压缓冲电路、参考电压产生装置、输入缓冲装置及系统。

背景技术:

1、电压缓冲电路是模数转换器(analog to digital converter,adc)中的重要组成模块。电压缓冲电路是将驱动能力弱和抗干扰性低的电压信号转换为驱动能力强和抗干扰性高的电压信号,供adc使用。电压缓冲电路一般包括电容和晶体管。而电压缓冲电路在增强电压信号的驱动能力时,不能引入过大的随机误差。因此,电压缓冲电路通常需要进行校准,来降低随机误差对电压缓冲电路的输出电压的影响。

2、目前,一种传统校准方法为自动校零(auto-zero)方法。该方法中,校准相位通过一个输入误差存储电容来储存输入误差。如此,在校准相位,输入误差存储电容上的存储电压可得到校准。在工作相位,电压缓冲电路的输出电压可得到校准,从而自动校准随机误差。

3、然而,电压缓冲电路中,晶体管的电荷注入通常会引入误差。在校准相位结束时,由于晶体管的关断,晶体管仍会向输入误差存储电容注入电荷,会改变输入误差存储电容上的存储电压,且在工作相位,也会改变电压缓冲电路的输出电压,从而引入较大的随机误差。如此,导致随机误差对电压缓冲电路的输出电压的影响增大,adc的系统精度降低。

技术实现思路

1、本技术提供一种电压缓冲电路、参考电压产生装置、输入缓冲装置及系统,能够减小晶体管的电荷注入引入的误差,使随机误差对电压缓冲电路的输出电压的影响减小。

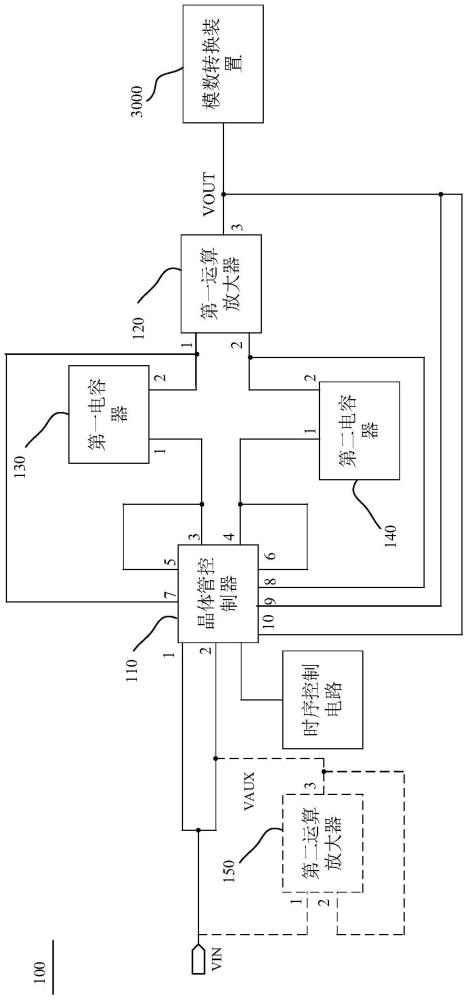

2、第一方面,本技术提供一种电压缓冲电路,该电压缓冲电路包括:晶体管控制器、第一电容器、第二电容器和第一运算放大器,第一电容器与第二电容器之间的容值差值在第一范围内;

3、晶体管控制器的第一端和晶体管控制器的第二端均用于接入输入电压,晶体管控制器的控制端与时序控制电路电连接,晶体管控制器的第三端与第一电容器的第一端电连接,第一电容器的第二端与第一运算放大器的正相输入端电连接,晶体管控制器的第四端与第二电容器的第一端电连接,第二电容器的第二端与第一运算放大器的负相输入端电连接,第一运算放大器的输出端与模数转换装置电连接,晶体管控制器的第五端电连接于晶体管控制器的第三端与第一电容器的第一端之间,晶体管控制器的第六端电连接于晶体管控制器的第四端与第二电容器的第一端之间,晶体管控制器的第七端电连接于第一电容器的第二端与第一运算放大器的正相输入端之间,晶体管控制器的第八端电连接于第二电容器的第二端与第一运算放大器的负相输入端之间,晶体管控制器的第九端和晶体管控制器的第十端均电连接于第一运算放大器的输出端与模数转换装置之间;

4、晶体管控制器,用于接收时序控制电路传输的时钟信号,并根据时钟信号,控制电压缓冲电路处于校准阶段或者工作阶段;

5、晶体管控制器,还用于在电压缓冲电路处于校准阶段时,将第一电容器上的存储电压变为0v,将第二电容器上的存储电压变为第一电压,第一电压是输出电压与输入电压之间的差值;

6、晶体管控制器,还用于在电压缓冲电路结束校准阶段时,分别向第一电容器和第二电容器注入相等的第一电荷,以将第一电容器上的存储电压变为第二电压,将第二电容器上的存储电压变为第一电压与第三电压的和值;

7、第一运算放大器,用于在电压缓冲电路处于工作阶段时,根据第二电压以及和值,对输出电压进行校准,以使输出电压的电压值在第二范围内,并向模数转换装置传输输出电压。

8、通过第一方面提供的电压缓冲电路,通过晶体管控制器可以接收时序控制电路传输的时钟信号,使晶体管控制器可以根据时钟信号,控制电压缓冲电路处于校准阶段或者工作阶段。如此,在电压缓冲电路处于校准阶段时,晶体管控制器向第一电容器注入第一电荷,使第一电容器上的存储电压变为第二电压,以及向第二电容器注入第一电荷,使第二电容器上的存储电压变为第一电压与第三电压的和值。由于第一电容器与第二电容器之间的容值差值在第一范围内,使第二电压和第三电压之间的电压差值在第一范围内。进而,在电压缓冲电路处于工作阶段时,第一运算放大器可以根据第二电压以及和值,对输出电压进行校准,使第二电压和第三电压之间的电压值差值可以减小在第一范围内。如此,能够减小因第一电荷而引入的误差。进而,减小晶体管的电荷注入引入的误差,使得输出电压的电压值在第二范围内。从而,第一运算放大器可以向模数转换装置传输输出电压,减小随机误差对电压缓冲电路的输出电压的影响。

9、在一种可能的设计中,该电压缓冲电路还包括:第二运算放大器;

10、第二运算放大器的正相输入端用于接入输入电压,第二运算放大器的输出端与晶体管控制器的第二端电连接,第二运算放大器的负向输入端电连接于第二运算放大器的输出端与晶体管控制器的第二端之间;

11、第二运算放大器,用于对输入电压进行等比例放大,得到放大的输入电压,放大的输入电压的幅值与输入电压的幅值相等,并向晶体管控制器传输放大的输入电压;

12、第二运算放大器,还用于在电压缓冲电路结束校准阶段时,存储晶体管控制器注入的第二电荷和晶体管控制器的时钟馈通。

13、在一种可能的设计中,晶体管控制器,具体用于根据第一时钟信号和第二时钟信号,控制电压缓冲电路处于校准阶段;

14、晶体管控制器,还具体用于根据第三时钟信号,控制电压缓冲电路处于工作阶段;

15、其中,时钟信号包括:第一时钟信号、第二时钟信号和第三时钟信号;第一时钟信号的上升沿和第二时钟信号的上升沿一致,第一时钟信号的下降沿在第二时钟信号的下降沿之后,第三时钟信号与第一时钟信号不同时为高电平,第三时钟信号与第二时钟信号不同时为高电平。

16、在一种可能的设计中,模数转换装置的工作时钟频率与第一时钟信号的频率的比值、模数转换装置的工作时钟频率与第二时钟信号的频率的比值以及模数转换装置的工作时钟频率与第三时钟信号的频率的比值均为1:n,n为大于或等于1的整数。

17、在一种可能的设计中,晶体管控制器包括:第一晶体管组件、第二晶体管组件、第三晶体管组件;

18、第一晶体管组件的控制端、第二晶体管组件的控制端和第三晶体管组件的控制端均与时序控制电路电连接,第一晶体管组件的第一端和第二晶体管组件的第一端和第三晶体管组件的第一端均用于接入输入电压,第一晶体管组件的第二端与第一电容器的第一端电连接,第一晶体管组件的第三端与第二电容器的第一端电连接,第二晶体管组件的第二端电连接于第一晶体管组件的第二端与第一电容器的第一端之间,第二晶体管组件的第三端电连接于第一晶体管组件的第三端与第二电容器的第一端之间,第三晶体管组件的第二端电连接于第一电容器的第二端与第一运算放大器的正相输入端之间,第三晶体管组件的第三端电连接于第二电容器的第二端与第一运算放大器的负相输入端之间,第一晶体管组件的第四端和第三晶体管组件的第四端均电连接于第一运算放大器的输出端与模数转换装置之间;

19、第一晶体管组件,用于接收时序控制电路传输的第三时钟信号;

20、第二晶体管组件,用于接收时序控制电路传输的第一时钟信号;

21、第三晶体管组件,用于接收时序控制电路传输的第二时钟信号。

22、在一种可能的设计中,第一晶体管组件包括:第一晶体管和第二晶体管;

23、第一晶体管的控制端和第二晶体管的控制端均与时序控制电路电连接,第一晶体管的第一端用于接入输入电压,第一晶体管的第二端与第一电容器的第一端电连接,第二晶体管的第一端电连接于第一运算放大器的输出端与模数转换装置之间,第二晶体管的第二端与第二电容器的第一端电连接。

24、在一种可能的设计中,第二晶体管组件包括:第三晶体管和第四晶体管;

25、第三晶体管的控制端和第四晶体管的控制端均与时序控制电路电连接,第三晶体管的第一端电连接于第一晶体管组件的第二端与第一电容器的第一端之间,第四晶体管的第一端电连接于第一晶体管组件的第三端与第二电容器的第一端之间,第三晶体管的第二端和第四晶体管的第二端均用于接入输入电压。

26、在一种可能的设计中,第三晶体管组件包括:第五晶体管和第六晶体管;

27、第五晶体管的控制端和第六晶体管的控制端均与时序控制电路电连接,第五晶体管的第一端电连接于第一电容器的第二端与第一运算放大器的正相输入端之间,第五晶体管的第二端用于接入输入电压,第六晶体管的第一端电连接于第二电容器的第二端与第一运算放大器的负相输入端之间,第六晶体管的第二端电连接于第一运算放大器的输出端与模数转换装置之间。

28、在一种可能的设计中,第一电容器的容值和第二电容器的容值相等。

29、在一种可能的设计中,第一电容器或者第二电容器包括:一个电容器,或者,多个串联和/或并联的电容器。

30、第二方面,本技术提供一种芯片,包括:上述第一方面及第一方面任一种可能的设计中的电压缓冲电路。

31、上述第二方面以及上述第二方面的各可能的设计中所提供的,其有益效果可以参见上述第一方面和第一方面的各可能的实施方式所带来的有益效果,在此不再赘述。

32、第三方面,本技术提供一种参考电压产生装置,包括:带隙基准电路、第一时序控制电路以及上述第一方面及第一方面任一种可能的设计中的电压缓冲电路,带隙基准电路与晶体管控制器的第一端和晶体管控制器的第二端均电连接;

33、带隙基准电路,用于向晶体管控制器传输输入电压。

34、第四方面,本技术提供一种输入缓冲装置,包括:运算放大电路、第二时序控制电路以及上述第一方面及第一方面任一种可能的设计中的电压缓冲电路,运算放大电路与晶体管控制器的第一端和晶体管控制器的第二端均电连接;

35、运算放大电路,用于向晶体管控制器传输输入电压。

36、第五方面,本技术提供一种模数转换系统,包括:模数转换装置、输入缓冲装置和上述第三方面中的参考电压产生装置;

37、或者,模数转换装置、参考电压产生装置和上述第四方面中的输入缓冲装置;

38、或者,模数转换装置、上述第三方面中的参考电压产生装置和上述第四方面中的输入缓冲装置。

39、第六方面,本技术提供一种模数转换系统,包括:模数转换装置、参考电压产生装置和输入缓冲装置;

40、参考电压产生装置包括:带隙基准电路、第一时序控制电路以及上述第一方面及第一方面任一种可能的设计中的电压缓冲电路,带隙基准电路与晶体管控制器的第一端和晶体管控制器的第二端均电连接;

41、输入缓冲装置包括:运算放大电路、第二时序控制电路以及上述第一方面及第一方面任一种可能的设计中的电压缓冲电路,运算放大电路与晶体管控制器的第一端和晶体管控制器的第二端均电连接;

42、带隙基准电路,用于向晶体管控制器传输输入电压;

43、运算放大电路,用于向晶体管控制器传输输入电压。

44、在一种可能的设计中,模数转换系统还包括:第三运算放大器、第一电阻和第二电阻;

45、第三运算放大器的正相输入端电连接于带隙基准电路与晶体管控制器的第一端之间,第三运算放大器的输出端与晶体管控制器的第二端电连接,第一电阻的第一端电连接于第三运算放大器的输出端与晶体管控制器的第二端之间,第三运算放大器的负相输入端电连接于第一电阻的第一端和第三运算放大器的输出端之间,第一电阻的第二端与第二电阻的第一端电连接,第二电阻的第二端接地,晶体管控制器的第二端电连接于第一电阻的第二端与第二电阻的第一端之间;

46、第三运算放大器,用于对输入电压进行等比例放大,得到放大的输入电压,放大的输入电压的幅值与输入电压的幅值相等,并向晶体管控制器传输放大的输入电压;

47、第三运算放大器,还用于在电压缓冲电路结束校准阶段时,存储晶体管控制器注入的第三电荷和晶体管控制器的时钟馈通。

- 还没有人留言评论。精彩留言会获得点赞!