一种触发器电路和芯片的制作方法

本公开的实施例涉及集成电路,具体地,涉及一种触发器电路和芯片。

背景技术:

1、施密特触发器是一种将输入电压与参考电压进行比较,并基于比较生成数字逻辑电平输出的电路,它们通常用于逻辑电路、信号处理和开关。对于传统施密特触发器,当输入电压高于阈值电压vih时,输出为高电平信号;当输入电压低于阈值电压vil时,输出为低电平信号。施密特触发器可作为波形整形电路,能够将模拟信号波形整形为数字电路能够处理的方波波形,而且由于施密特触发器具有迟滞特性,可用于抗干扰。

2、传统的施密特触发器电路输入信号通常都小于5.5v,以兼容互补金属氧化物半导体场效应晶体管(complementary metal oxide semiconductor field effecttransistor,cmos)逻辑电平和晶体管-晶体管逻辑集成电路(transistor-transistorlogic,ttl)逻辑电平。但在高压产品中,逻辑输入管脚可能接到电源电压vcc上,例如vcc=40v。输入信号此时也是高压,然而传统的施密特触发器电路不能承受高压,可能导致芯片损坏。

技术实现思路

1、本文中描述的实施例提供了一种触发器电路和芯片,不仅能够实现高压施密特触发器的功能,而且无需输入偏置电流。

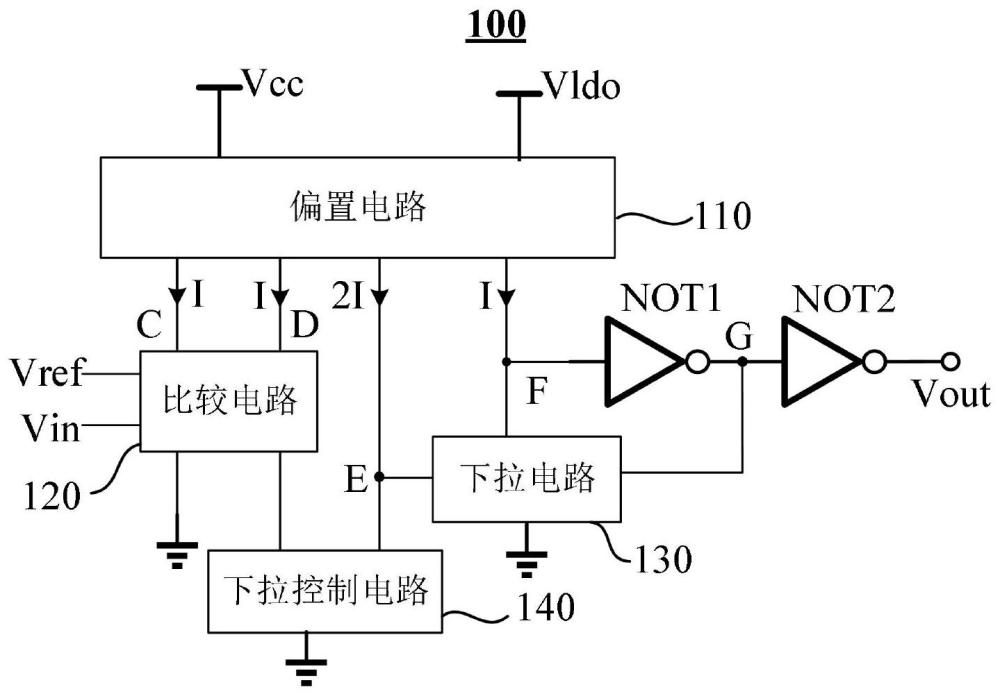

2、第一方面,本公开提供了一种触发器电路,包括:偏置电路、比较电路、下拉电路、下拉控制电路、第一反相器和第二反相器;所述比较电路的第一控制端电连接所述触发器电路的输入端,所述触发器电路的输入端提供的输入电压的范围为0v至预设电压,所述比较电路的第二控制端电连接参考电压。

3、所述偏置电路被配置为,向所述下拉电路、所述下拉控制电路和所述比较电路提供偏置电流。所述比较电路被配置为,比较所述输入电压和所述参考电压并输出比较电流信号。所述下拉控制电路被配置为,基于所述比较电流信号控制所述下拉电路。所述下拉电路被配置为,在所述输入电压小于所述参考电压与第一电压阈值之差时,拉低所述第一反相器的输入端电压以输出低电平。所述偏置电路还被配置为,在所述输入电压大于所述参考电压与第二电压阈值之和时,拉高所述第一反相器的输入端电压以输出高电平。

4、在本公开的一些实施例中,所述比较电路包括:第一晶体管、第二晶体管和第三晶体管。

5、所述第一晶体管的第一端和所述第三晶体管的第一端电连接所述偏置电路的第一输出端,所述第一晶体管的控制端和所述第三晶体管的控制端电连接所述触发器电路的输入端,所述第一晶体管的第二端接地,所述第三晶体管的第二端和所述第二晶体管的第一端电连接所述偏置电路的第二输出端,所述第二晶体管的第二端电连接所述下拉控制电路的第一输入端,所述第二晶体管的控制端电连接所述参考电压。

6、在本公开的一些实施例中,所述偏置电路包括:第四晶体管、第五晶体管、第六晶体管、第七晶体管、第八晶体管、第九晶体管、第十晶体管、第十一晶体管、第十二晶体管和第十三晶体管。

7、所述第四晶体管的第一端、所述第五晶体管的第一端、所述第六晶体管的第一端和所述第七晶体管的第一端电连接电源电压,所述第八晶体管的第一端和所述第九晶体管的第一端接地,所述第十晶体管的第一端、所述第十一晶体管的第一端、所述第十二晶体管的第一端和所述第十三晶体管的第一端电连接内部电压。

8、所述第四晶体管的第二端电连接所述比较电路的第一输入端,所述第五晶体管的第二端电连接所述比较电路的第二输入端,所述第六晶体管的第二端、所述第十二晶体管的第二端和所述下拉控制电路的第二输入端电连接所述下拉电路的控制端,所述第七晶体管的第二端、所述第七晶体管的控制端、所述第四晶体管的控制端、所述第五晶体管的控制端和所述第六晶体管的控制端电连接所述第八晶体管的第二端。

9、所述第八晶体管的控制端、所述第九晶体管的控制端和所述第九晶体管的第二端电连接所述第十一晶体管的第二端,所述第十晶体管的控制端、所述第十晶体管的第二端、所述第十一晶体管的控制端和所述第十二晶体管的控制端电连接所述第十三晶体管的控制端,所述第十三晶体管的第二端和所述下拉电路的输出端电连接所述第一反相器的输入端。

10、在本公开的一些实施例中,所述下拉电路包括:第十四晶体管、第十五晶体管、第十六晶体管和第十七晶体管。

11、所述第十四晶体管的第一端、所述第十五晶体管的第一端和所述第十七晶体管的第一端接地,所述第十四晶体管的第二端、所述第十四晶体管的控制端、所述第十五晶体管的控制端、所述第十七晶体管的控制端和所述下拉控制电路的第二输入端电连接所述偏置电路的第三输出端,所述第十五晶体管的第二端电连接所述第十六晶体管的第一端,所述第十六晶体管的第二端、所述第十七晶体管的第二端和所述偏置电路的第四输出端电连接所述第一反相器的输入端,所述第十六晶体管的控制端和所述第一反相器的输出端电连接所述第二反相器的输入端。

12、在本公开的一些实施例中,所述下拉控制电路包括:第十八晶体管和第十九晶体管。

13、所述第十八晶体管的第一端和所述第十九晶体管的第一端接地,所述第十八晶体管的第二端、所述第十八晶体管的控制端和所述第十九晶体管的控制端电连接所述比较电路的输出端,所述第十九晶体管的第二端和所述偏置电路的第三输出端电连接所述下拉电路的控制端。

14、在本公开的一些实施例中,所述偏置电路还包括钳位晶体管,其中,所述钳位晶体管的第一端电连接所述第八晶体管的第二端,所述钳位晶体管的第二端电连接所述第七晶体管的第二端。

15、所述钳位晶体管被配置为,将所述第八晶体管的第二端的电压限制为小于或等于钳位电压。

16、在本公开的一些实施例中,所述第一晶体管、所述第二晶体管、所述第三晶体管、所述第四晶体管、所述第五晶体管、所述第六晶体管和所述第七晶体管为p型横向扩散金属氧化物半导体场效应管pldmos。

17、在本公开的一些实施例中,所述钳位晶体管为nldmos。

18、在本公开的一些实施例中,所述第三晶体管的宽长比为所述第二晶体管的宽长比的k倍,其中,k为大于1的正整数。

19、所述第十五晶体管的宽长比为所述第十四晶体管的宽长比的m倍,其中,m为大于1的正整数,且m<k。

20、第二方面,本公开提供了一种芯片,包括第一方面提供的任一触发器电路。

21、本公开提供了一种触发器电路,包括偏置电路、比较电路、下拉电路、下拉控制电路、第一反相器和第二反相器,通过偏置电路能够向下拉电路、下拉控制电路和比较电路提供偏置电流,通过比较电路能够比较输入电压和参考电压并输出比较电流信号且输入电压的范围为0v至预设电压,也就是说,比较电路可以将输入高压信号转换成低压电流信号,实现输入高压信号的逻辑控制,通过下拉控制电路能够基于比较电流信号控制下拉电路,使得下拉电路能够在输入电压小于参考电压与第一电压阈值之差时,拉低第一反相器的输入端电压以输出低电平,通过偏置电路能够在输入电压大于参考电压与第二电压阈值之和时,拉高第一反相器的输入端电压以输出高电平。如此,触发器电路采用高压比较电路实现高压施密特触发器的功能。

22、另外,由于触发器电路的输入端与比较电路的控制端电连接,触发器电路的输入端可以提供比较电路的控制电压,且触发器电路可以在内部生成偏置电流,因此触发器电路的输入端无需提供偏置电流,即触发器电路无需输入偏置电流。

- 还没有人留言评论。精彩留言会获得点赞!