一种自校准和频率可选择双延迟线锁相环电路

本发明涉及集成电路,特别涉及一种自校准和频率可选择双延迟线锁相环电路的设计方法。

背景技术:

1、近年来,随着我国信息化技术的深入,主流的电子产品加速向高频推进,市场迫切需要更高速率、更高精度的高速模/数转换系统,以满足不断提高的系统速度和实时采样要求。高速模/数转换器是一个时控系统,其必须严格按时间序列进行信号采样和模数转换,因而对高稳定时钟的要求特别高。

2、时钟电路的设计方法有很多种,例如振荡器、直接频率合成器、锁相技术等技术。锁相技术因其内部负反馈环路的结构优势,目前已成为芯片系统中最常用的一种时钟产生技术。锁相技术中最常用的结构就是锁相环(phase-locked loop,pll),它是一种反馈系统,其中电压控制振荡器和相位比较器相互连接,使得振荡器频率(相位)可以准确跟踪施加的频率或相位调制信号的频率。但早期pll采用压控振荡器(voltage-controlledoscillator,vco)结构,此结构中振荡器的工作状态或振荡回路的元件参数受输入控制电压的控制,输出频率是输入控制电压的线性函数,故vco的传输函数包含一个极点,使噪声不断积累。随着集成电路技术的发展,学术界和工业界迫切需要新的锁相技术或者结构,因此延迟锁相环(delay locked loop,dll)技术越来越受到重视并得以发展。延迟锁相环是在pll技术上改进得到的,被广泛应用于时序领域中。它继承了pll电路的锁相技术,但去掉了pll电路内的振荡器部分,取而代之的是一条延迟量受电压控制的延迟线,即压控延迟线(voltage controlled delay line,vcdl)。压控延迟线由多个延迟单元串接而成,每个延迟单元的延迟量都受电压控制,即延迟控制电压。与pll相比,dll因其更好的环路稳定性、较低功耗、更简单的电路结构、更短的锁定时间、较低的相位噪声等优点,更受业界青睐。

3、目前,dll现在已经广泛应用于高速存储总线接口、时钟数据恢复电路,时钟合成器等各类电路。各类时钟的需求也加速了dll电路的发展,同时也对现有的dll性能提出新的挑战。为了满足需求,工业界和学业界都在向更低抖动、更宽工作频率范围等方向努力。

技术实现思路

1、针对现有技术中存在的问题,本发明的目的是提供一种自校准和频率可选择双延迟线锁相环电路,其能改善上述问题。

2、为实现上述技术目的,本发明采用的技术方案是:一种自校准和频率可选择双延迟线锁相环电路,该电路存在双延迟线结构,可以根据输入时钟所处频率范围自动选择延迟线,故电路整体工作频率包括了两个延迟线工作频率范围,此外,在dll环路结构以外增加延迟校准电路,以使延迟线各级输出之间延迟量一致。

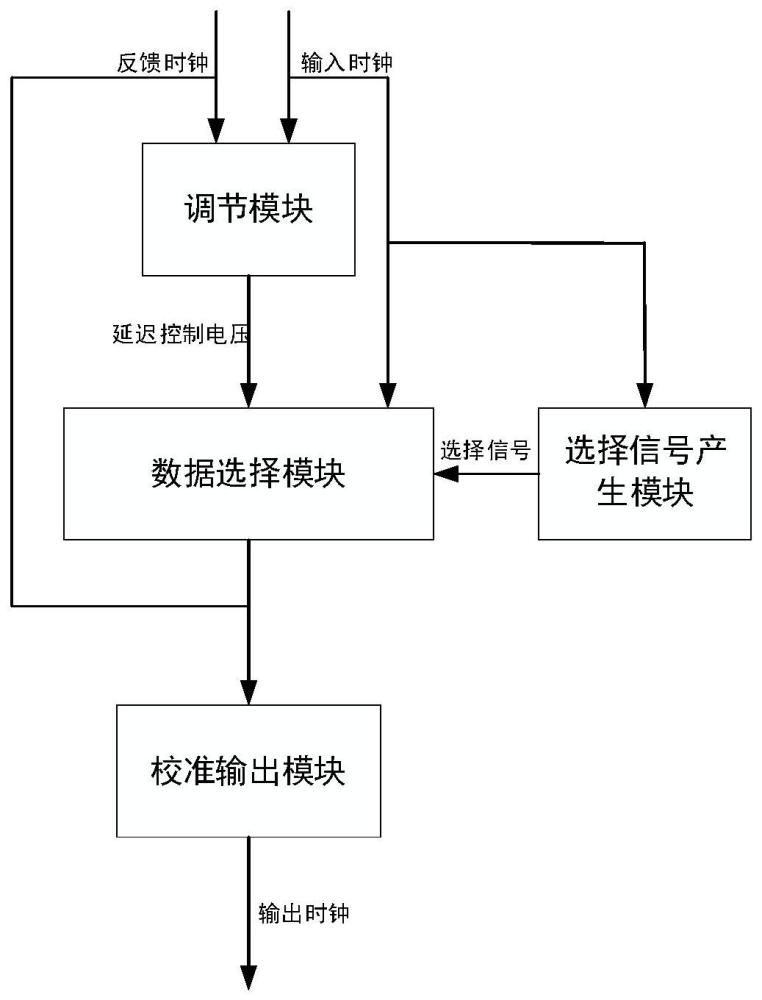

3、所述锁相环电路包括调节模块、选择信号产生模块、数据选择模块以及校准输出模块,其中:

4、s1、所述调节模块输入端连接输入时钟和反馈时钟,输出为延迟控制电压,用于调控延迟线的延迟量,缩小输入时钟与反馈时钟之间的相位差;所述选择信号产生模块输入端连接输入时钟,输出为选择信号,其值为高电平或者低电平;所述数据选择模块的输入端为输入时钟、选择信号以及延迟控制电压,根据选择信号选择某条延迟线作为输出,一方面继续输入到延迟校准模块,另一方面反馈回调节模块作为反馈时钟;所述延迟校准模块用于校准延迟线的延迟量,得到最终的输出时钟信号;

5、s2、进一步地,所述调节模块中主要包括启动控制电路(start-controlledcircuits,scc)、鉴相器(phase detector,pd)、电荷泵(charge pump,cp)以及环路滤波(loop filter,lf),其中:

6、s201、scc根据输入时钟与反馈时钟之间的相位,控制电路启动时间,并调整两时钟对齐边沿,防止错误锁定(与第一个上升沿对齐)和谐波锁定(与第三个及以上的上升沿对齐),输入时钟和反馈时钟经过scc输入到pd中;

7、s202、pd根据输入时钟和反馈时钟之间的相位差,产生不同脉冲宽度的信号;

8、s202、cp将鉴相器输出端的脉冲信号宽度转换为对环路滤波电容的充放电操作,并产生一个延迟控制电压;

9、s203、lf通常由一个电容构成。

10、s3、再进一步地,所述选择信号产生模块主要包括频率测量电路(frequency testcircuits,ftc)和比较器(comparator,com),其中:

11、s301、ftc模块用于测量输入时钟的频率,并将测量出的频率值与一个已知的参考频率值共同输入到比较器中;

12、s302、com模块得到频率测量值,并与频率参考值比较大小,若频率测量值低于频率参考值则输出(即选择信号)低电平,反之则输出高电平。

13、s4、再进一步地,所述数据选择模块包括两条压控延迟线(voltage controlleddelay line,vcdl)和一个数据选择组,其中:

14、s401、vcdl由多个相同的延迟单元串接而成,每个延迟单元延迟量都受到电压控制(即延迟控制电压),并且在每个延迟单元输出端都可以得到一个时钟信号,多个延迟单元输出的时钟信号组成延迟量均匀的多相时钟信号;

15、s402、数据选择组由多个数据选择器(data selector,ds)并联组成,ds有两个输入端、一个输出端以及一个选择端,即为“二选一”数据选择器;

16、s403、输入时钟首先进入两个压控延迟线(vcdl1和vcdl2)中,在经过延迟之后,得到的多相时钟信号输入到数据选择组中,再根据选择信号(高/低电平)选择vcdl1和vcdl2其中一条延迟线并输出多相时钟信号;

17、s404、所述延迟线将输入时钟延迟一个周期的时间。

18、s5、再进一步地,所述延迟校准模块主要包括锁定检测电路(lock detectorcircuits,ldc)、时序误差比较电路(timing error comparator,tec)以及延迟校准缓冲器(delay calibration buffer,dcb),其中:

19、s501、ldc根据输入时钟与延迟线最后一级时钟的相位差,判断电路是否锁定,并输出校准使能信号,使时序误差比较电路开始工作;

20、s502、tec接收来自延迟校准缓冲器的三个连续时钟信号,并比较三者之间时序的差异性,输出校准电压信号;

21、s503、dcb由多个延迟单元串联连接,此延迟单元与压控延迟中的延迟单元结构相同但参数不同,由tec得到的校准电压信号输入到延迟控制电压端口,以调整中间时钟与前后时钟的延迟时间,使得前后延迟时间一致;

22、s6、再进一步地,所述数据选择组中每个ds单元输入端为两个延迟线所对应相位的时钟信号;所述选择信号为二进制信号:高电平或者低电平,其中:

23、当选择信号为低电平,所述数据选择组选择处于较低频率范围延迟线;

24、当选择信号为高电平,所述数据选择组选择处于较高频率范围延迟线。

25、s7、再进一步地,vcdl1和vcdl2的延迟单元不同,分别代表不同的工作频率范围,但是vcdl1和vcdl2各自包括多个相同的延迟单元,多个延迟单元之间串联连接;

26、所述延迟单元的压控增益(延迟时间是控制电压的函数,其导数为压控增益)极性皆为正,即控制电压增加,延迟时间增加。

27、s8、再进一步地,vcdl1和vcdl2在第一级和最后一级延迟单元加了的dummy单元,dummy单元是版图设计时加入的一种虚拟器件,其结构和设计参数都与延迟单元一致,以提高压控延迟线版图设计的匹配性,进而降低延迟失配(延迟单元之间的延迟量不一致称为延迟失配)。

28、现有的技术由于延迟线的限制导致工作频率范围较小,超出dll的工作频率后将导致电路无法正常工作,与现有技术相比,本发明的技术方案具有以下有益的技术效果:本发明中有两个压控延迟线可供选择,电路可以比较输入时钟频率值与一个已知的参考频率值,根据输出(选择信号)选择对应的压控延迟线并输出多相时钟信号,整个电路的工作频率范围得以提高。并在环路结构以外增加延迟校准电路,在减小输出时钟延迟失配(即延迟线各级输出之间延迟量不一致)同时又不会影响dll环路内部电路。

- 还没有人留言评论。精彩留言会获得点赞!