一种优化高速信号等长的封装结构的制作方法

本技术涉及pcb,尤其涉及一种优化高速信号等长的封装结构。

背景技术:

1、印刷电路板英文名称printed circuit board,简称pcb板,由于其采用电子印刷术制作形成,故被称为“印刷”电路板,是电子元器件的支撑体、电气连接的载体,是一种重要的电子部件。pcb封装就是把实际的电子元器件,芯片等的各种参数(比如元器件的大小,长宽,直插,贴片,焊盘的大小,管脚的长宽,管脚的间距等)用图形方式表现出来,以便可以在画pcb图时进行调用,是pcb板制造中重要的一个环节。

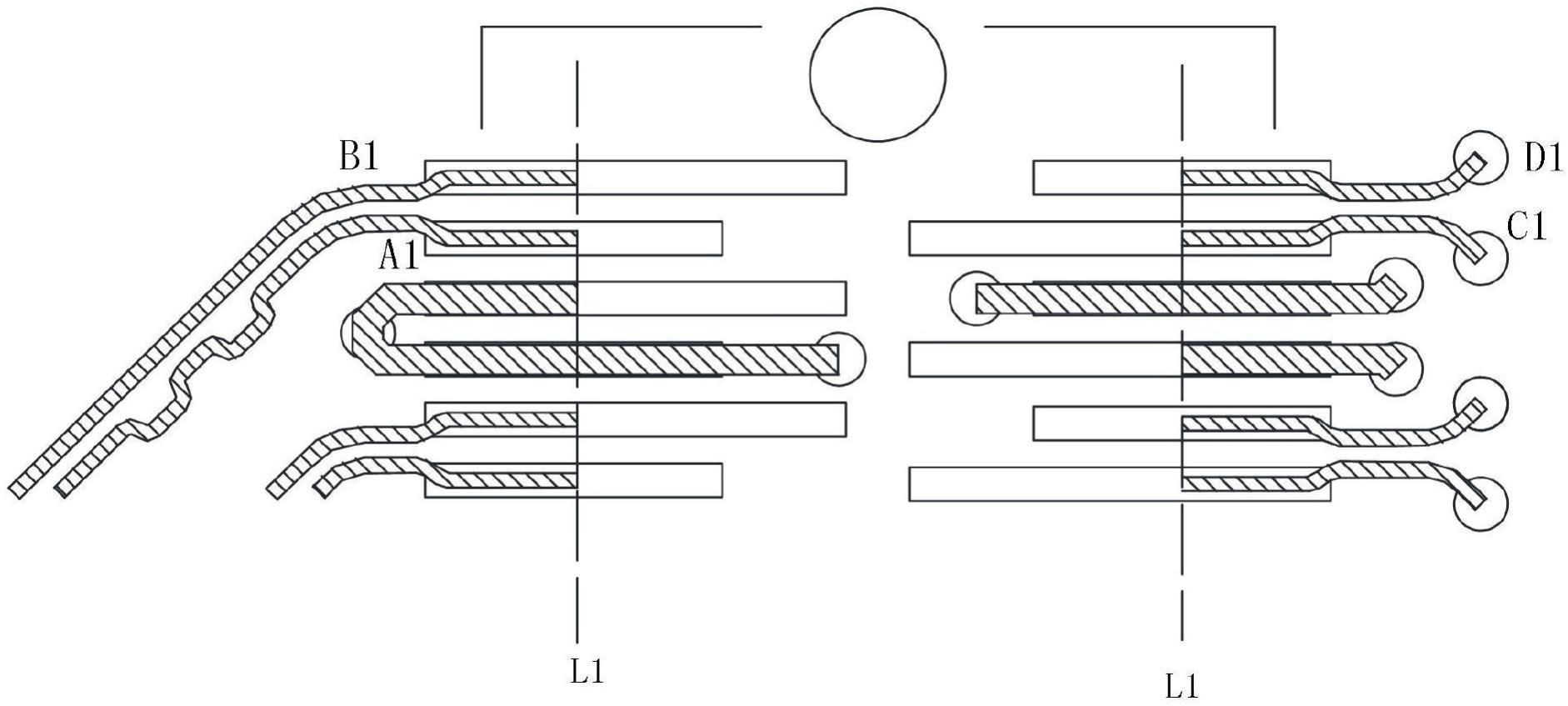

2、在pcb板的应用中,常常需要连接两块电路板,使其之间实现信号连接。一般两块电路板之间为实现互连通信必须要有高速信号通过,板与板之间通信连接元件为互扣连接的座子,即多pin脚排列的连接器,如具有四排pin脚排列的连接器,在封装时就会出现如图1所示的双排长短pin封装来实现与实物座子匹配。在这里不能将短pin改成长pin,若将短pin改为长pin,实物座子靠近外边的管脚实际连接时除了有效长度还会产生在一段stub的情况,该段stub即是由短pin增长的部分形成。

3、图1中各个pin的中心点一般在各自的中心位置上,这样在实际pcb设计布线时会出现如图2所示的情况,从而使得长pin出线会比短pin出线长,基于allegro设计软件上识别的等长是指板上实际板上pin中心点对pin中心点的实际走线长度,常规封装会造成信号线不等长,产生时序差异,然而由于高速信号速率很高,对于时序的要求比较严格,信号等长误差较小越好,一般的封装方式用于高速信号连接器的封装对信号的影响较大。

4、上述缺陷,值得改进。

技术实现思路

1、为了克服现有的技术的不足,本实用新型提供一种优化高速信号等长的封装结构。

2、本实用新型技术方案如下所述:

3、一种优化高速信号等长的封装结构,所述优化高速信号等长的封装结构应用于高速信号连接器与电路板的连接,所述电路板上包括有长pin和短pin的封装,所述长pin和所述短pin连接高速信号线,所述长pin出线位置与所述短pin出线位置对齐,长pin和短pin上出线长度相同。

4、进一步地,在一实施例中,所述短pin的出线位置处于短pin中心位置上,长pin出线位置处于短pin中心点连线与长pin相交处。

5、进一步地,在一实施例中,短pin长度大于长pin长度的一半,所述长pin的出线位置处于长pin中心位置上,短pin出线位置处于长pin中心点连线与短pin相交处。

6、进一步地,在一实施例中,所述长pin出线位置、所述短pin出线位置位于各自pin脚上长pin中心位置所在直线与短pin中心位置所在直线之间的位置上。

7、进一步地,在一实施例中,同侧的长pin和短pin的外侧边对齐。

8、进一步地,在一实施例中,所述短pin连接的高速信号线具有凸起。

9、进一步地,在一实施例中,所述凸起靠近所述高速信号线弯折处。

10、进一步地,在一实施例中,同侧的长pin和短pin交替排列。

11、进一步地,在一实施例中,每排长pin的相对侧面位置上对应设置一个短pin,每排短pin的相对侧面位置上对应设置一个长pin。

12、进一步地,在一实施例中,所述高速信号线还包括过孔连接。

13、根据上述方案的本实用新型,其有益效果在于,在电路板与高速信号器连接时,电路板上出线有长pin脚和短pin脚两种长度不同的pin脚连接,本实用新型通过在进行长、短pin封装时,改变pin中心点位置,形成长pin出线位置和短pin出线位置对齐的封装结构,以使长pin出线和短pin出线长度相同。通过对齐pin中心点建库,使后续pcb布线时,长pin出线点、短pin出线点对齐以使信号出线长度一致,从而保证高速信号的信号线等长,解决了高速信号板间传递的延时问题,降低了封装用于高速信号连接器时对高速信号的影响。

技术特征:

1.一种优化高速信号等长的封装结构,其特征在于,所述优化高速信号等长的封装结构应用于高速信号连接器与电路板的连接,所述电路板上包括有长pin和短pin的封装,所述长pin和所述短pin连接高速信号线,所述长pin出线位置与所述短pin出线位置对齐,长pin和短pin上出线长度相同。

2.根据权利要求1所述的优化高速信号等长的封装结构,其特征在于,所述短pin的出线位置处于短pin中心位置上,长pin出线位置处于短pin中心点连线与长pin相交处。

3.根据权利要求1所述的优化高速信号等长的封装结构,其特征在于,短pin长度大于长pin长度的一半,所述长pin的出线位置处于长pin中心位置上,短pin出线位置处于长pin中心点连线与短pin相交处。

4.根据权利要求1所述的优化高速信号等长的封装结构,其特征在于,所述长pin出线位置、所述短pin出线位置位于各自pin脚上长pin中心点连线与短pin中心点连线之间的位置上。

5.根据权利要求1-4任一所述的优化高速信号等长的封装结构,其特征在于,同侧的长pin和短pin的外侧边对齐。

6.根据权利要求5所述的优化高速信号等长的封装结构,其特征在于,所述短pin连接的高速信号线具有凸起。

7.根据权利要求6所述的优化高速信号等长的封装结构,其特征在于,所述凸起靠近所述高速信号线弯折处。

8.根据权利要求7所述的优化高速信号等长的封装结构,其特征在于,同侧的长pin和短pin交替排列。

9.根据权利要求8所述的优化高速信号等长的封装结构,其特征在于,每排长pin的相对侧面位置上对应设置一个短pin,每排短pin的相对侧面位置上对应设置一个长pin。

10.根据权利要求9所述的优化高速信号等长的封装结构,其特征在于,所述高速信号线还包括过孔连接。

技术总结

本技术公开了一种优化高速信号等长的封装结构,所述优化高速信号等长的封装结构应用于高速信号连接器与电路板的连接,所述电路板上包括有长pin和短pin的封装,所述长pin和所述短pin连接高速信号线,所述长pin出线位置与所述短pin出线位置对齐,长pin和短pin上出线长度相同。本技术通过对齐pin的连接点建库,使后续pcb布线时,长短pin中心点对齐以使信号出线一致,从而保证高速信号的信号线等长,更好的保证延时问题。本技术对pin中心点变动不会改变高速信号连接器发挥连接作用的具体实体结构,本申请简单易行,在PCB封装上具有广泛的应用,具有良好的适用性。

技术研发人员:马洪伟,王灿钟

受保护的技术使用者:深圳市一博科技股份有限公司

技术研发日:20230330

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!