一种3D堆栈崁入式电子器件封装结构的制作方法

本技术涉及一种3d堆栈崁入式电子器件封装结构,属于半导体。

背景技术:

1、半导体行业经历了快速增长。在大多数情况下,电子元件性能的提升来自最小特征尺寸的重复减小,这允许将更多元件集成到给定区域。随着近来对更小电子元件的需求不断增长,对更小、更具创意的半导体管芯封装技术的需求也在增长。

2、然而,对于离散的无源器件,传统器件的尺寸非常大,不利于未来高性能芯片的发展。

技术实现思路

1、本实用新型所要解决的技术问题是针对现有技术中存在上述缺陷,提供一种3d(三维)堆栈崁入式电子器件封装结构将无源器件集成在诸如晶圆的硅基材中,缩小了器件尺寸。

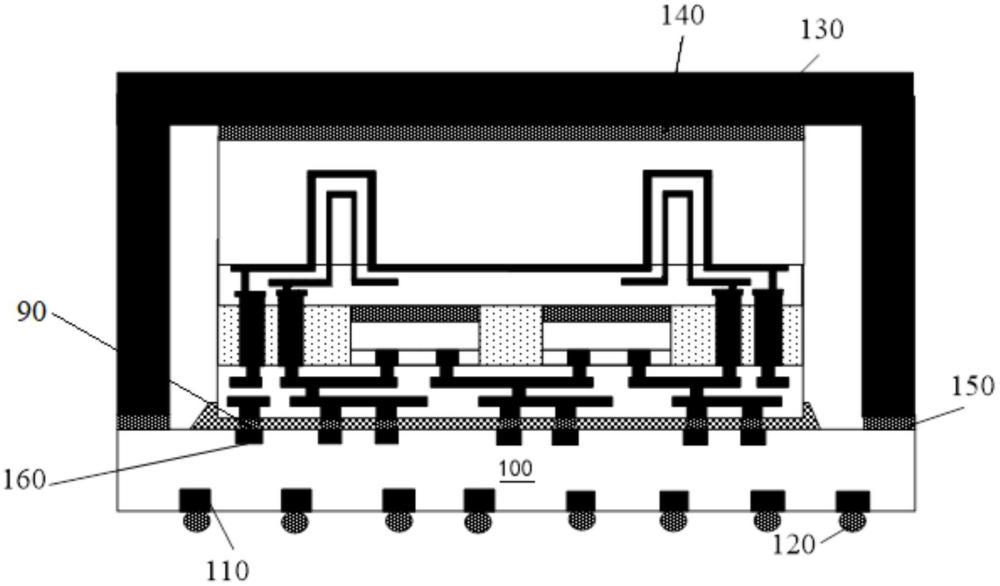

2、根据本实用新型,提供了一种3d堆栈崁入式电子器件封装结构,包括:布置在硅基材中的无源电容结构;布置在硅基材上的硅基材介质层;以及通过粘合层布置在硅基材上的硅基材介质层上的芯片,其中芯片上布置有形成电连接端口的介质层。

3、优选地,所述3d堆栈崁入式电子器件封装结构还包括:布置在硅基材上的硅基材介质层中的无源电感结构。

4、优选地,所述3d堆栈崁入式电子器件封装结构还包括:金属柱,其中无源电容结构经由硅基材介质层中布线与电连接金属柱,金属柱与芯片及其上的介质层处于同一层。

5、优选地,所述3d堆栈崁入式电子器件封装结构还包括:覆盖芯片和金属柱的封装材料、布置在芯片所在层上的上部介质层、经由上部介质层中的布线连接至金属柱和电连接端口的焊球。

6、优选地,所述3d堆栈崁入式电子器件封装结构还包括:封装基板,其中封装基板上表面形成有上部电焊盘,封装基板下表面形成有与上部电焊盘电连接的下部电焊盘,下部电焊盘上连接有外部焊球。

7、优选地,焊球焊接至上部电焊盘以便将芯片固定至封装基板。

8、优选地,所述3d堆栈崁入式电子器件封装结构还包括:通过粘合剂覆盖在封装基板上的散热盖。

9、优选地,散热盖与硅基材之间布置有粘合材料层。

10、优选地,硅基材与散热盖之间还设置有封装件,散热盖与封装件之间布置有粘合材料层。

11、优选地,硅基材于相应位置开设开孔,开孔露出硅基材中的布线结构,开孔通过导电焊锡设置封装件。

12、本实用新型将无源器件集成在诸如晶圆的硅基材中,缩小了器件尺寸。与传统的多层陶瓷电容相比,基于硅晶圆制备硅电容器可以减小电容器的体积、增大容值密度。传统制程的玻璃载板价格昂贵,制程报废率不易重复使用,基于硅晶圆制备电容器直接变成载板,具备制备低成本、小体积优点。

技术特征:

1.一种3d堆栈崁入式电子器件封装结构,其特征在于包括:

2.根据权利要求1所述的一种3d堆栈崁入式电子器件封装结构,其特征在于还包括:布置在硅基材上的硅基材介质层中的无源电感结构。

3.根据权利要求1或2所述的一种3d堆栈崁入式电子器件封装结构,其特征在于还包括:金属柱,其中无源电容结构经由硅基材介质层中布线与电连接金属柱,金属柱与芯片及其上的介质层处于同一层。

4.根据权利要求3所述的一种3d堆栈崁入式电子器件封装结构,其特征在于还包括:覆盖芯片和金属柱的封装材料、布置在芯片所在层上的上部介质层、经由上部介质层中的布线连接至金属柱和电连接端口的焊球。

5.根据权利要求4所述的一种3d堆栈崁入式电子器件封装结构,其特征在于还包括:封装基板,其中封装基板上表面形成有上部电焊盘,封装基板下表面形成有与上部电焊盘电连接的下部电焊盘,下部电焊盘上连接有外部焊球。

6.根据权利要求5所述的一种3d堆栈崁入式电子器件封装结构,其特征在于,焊球焊接至上部电焊盘以便将芯片固定至封装基板。

7.根据权利要求5所述的一种3d堆栈崁入式电子器件封装结构,其特征在于还包括:通过粘合剂覆盖在封装基板上的散热盖。

8.根据权利要求7所述的一种3d堆栈崁入式电子器件封装结构,其特征在于,散热盖与硅基材之间布置有粘合材料层。

9.根据权利要求7所述的一种3d堆栈崁入式电子器件封装结构,其特征在于,硅基材与散热盖之间还设置有封装件,散热盖与封装件之间布置有粘合材料层。

10.根据权利要求9所述的一种3d堆栈崁入式电子器件封装结构,其特征在于,硅基材于相应位置开设开孔,开孔露出硅基材中的布线结构,开孔通过导电焊锡设置封装件。

技术总结

本技术提供了一种3D堆栈崁入式电子器件封装结构,包括:布置在硅基材中的无源电容结构;布置在硅基材上的硅基材介质层;以及通过粘合层布置在硅基材上的硅基材介质层上的芯片,其中芯片上布置有形成电连接端口的介质层。本技术将无源器件集成在诸如晶圆的硅基材中,缩小了器件尺寸。与传统的多层陶瓷电容相比,基于硅晶圆制备硅电容器可以减小电容器的体积、增大容值密度。

技术研发人员:陈彦亨,林正忠

受保护的技术使用者:盛合晶微半导体(江阴)有限公司

技术研发日:20230808

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!