字线拾取结构和用于形成字线拾取结构的方法与流程

背景技术:

1、本公开一般涉及集成电路,并且更具体地,涉及导电线的形状和布置。

2、半导体制造技术的各种进步已经提供了用于产生越来越小的特征尺寸以及这些特征之间的越来越小的间距的能力。然而,这些更小的特征和间距继续带来制造挑战和成品率问题。

技术实现思路

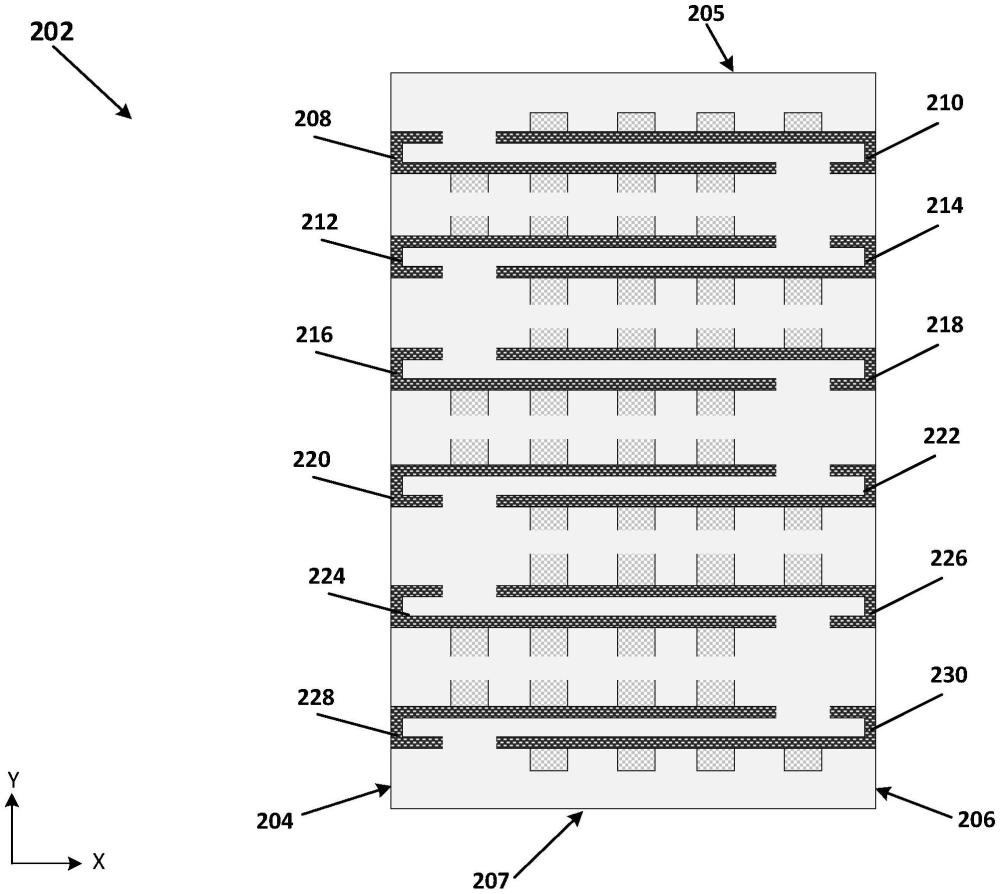

1、根据本公开的一个方面,一种存储器装置,包括:多个第一字线,其中,每个第一字线具有第一部分、第二部分和第三部分;多个第二字线,其中,每个第二字线具有第一部分、第二部分和第三部分;以及存储阵列,其具有第一侧、与第一侧横向相对的第二侧、以及第三侧;其中,每个第一字线的第一部分与其第三部分间隔开,并且每个第二字线的第一部分与其第三部分间隔开,每个第一字线的第二部分与其第一部分以及其第三部分不平行且不共线,并且每个第二字线的第二部分与其第一部分以及其第三部分不平行且不共线,每个第一字线设置成使得其第二部分与第一侧相邻,并且每个第二字线设置成使得其第二部分与第二侧相邻,每个第一字线的第一部分具有第一长度,每个第一字线的第二部分具有第二长度,并且每个第一字线的第三部分具有第三长度,每个第二字线的第一部分具有第四长度,每个第二字线的第二部分具有第五长度,并且每个第二字线的第三部分具有第六长度,第一长度大于第三长度,并且第四长度大于第六长度。

2、在一些实施方式中,每个第一字线的第二部分设置在第一侧的第一预先确定的距离和第二侧的第二预先确定的距离内,第一预先确定的距离小于第二预先确定的距离,每个第二字线的第二部分设置在第二侧的第三预先确定的距离和第一侧的第四预先确定的距离内,第三预先确定的距离小于第四预先确定的距离,第一第一字线的第三部分与第三侧相距第一距离,并且第一第二字线的第一部分与第三侧相距第一距离,第二第一字线的第三部分与第三侧相距第二距离,并且第二第二字线的第一部分与第三侧相距第二距离,每个第一字线的第一部分竖直地延伸以形成一个或多个竖直取向的栅极电极,每个第二字线的第一部分竖直地延伸以形成一个或多个竖直取向的栅极电极。

3、在一些实施方式中,存储器装置还包括:多个第一侧字线拾取结构以及多个第二侧字线拾取结构,其中,每个第一侧字线拾取结构包括对应的第一字线的至少第二部分、对应的第一字线的第一部分的一部分、以及对应的第一字线的第三部分的一部分,其中,每个第二侧字线拾取结构包括对应的第二字线的至少第二部分、对应的第二字线的第一部分的一部分、以及对应的第二字线的第三部分的一部分。

4、在一些实施方式中,存储器装置还包括:第一多个接触结构以及第二多个接触结构,其中,第一多个接触结构中的每个接触结构设置在对应的第一侧字线拾取结构处,并且第二多个接触结构中的每个接触结构设置在对应的第二侧字线拾取结构处。

5、在一些实施方式中,第一第一字线的第一部分平行于第一第二字线的第一部分。

6、在一些实施方式中,每个第一字线的第一部分横向地延伸远离存储阵列的第一侧并且朝向存储阵列的第二侧横向地延伸。

7、在一些实施方式中,存储器装置还包括第一多行存储单元,第一多行存储单元中的每行具有多个存储单元,其中,每个第一字线的第一部分耦合到第一多行存储单元中的对应行的多个存储单元。

8、在一些实施方式中,每个第二字线的第一部分横向地延伸远离存储阵列的第二侧并且朝向存储阵列的第一侧横向地延伸。

9、在一些实施方式中,存储器装置还包括第二多行存储单元,第二多行存储单元中的每行具有多个存储单元,其中,每个第二字线的第一部分耦合到第二多行存储单元中的对应行的多个存储单元。

10、在一些实施方式中,每个第一字线的第三部分延伸远离存储阵列的第一侧并且朝向存储阵列的第二侧延伸,并且每个第二字线的第三部分延伸远离存储阵列的第二侧并且朝向存储阵列的第一侧延伸。

11、根据本公开的另一方面,一种存储器装置包括:存储阵列,其具有第一侧、与第一侧相对的第二侧、以及第三侧;第一字线,其至少部分地设置在存储阵列内,并具有第一部分、第二部分和第三部分,其中,第一字线的第一部分、第二部分和第三部分是彼此连续的;第二字线,其至少部分地设置在存储阵列内,并具有第一部分、第二部分和第三部分,其中,第二字线的第一部分、第二部分和第三部分是彼此连续的;以及第一侧字线拾取结构,其包括第一字线的第二部分、第一字线的第一部分的一部分、以及第一字线的第三部分的一部分,其中,第一字线的第一部分和第三部分彼此间隔开,并且第二字线的第一部分和第三部分彼此间隔开。

12、在一些实施方式中,第一字线的第一部分比第一字线的第三部分长,第二字线的第一部分比第二字线的第三部分长,并且第一字线和第二字线设置成使得第一字线的第一部分、第一字线的第三部分、第二字线的第一部分以及第二字线的第三部分均彼此平行。

13、在一些实施方式中,第一字线和第二字线设置成使得:第一字线的第一部分与存储阵列的第三侧相距第一距离,并且第二字线的第三部分与存储阵列的第三侧相距第一距离;并且第一字线的第三部分与存储阵列的第三侧相距第二距离,并且第二字线的第一部分与存储阵列的第三侧相距第二距离。

14、在一些实施方式中,存储器装置还包括:第三字线,其具有第一部分、第二部分和第三部分,其中,第三字线的第一部分、第二部分和第三部分是彼此连续的;以及第四字线,其具有第一部分、第二部分和第三部分,其中,第四字线的第一部分、第二部分和第三部分是彼此连续的,其中,第一字线的第一部分在位线方向上与第二字线的第一部分相邻,第二字线的第一部分在位线方向上与第三字线的第一部分相邻,并且第三字线的第一部分在位线方向上与第四字线的第一部分相邻。

15、在一些实施方式中,存储器装置还包括:第三字线,其具有第一部分、第二部分和第三部分,其中,第三字线的第一部分、第二部分和第三部分是彼此连续的;以及第四字线,其具有第一部分、第二部分和第三部分,其中,第四字线的第一部分、第二部分和第三部分是彼此连续的,其中,第一字线的第一部分在位线方向上与第二字线的第一部分相邻,第一字线的第一部分在位线方向上与第三字线的第一部分相邻,并且第三字线的第一部分在位线方向上与第四字线的第一部分相邻。

16、根据本公开的又一方面,一种半导体装置包括:存储阵列,其具有第一侧、与第一侧相对的第二侧、以及第三侧,并且包括多个存储行,每个存储行包括多个存储单元;第一字线,其中,第一字线具有第一部分、第二部分和第三部分,第一字线的第二部分设置得相较于第二侧更靠近第一侧,第一部分和第三部分彼此间隔开,并且第一字线耦合到第一存储行的多个存储单元;第二字线,其中,第二字线具有第一部分、第二部分和第三部分,第二字线的第二部分设置得相较于第一侧更靠近第二侧,第一部分和第三部分彼此间隔开,并且第二字线耦合到第二存储行的多个存储单元;第三字线,其中,第三字线具有第一部分、第二部分和第三部分,第三字线的第二部分设置得相较于第二侧更靠近第一侧,第一部分和第三部分彼此平行,并且第三字线耦合到第三存储行的存储单元;以及第四字线,其中,第四字线具有第一部分、第二部分和第三部分,第四字线的第二部分设置得相较于第一侧更靠近第二侧,第一部分和第三部分彼此平行,并且第四字线耦合到第四存储行的存储单元。

17、在一些实施方式中,第一字线、第二字线和第三字线设置成使得第一字线的第一部分与第二字线的第一部分相邻,并且也与第三字线相邻。

18、在一些实施方式中,第一字线的第三部分和第二字线的第一部分与存储阵列的第三侧相距相同的距离。

19、在一些实施方式中,第一字线、第二字线和第三字线设置成使得第二字线的第一部分与第一字线的第一部分相邻,并且也与第三字线的第一部分相邻。

20、在一些实施方式中,第二字线的第三部分和第一字线的第一部分与存储阵列的第三侧相距相同的距离。

21、根据本公开的又一方面,一种形成半导体结构的方法包括:在半导体衬底中蚀刻出第一沟槽和第二沟槽,第一沟槽具有第一沟槽侧壁和第二沟槽侧壁,第二沟槽具有第一沟槽侧壁和第二沟槽侧壁;形成设置在第一沟槽中的至少一个第一竖直取向的晶体管以及设置在第二沟槽中的至少一个第二竖直取向的晶体管;对导电材料的层进行图案化,使得形成多个字线,每个字线具有第一部分、与第一部分不平行且不共线的第二部分、以及与第一部分间隔开的第三部分;在第一竖直取向的晶体管与第二竖直取向晶体管之间形成间隙,以及采用至少一种电介质材料填充间隙。

22、在一些实施方式中,形成间隙包括:去除半导体衬底的设置在第一沟槽与第二沟槽之间的部分。

23、在一些实施方式中,该方法还包括:对导电材料的层进行图案化,使得第一组的多个字线将其对应的第二部分设置在存储阵列的第一侧,并且第二组的多个字线将其对应的第二部分设置在存储阵列的第二侧。

24、在一些实施方式中,第一组的多个字线的第二部分平行于第二组的多个字线的第二部分。

25、在一些实施方式中,第一组的多个字线和第二组的多个字线彼此交替设置。

26、在一些实施方式中,该方法还包括:在多个字线的每个第二部分处形成字线拾取结构。

27、在一些实施方式中,导电材料包括至少一种金属。

28、在一些实施方式中,第一沟槽包括第一沟槽底部,第二沟槽包括第二沟槽底部,并且该方法还包括:去除导电材料的层的位于第一沟槽底部上方的第一部分,以及去除导电材料的层的位于第二沟槽底部上方的第二部分。

29、在一些实施方式中,该方法还包括:对至少一种电介质材料进行平坦化。

30、在一些实施方式中,至少一种电介质材料包括至少硅的氧化物。

31、根据本公开的又一方面,一种形成半导体结构的方法包括:提供具有顶表面和底表面的衬底;将至少第一沟槽和第二沟槽蚀刻到衬底中,第一沟槽和第二沟槽均具有至少第一沟槽侧壁、第二沟槽侧壁和沟槽底部,其中,设置在第一沟槽与第二沟槽之间的衬底结构为第一沟槽提供第二沟槽侧壁并且为第二沟槽提供第一沟槽侧壁;形成第一电介质层,第一电介质层与第一沟槽的第一沟槽侧壁、第二沟槽侧壁和沟槽底部相邻,并且与第二沟槽的第一沟槽侧壁、第二沟槽侧壁和沟槽底部相邻;形成导电材料的层,导电材料的层具有第一表面以及与第一表面相对的第二表面,其中,第一表面的第一部分与第一电介质层相邻,并且导电材料的层的第二表面设置成使得在导电材料的设置在第一沟槽和第二沟槽的第一沟槽侧壁上的第二表面与导电材料的设置在第一沟槽和第二沟槽的对应的第二沟槽侧壁上的第二表面之间存在第一间隙;从每个沟槽中去除导电材料的层的第一部分,使得第一电介质层的设置在第一沟槽和第二沟槽的沟槽底部上的部分暴露;采用第二电介质层填充第一沟槽和第二沟槽的第一间隙;去除第二电介质层的上部部分、导电材料的层的设置在每个沟槽的第一沟槽侧壁上的上部部分、以及导电材料的层的设置在第一沟槽和第二沟槽的第二沟槽侧壁上的上部部分,由此,在第一沟槽和第二沟槽的上部部分中形成第二间隙;采用第三电介质层填充位于第一沟槽和第二沟槽的上部部分中的第二间隙;以及通过去除第三电介质层的位于第一沟槽中的第一部分、第三电介质层的位于第二沟槽中的第二部分、导电材料的层的位于第一沟槽中的第一下部部分、导电材料的层的位于第二沟槽中的第二下部部分、以及衬底结构的上部部分,来形成第三间隙。

32、在一些实施方式中,第二电介质层和第三电介质层两者包括第一电介质材料。

33、在一些实施方式中,第一电介质材料包括硅的氧化物。

34、在一些实施方式中,该方法还包括:对导电材料的层进行图案化,使得形成多个字线,每个字线具有第一部分、垂直于第一部分的第二部分、以及垂直于第二部分并且平行于第一部分的第三部分。

35、在一些实施方式中,该方法还包括:对导电材料的层进行图案化,使得第一组的多个字线将其对应的第二部分设置在存储阵列的第一侧从而提供多个第一侧字线拾取结构,并且第二组的多个字线将其对应的第二部分设置在存储阵列的第二侧从而提供多个第二侧字线拾取结构。

36、根据本公开的又一方面,一种形成用于存储阵列的字线的方法包括:提供半导体衬底,半导体衬底具有顶表面;蚀刻出包括至少第一沟槽和第二沟槽的多个沟槽,其中,第一沟槽具有第一沟槽侧壁、第二沟槽侧壁和沟槽底部,并且第二沟槽具有第一沟槽侧壁、第二沟槽侧壁和沟槽底部;将第一电介质层设置在第一沟槽的第一沟槽侧壁、第二沟槽侧壁和沟槽底部上,并且还将第一电介质层设置在第二沟槽的第一沟槽侧壁、第二沟槽侧壁和沟槽底部上;形成图案化的金属层,使得在存储阵列中形成多个字线,多个字线中的每个字线具有第一部分、设置为与第一部分成第一角度的第二部分、以及与第一部分间隔开并且设置为与第二部分成第二角度的第三部分;以及对图案化的金属层进行图案化,使得图案化的金属层的位于沟槽底部上方的部分被去除,其中,第一组的多个字线将其对应的第二部分设置在存储阵列的第一侧,并且第二组的多个字线将其对应的第二部分设置在存储阵列的第二侧。

37、在一些实施方式中,设置在第一沟槽与第二沟槽之间的半导体结构形成第一沟槽的第二沟槽侧壁,并且形成第二沟槽的第一沟槽侧壁。

38、在一些实施方式中,该方法还包括:去除半导体结构的上部部分。

39、在一些实施方式中,该方法还包括:在蚀刻出多个沟槽之前,在半导体衬底的顶表面上形成氮化硅层;对氮化硅层进行图案化;在第一沟槽中形成至少一个竖直取向的栅极电极,并且在第二沟槽中形成至少一个竖直取向的栅极电极;以及在去除半导体结构的上部部分之前,去除氮化硅层的设置在半导体结构上的部分。

40、在一些实施方式中,该方法还包括:在半导体结构的至少下部部分上方沉积第三电介质层。

41、提及这些例示性实施方式不是为了限制或限定本公开,而是为了提供示例来帮助理解本公开。在具体实施方式中讨论了额外的实施方式,并且在其中提供了进一步的描述。

- 还没有人留言评论。精彩留言会获得点赞!