制造约瑟夫森结的方法与流程

本公开涉及减少两步沉积工艺中的结电阻变化。

背景技术:

1、量子计算是一种相对新的计算方法,其利用量子效应诸如基态和纠缠的叠加以比传统的数字计算机更有效地执行某些计算。与以位(例如“1”或“0”)的形式存储和操纵信息的数字计算机相反,量子信息处理器件能够使用量子位(qubit)来操纵信息。量子位可以指能够进行多种状态的叠加(例如处于“0”和“1”状态两者的数据)和/或能够将处于多种状态的数据本身叠加的量子器件。根据常规术语,量子系统中“0”和“1”状态的叠加可以例如表示为α│0>+β│1>。数字计算机的“0”和“1”状态分别类似于量子位的│0>基态和│1>基态。值│α│2表示量子位处于│0>态的概率,而值│β│2表示量子位处于│1>基态的概率。

技术实现思路

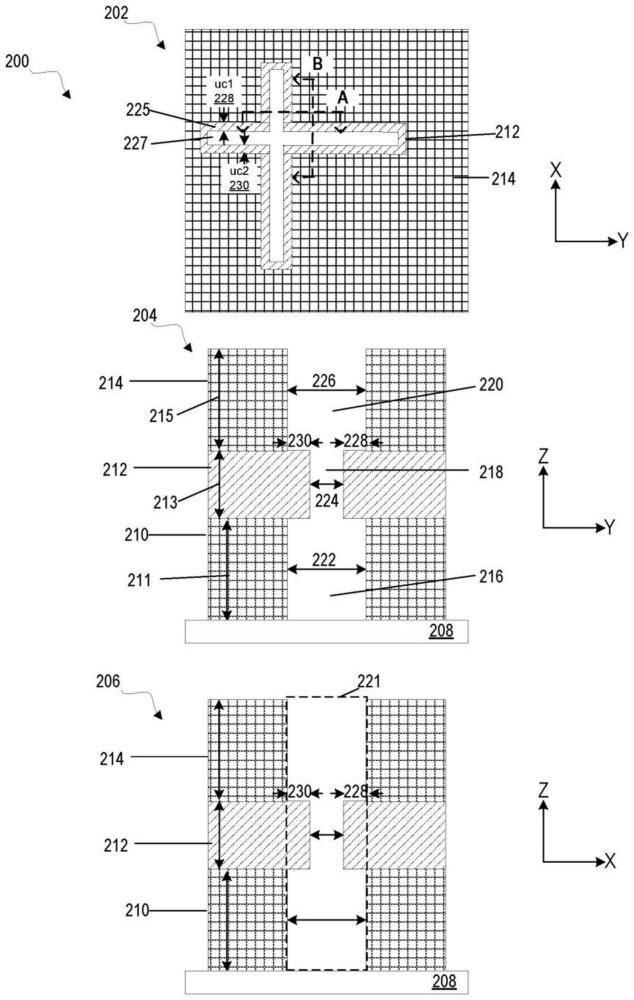

1、通常,本说明书中描述的主题的一个创新方面可以体现为以下方法,该方法包括以下动作:提供电介质基板;在电介质基板上形成第一抗蚀剂层;在第一抗蚀剂层上形成第二抗蚀剂层;以及在第二抗蚀剂层上形成第三抗蚀剂层。第一抗蚀剂层包括延伸穿过第一抗蚀剂层的厚度的第一开口,第二抗蚀剂层包括在第一开口之上对准并延伸穿过第二抗蚀剂层的厚度的第二开口,第三抗蚀剂层包括在第二开口之上对准并延伸穿过第三抗蚀剂层的厚度的第三开口。

2、这些方法的实施方式可以可选地包括以下特征中的一个或更多个。在一些实施方式中,第一开口、第二开口和第三开口中的每个的厚度沿着垂直于电介质基板的表面的第一方向延伸,其中第一开口、第二开口和第三开口中的每个具有沿着与第一方向正交的第二方向延伸的相应宽度,并且其中第二开口的宽度小于第一开口的宽度且小于第三开口的宽度。

3、在一些实施方式中,第一抗蚀剂层中的第一开口和第三抗蚀剂层中的第三开口通过以第一图案曝光第一抗蚀剂层、第二抗蚀剂层和第三抗蚀剂层来限定,第二抗蚀剂层中的第二开口通过以第二图案曝光第一抗蚀剂层、第二抗蚀剂层和第三抗蚀剂层来限定。然后第一抗蚀剂层、第二抗蚀剂层和第三抗蚀剂层被随后显影。

4、在一些实施方式中,第一材料层通过第一开口、第二开口和第三开口以相对于基板的第一沉积角度沉积,第二材料层通过第一开口、第二开口和第三开口以相对于基板的第二沉积角度沉积。第一材料层和第二材料层可以是超导材料。

5、在一些实施方式中,在沉积第二材料层之前,执行第一材料层的表面氧化以提供第一材料层的氧化区域。在一些实施方式中,第一材料层的一部分、氧化区域的一部分和第二材料层的一部分形成量子信息处理器件(例如约瑟夫森结)的一部分,其中量子信息处理器件可以是量子位。

6、在一些实施方式中,例如使用蚀刻工艺去除第一抗蚀剂层、第二抗蚀剂层、第三抗蚀剂层和过量的沉积材料。

7、在一些实施方式中,在沉积第一材料层期间电介质基板和材料沉积源根据相对于彼此的第一取向布置,在第二材料层的沉积期间电介质基板和材料沉积源根据相对于彼此的第二取向布置,其中第一取向不同于第二取向。可以在沉积第一材料层之后并且在沉积第二材料层之前旋转基板。可选地,在沉积第一材料层之后并且在沉积第二材料层之前,可以相对于电介质基板改变材料沉积源的位置。

8、在一些实施方式中,第一开口、第二开口和第三开口限定暴露电介质基板的表面的掩模开口区域。第一底切宽度可以由掩模开口区域的第一侧的第二开口的第一边缘与第三开口的第一边缘之间的距离限定。第二底切宽度可以由与掩模开口区域的第一侧正好相反的掩模开口区域的第二侧的第二开口的第二边缘与第三开口的第二边缘之间的距离限定。第一底切宽度可以近似为零。

9、在一些实施方式中,第二底切宽度大于在第一沉积工艺期间沉积在第三抗蚀剂层的侧壁上的材料的厚度。

10、在一些实施方式中,在沉积第一材料层期间,掩模开口区域的第一侧比掩模开口区域的第二侧更靠近材料沉积源。

11、可以实施本说明书中描述的主题的特定实施方式从而实现以下优点中的一个或更多个。例如,在一些实施方式中,这里公开的技术可以用于减少结变化和/或提高基板上的最邻近的约瑟夫森结之间的性能均匀性。在一些实施方式中,当前公开的技术通过减小掩模层内的开口区域的尺寸变化来改善量子信息处理器件的性能的整个均匀性,所述尺寸变化可能由沉积参数(例如沉积角度)和/或在掩模层的侧壁上的偶然沉积引起。另外,通过减小掩模层内的开口区域的尺寸变化(例如由于沉积粗糙度引起的开口区域的波纹度),可以改善量子信息处理器件的性能的整个均匀性,该尺寸变化可能由沉积层中的晶粒生长和晶粒形态(例如铝晶粒生长)的效果引起。通过减小掩模层内的开口的尺寸变化,可以使使用该掩模层制造的量子信息处理器件(诸如约瑟夫森结和量子位)的形式和形状更加均匀。进而,所得到的量子信息处理器件表现出更均匀的操作特性,这有助于使用和设计用于使用单个控制器驱动/操作一组两个或更多量子位的全局微波驱动方法。在一些实施方式中,通过减少由沉积层的晶粒生长和晶粒形态(例如晶粒边界)破坏的结的数目,减少沉积层中的晶粒生长效应提高了量子信息处理器件的产率(例如约瑟夫森结和量子位)。

12、本说明书中描述的主题的一个或更多个实施方式的细节在附图和以下的描述中阐述。主题的其它特征、方面和优点将从说明书、附图和权利要求书变得明显。

技术特征:

1.一种方法,包括:

2.根据权利要求1所述的方法,包括:

3.根据权利要求2所述的方法,其中所述第一沉积角度和所述第二沉积角度不同。

4.根据权利要求3所述的方法,其中所述第一沉积角度与所述第二沉积角度正交。

5.根据权利要求2所述的方法,其中所述第一沉积角度是相对于所述电介质基板的所述表面的倾斜角,以及

6.根据权利要求5所述的方法,其中所述第二沉积角度使得所述第二光致抗蚀剂层的一部分和/或靠近所述第一开口、第二开口和/或第三开口的边缘的先前沉积的第一材料层阻挡所述第一开口、第二开口和/或第三开口内的来自第二沉积的沉积材料中的至少一些。

7.根据权利要求2所述的方法,其中用于所述第一层沉积的所述第一位置和用于所述第二层沉积的所述第二位置彼此正交。

8.根据权利要求2所述的方法,其中所述第一材料层和所述第二材料层是超导材料。

9.根据权利要求2所述的方法,还包括在沉积所述第二材料层之前,执行所述第一材料层的表面氧化以提供所述第一材料层的氧化区域。

10.根据权利要求9所述的方法,其中所述第一材料层的一部分、所述氧化区域的一部分和所述第二材料层的一部分形成量子信息处理器件的部分。

11.根据权利要求2所述的方法,还包括去除所述第一光致抗蚀剂层、所述第二光致抗蚀剂层、所述第三光致抗蚀剂层。

12.根据权利要求2所述的方法,包括在沉积所述第一材料层之后并且在沉积所述第二材料层之前,旋转所述基板。

13.根据权利要求2所述的方法,包括在沉积所述第一材料层之后并且在沉积所述第二材料层之前,改变所述材料沉积源相对于所述电介质基板的位置。

14.根据权利要求2所述的方法,其中所述第三开口包括限定在所述第三开口的第一侧和所述第二光致抗蚀剂层的第一侧之间的第一底切宽度,并且包括限定在所述第三开口的第二侧和所述第二光致抗蚀剂层的第二侧之间的第二底切宽度,其中所述第一底切宽度大于所述第二底切宽度。

15.根据权利要求14所述的方法,其中所述第二底切宽度为零。

16.根据权利要求14所述的方法,其中所述第一开口、所述第二开口和所述第三开口中的每个具有沿着与所述第一方向和所述第二方向正交的第三方向延伸的对应附加宽度,

17.根据权利要求2所述的方法,其中所述第一层对应于约瑟夫森结的第一部分,以及其中所述第二层对应于所述约瑟夫森结的第二部分。

18.根据权利要求17所述的方法,其中所述约瑟夫森结形成量子位的部分。

19.一种方法,包括:

20.根据权利要求19所述的方法,其中在所述第二位置中所述电介质的所述表面相对于所述材料沉积源的相对取向从所述第一位置旋转90度。

21.根据权利要求19所述的方法,还包括在沉积所述第二材料层之前,执行所述第一材料层的表面氧化以提供所述第一材料层的氧化区域,

技术总结

一种减少使用两步沉积工艺制造的量子信息处理器件中的结的结电阻变化的方法。在一个方面,一种方法包括:提供电介质基板(208);在电介质基板上形成第一抗蚀剂层(210);在第一抗蚀剂层上形成第二抗蚀剂层(212);以及在第二抗蚀剂层上形成第三抗蚀剂层(214)。第一抗蚀剂层包括延伸穿过第一抗蚀剂层的厚度的第一开口(216),第二抗蚀剂层包括在第一开口之上对准并延伸穿过第二抗蚀剂层的厚度的第二开口(218),第三抗蚀剂层包括在第二开口之上对准并延伸穿过第三抗蚀剂层的厚度的第三开口(220)。

技术研发人员:B·J·伯克特

受保护的技术使用者:谷歌有限责任公司

技术研发日:

技术公布日:2024/5/10

- 还没有人留言评论。精彩留言会获得点赞!