一种锁相环电路、系统及锁相环锁定时间的确定方法与流程

本发明涉及集成电路测试,特别是涉及一种锁相环电路、系统及锁相环锁定时间的确定方法。

背景技术:

1、在当前数字信号的时钟频率较高的情况下,随之出现电路系统内对于信号的建立、保持时间以及时钟抖动的要求愈加提高。通过展频时钟(spread spectrum clock,ssc)方式以降低时钟在基频和奇次谐波的幅度达到降低电磁辐射峰值的目的。

2、但是,ssc时钟在处理过程中会引入额外的抖动,通常情况下,若出现抖动,锁相环(phase locked loops,pll)会利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,确定锁相环的锁定时间。针对于当前的pll锁定时间的确定过程,人为抓取信号以进行计算,在人为抓取过程中,会存在延时或者抓取不准确,导致pll锁定时间计算与实际pll锁定时间存在偏差,另外,锁定时间的确定过程对应的锁定场景较为单一,导致在后续评估锁定能力存在偏差和覆盖场景单一。

3、因此,如何提高pll锁定时间的准确性和锁定能力以保证电路系统正常工作是本领域技术人员亟需要解决的技术问题。

技术实现思路

1、本发明的目的是提供一种锁相环电路、系统及锁相环锁定时间的确定方法,以解决当前pll锁定时间确定过程通过人为抓取信号出现的延时和不准确,导致pll锁定时间存在偏差和锁定场景单一的技术问题。

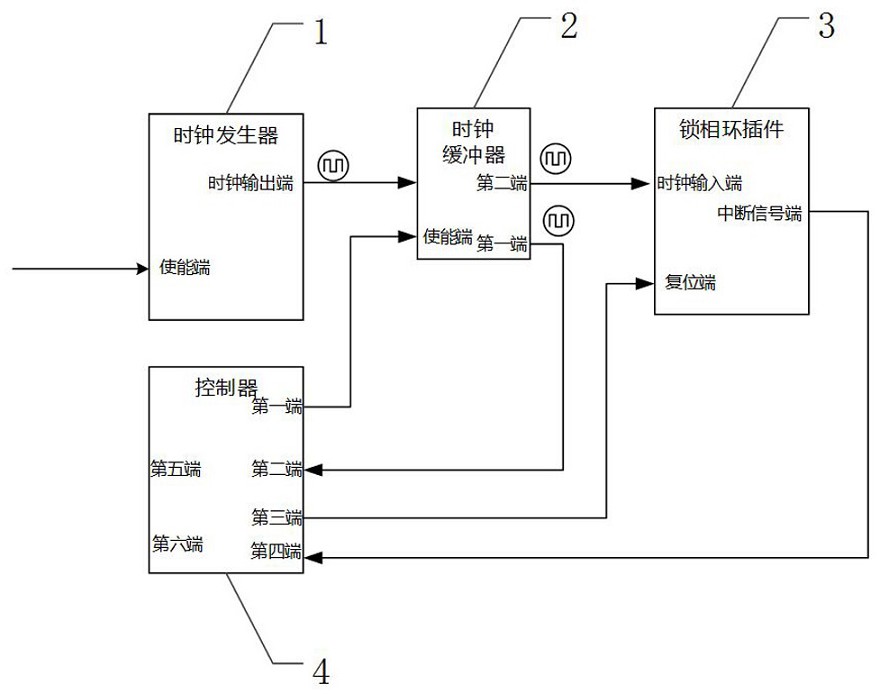

2、为解决上述技术问题,本发明提供一种锁相环电路,锁相环电路包括时钟发生器、时钟缓冲器和锁相环插件;

3、所述时钟发生器与所述时钟缓冲器连接,用于获取当前调制深度对应的时钟信号;

4、所述时钟缓冲器与所述锁相环插件连接;

5、控制器分别与所述时钟缓冲器和所述锁相环插件连接,用于根据预设的锁定场景,控制所述时钟缓冲器发送所述时钟信号的时间和所述锁相环插件的解复位时间分别得到第一时间和第二时间,根据所述第一时间和所述第二时间确定所述预设的锁定场景对应的锁定时间。

6、一方面,所述控制器与所述时钟缓冲器连接,包括:

7、所述控制器的第一端与所述时钟缓冲器的使能端连接;

8、所述时钟缓冲器的第一输出端与所述控制器的第二端连接。

9、另一方面,所述控制器与所述锁相环插件连接,包括:

10、所述控制器的第三端连接所述锁相环插件的复位端;

11、所述锁相环插件的中断信号端连接所述控制器的第四端。

12、另一方面,还包括开关单元;

13、所述开关单元分别与所述控制器、所述时钟发生器连接;

14、所述控制器还用于控制所述开关单元对应输出的所述当前调制深度。

15、另一方面,所述开关单元包括第一开关、第二开关、第一电阻和第二电阻;

16、所述第一开关的第一端连接所述第一电阻的第一端;所述第一电阻的第二端连接电源;

17、所述第一开关的第二端连接所述第二电阻的第一端,且连接所述时钟发生器的使能端;

18、所述第二电阻的第二端连接所述第二开关的第一端;所述第二开关的第二端接地;

19、所述控制器的第五端连接所述第一开关的控制端,所述控制器的第六端连接所述第二开关的控制端。

20、另一方面,所述开关单元包括第三开关、第四开关、第五开关、第六开关、第三电阻、第四电阻、第五电阻和第六电阻;

21、所述第三电阻的第一端连接所述第三开关的第一端,所述第四电阻的第一端连接所述第四开关的第一端,所述第三电阻的第二端和所述第四电阻的第二端均连接电源;

22、所述第三开关的第二端分别连接所述第五电阻的第一端和所述时钟发生器的使能端,所述第五开关的第一端连接所述第五电阻的第二端,所述第五开关的第二端接地;

23、所述第四开关的第二端分别连接所述第六电阻的第一端和所述时钟发生器的使能端,所述第六开关的第一端连接所述第六电阻的第二端,所述第六电阻的第二端接地;

24、所述控制器的第七端、第八端、第九端和第十端分别对应连接所述第三开关的控制端、所述第四开关的控制端、所述第五开关的控制端和所述第六开关的控制端。

25、另一方面,所述锁相环插件为锁相环芯片。

26、为解决上述技术问题,本发明还提供一种锁相环系统,包括上述所述的锁相环电路。

27、为解决上述技术问题,本发明还提供一种锁相环锁定时间的确定方法,应用于上述所述的锁相环电路,包括:

28、获取由时钟发生器输出的当前调制深度对应的时钟信号;

29、获取预设的锁定场景;

30、根据所述预设的锁定场景,控制时钟缓冲器发送所述时钟信号的时间和锁相环插件的解复位时间分别得到第一时间和第二时间;

31、根据所述第一时间和所述第二时间确定所述预设的锁定场景对应的锁定时间。

32、一方面,所述预设的锁定场景为经所述时钟缓冲器输出的所述时钟信号已到达所述锁相环插件且所述锁相环插件还未启动的场景,所述控制时钟缓冲器发送所述时钟信号的时间和锁相环插件的解复位时间分别得到第一时间和第二时间,包括:

33、获取所述时钟缓冲器发送所述时钟信号的时间;

34、根据所述时钟缓冲器发送所述时钟信号的时间确定反馈到控制器的所述第一时间;

35、获取所述锁相环插件预设的解复位时间,其中,所述解复位时间大于所述时钟缓冲器发送所述时钟信号的时间;

36、根据所述预设的解复位时间确定反馈到所述控制器的所述第二时间。

37、另一方面,所述预设的锁定场景为经所述时钟缓冲器输出的所述时钟信号未到达所述锁相环插件且所述锁相环插件已启动的场景,所述控制时钟缓冲器发送所述时钟信号的时间和锁相环插件的解复位时间分别得到第一时间和第二时间,包括:

38、获取所述锁相环插件预设的解复位时间;

39、根据所述预设的解复位时间确定反馈到控制器的所述第二时间;

40、获取所述时钟缓冲器发送所述时钟信号的时间,其中,所述时钟缓冲器发送所述时钟信号的时间大于所述预设的解复位时间;

41、根据所述时钟缓冲器发送所述时钟信号的时间确定反馈到所述控制器的所述第一时间。

42、另一方面,所述根据所述第一时间和所述第二时间确定所述预设的锁定场景对应的锁定时间,包括:

43、在所述预设的锁定场景为经所述时钟缓冲器输出的所述时钟信号已到达所述锁相环插件且所述锁相环插件还未启动的场景时,将所述第二时间与所述第一时间进行差值处理后确定的绝对值时间作为第一锁定时间,其中,所述第一锁定时间包含所述锁相环插件的未启动时间;

44、在所述预设的锁定场景为经所述时钟缓冲器输出的所述时钟信号未到达所述锁相环插件且所述锁相环插件已启动的场景时,将所述第二时间与所述第一时间进行差值处理后确定的绝对值时间作为第二锁定时间。

45、另一方面,在所述锁相环插件的数量为一个时,在确定所述第一锁定时间或所述第二锁定时间后,还包括:

46、获取锁定时间区间对应的锁定分数;

47、确定所述第一锁定时间或所述第二锁定时间位于所述锁定时间区间的各目标时间区间;

48、根据各所述目标时间区间确定对应的锁定分数以作为所述第一锁定时间或所述第二锁定时间对应的锁定能力。

49、另一方面,所述当前调制深度的类型包括第一调制深度、第二调制深度和第三调制深度,所述第一调制深度大于所述第二调制深度,所述第二调制深度大于所述第三调制深度,在所述锁相环插件的数量为多个且各所述锁相环插件的型号不同时,在确定所述第一锁定时间或所述第二锁定时间后,还包括:

50、在所述当前调制深度为所述第一调制深度时,获取各所述锁相环插件对应的各所述第一锁定时间或各所述第二锁定时间;

51、在多个所述锁相环插件的所述第一锁定时间或各所述第二锁定时间内筛选出所述第一锁定时间或所述第二锁定时间内对应最小的锁定时间,并将所述最小的锁定时间对应的锁相环插件作为目标锁相环插件;

52、若各所述第一锁定时间或各所述第二锁定时间在各自的锁定时间内相同,则将所述第一调制深度调制至所述第二调制深度,以作为新的所述当前调制深度;

53、返回至所述获取各所述锁相环插件对应的各所述第一锁定时间或各所述第二锁定时间的步骤,直至选择出目标锁相环插件。

54、另一方面,所述当前调制深度的类型的确定过程,包括:

55、获取所述控制器对应开关单元的输入输出状态,其中,所述输入输出状态为所述控制器与所述开关单元连接对应的电平状态;

56、获取所述控制器连接所述时钟缓冲器对应的使能状态和时钟状态列表;

57、根据所述时钟状态列表、所述输入输出状态和所述使能状态确定所述当前调制深度的类型。

58、本发明提供的一种锁相环电路,时钟发生器与时钟缓冲器连接,用于获取当前调制深度对应的时钟信号;时钟缓冲器与锁相环插件连接;控制器分别与时钟缓冲器和锁相环插件连接。

59、本发明的有益效果在于控制器基于当前调制深度对应的时钟信号和预设的不同锁定场景,控制时钟缓冲器发送时钟信号的时间和锁相环插件的解复位时间的先后顺序以测试在不同的锁定场景下对应得到的第一时间和第二时间,再根据第一时间和第二时间的差值确定预设的锁定场景对应的锁定时间。本发明通过控制器抓取信号以得到精准的第一时间和第二时间,相对于当前的人为抓取时间确定的pll锁定时间,避免出现偏差,提高抓取信号的精准性和后续评估锁定能力的准确性,减少延时时间,提高抓取效率。另外,不同调制深度下对应的不同的预设锁定场景,使得本发明覆盖的锁定场景全面化,保证电路系统正常。

60、其次,本发明提供的控制器与时钟缓冲器连接、控制器与锁相环插件连接,通过控制时钟缓冲器的使能端实现时钟信号送达锁相环插件的时间顺序,对输入的时钟信号进行检测,记录时钟送到锁相环插件的第一时间,通过释放锁相环插件的解复位时间实现锁相环插件的启动完成时刻的先后控制,实现模拟上述实施例中提到的两个锁定场景以确定对应的锁定时间,以便于后续对锁相环锁定能力的评估;通过控制器实现自动调整切换多种不同类型的ssc时钟输出,提高自动化测试程度。控制器通过配置连接开关单元的管脚状态,控制时钟发生器ssc模式控制管脚的电平状态,实现输出时钟型号的类型切换;将锁相环芯片做成插件(interposer)形式,不同厂家的锁相环芯片的插件与母板的接口定义保持一致,以便于在进行批量验证时,只需要更换插件即可,提高拆焊效率;通过两种不同的锁定场景设置,确定的第一时间和第二时间,以便于后续确定对应的锁定场景下的锁定时间;基于不同的锁定场景计算对应的锁定时间,以便于根据确定的锁定时间评估锁相环插件对不同模式输入时钟的锁定能力;基于多个锁相环插件下的不同的锁定深度下的各锁定场景对应的锁定时间确定的锁定能力进行的评估,通过锁定时间的长短映射出锁定能力较强的锁相环插件,提高锁定能力的评估准确性。

61、另外,本发明还提供了一种锁相环系统及锁相环锁定时间的确定方法,具有如上述锁相环电路相同的有益效果。

- 还没有人留言评论。精彩留言会获得点赞!