一种超高速交织采样AD芯片同步方法与流程

本发明涉及电数字数据处理,尤其涉及一种超高速交织采样ad芯片同步方法。

背景技术:

1、超高速ad(模数转换)芯片的一种主流架构为采用大量的超低功耗的ad核交织拼接成低功耗超高速采样ad芯片。该拼接架构的每个ad内核工作前需要进行直流零偏、幅度一致性、采样孔径位置校正与反馈精确修正,从而确保每个ad内核的幅度相位响应尽可能达到一致,且采样孔径尽可能的接近理想的交织采样位置,在数十gsps(吉采样次/秒)甚至数百gsps采样条件下实现较好的无杂散动态范围sfdr指标。目前该交织架构的ad芯片可实现片内ad内核间采样孔径fs(飞秒)级反馈修正,但不能实现片间ad内核同步采集。

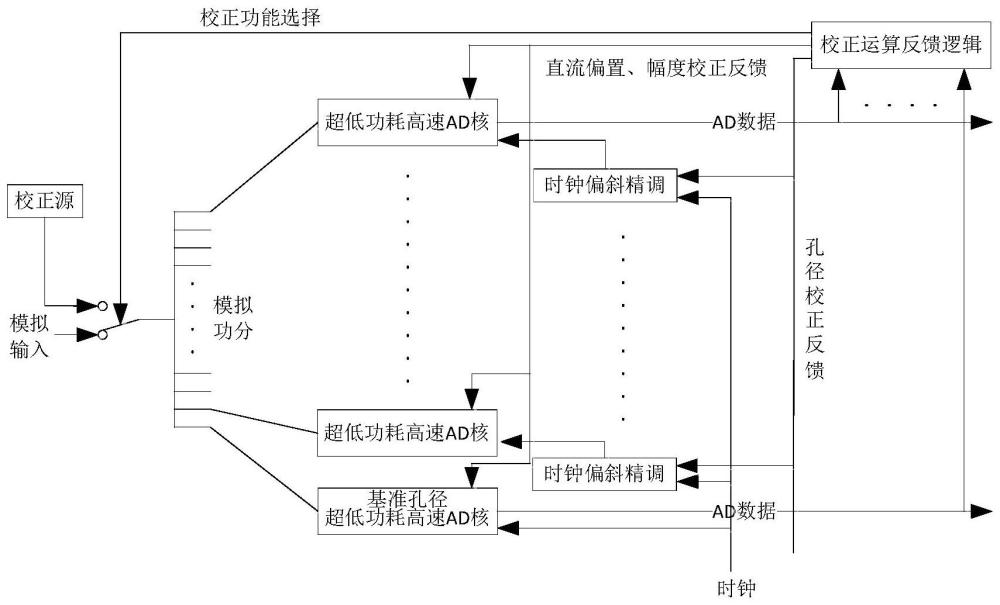

2、ad芯片内部交织架构如图1所示,图1中输入采样时钟可以是ad内核工作时钟,直接在ad芯片内部分配给时钟偏斜精单元,经校正运算反馈逻辑控制精确调整到理想采样孔径位置;输入采样时钟也可以是之间输入超高速采样钟,经多相分频(可减小调节延迟范围)后送时钟偏斜精单元,降低反馈控制难度。

3、现有超高速ad芯片的采样速率可达到数十gsps(吉采样次/秒)甚至百gsps采样。当采样率达到数十gsps的速度后,采样周期变为10ps量级,传统的ad芯片间同步方法因为器件运行速度、高低温飘移等原因,难以在采样时钟与同步信号间建立稳定的时序关系,从而不能解决超高速ad芯片的片间同步问题。

技术实现思路

1、为了解决上述问题,本发明提出一种超高速交织采样ad芯片同步方法,使ad芯片内部的超低功耗高速ad核在保留精确交织功能的同时,还能在规模应用中方便使用较低速的脉冲/周期信号的实现超高速ad芯片片间同步。

2、本发明采用的技术方案如下:

3、一种超高速交织采样ad芯片同步方法,包括:

4、构建具备时序同步基准功能ad核的非对称交织ad芯片架构:基于对称交织ad芯片架构,将一个ad核采样孔径位置固定,作为交织架构的时序基准,即基准ad核;以基准ad核的采样孔径位置为准,通过反馈控制方法调节剩余ad核的采样孔径位置至预设距离,实现非对称交织ad芯片的内部孔径交织以及数据同步。

5、进一步地,所述非对称交织ad芯片的基准ad核仅进行直流偏置和幅度校正,采样孔径位置固定不变,由外供时钟相位控制。

6、进一步地,所述非对称交织ad芯片的基准ad核需屏蔽或取消时钟占空比优化调节功能。

7、进一步地,所述非对称交织ad芯片的外部电路能够通过包括偶数分频在内的方法产生符合ad时钟占空比要求的时钟。

8、进一步地,还包括构建所述非对称交织ad芯片的内部数据帧:在所述非对称交织ad芯片内部,通过基准ad核使每个ad核输出时间相对输入时钟固定时序位置,并通过外部时钟频率使所述非对称交织ad芯片内部调节ad数据缓冲寄存器到外部时钟相同的相位,将不同时钟相位的ad数据逐级缓冲到外部时钟直接驱动的寄存器,从而形成以外部时钟频率为节拍的所述非对称交织ad芯片内部数据帧。

9、进一步地,所述非对称交织ad芯片的每个内部数据桢包含所有ad核的采样数据。

10、进一步地,所述非对称交织ad芯片的对外输出接口以内部数据帧为不可分割的基本单位进行传输。

11、进一步地,所述非对称交织ad芯片的ad核按顺序采样交织,数据输出到第一级缓冲寄存器,满足寄存器的建立保持时序要求,同时满足第二级寄存器的建立保持时序要求;数据传输到第二级数据寄存器,成为满足顺序稳定性的内部数据帧。

12、进一步地,还包括构建所述非对称交织ad芯片与时钟缓冲器的温控逻辑:对所述非对称交织ad芯片与时钟缓冲器进行温度闭环控制,从而将所述非对称交织ad芯片与时钟缓冲器的平衡温度控制在预设变化范围内。

13、进一步地,对所述非对称交织ad芯片与时钟缓冲器进行温度闭环控制的方法包括:基于半导体温度致冷片进行温度闭环控制。

14、本发明的有益效果在于:

15、在本发明中,采用相对低速的基准ad内核同步来实现高速交织ad芯片同步,数量级的降低了高速交织ad芯片的同步难度。同时运用温度环控的方法,使高速交织ad芯片的同步精度有了数量级的提升,满足了宽带同步的性能需求。

技术特征:

1.一种超高速交织采样ad芯片同步方法,其特征在于,包括:

2.根据权利要求1所述的一种超高速交织采样ad芯片同步方法,其特征在于,所述非对称交织ad芯片的基准ad核仅进行直流偏置和幅度校正,采样孔径位置固定不变,由外供时钟相位控制。

3.根据权利要求1所述的一种超高速交织采样ad芯片同步方法,其特征在于,所述非对称交织ad芯片的基准ad核需屏蔽或取消时钟占空比优化调节功能。

4.根据权利要求1所述的一种超高速交织采样ad芯片同步方法,其特征在于,所述非对称交织ad芯片的外部电路能够通过包括偶数分频在内的方法产生符合ad时钟占空比要求的时钟。

5.根据权利要求1所述的一种超高速交织采样ad芯片同步方法,其特征在于,还包括:

6.根据权利要求5所述的一种超高速交织采样ad芯片同步方法,其特征在于,所述非对称交织ad芯片的每个内部数据桢包含所有ad核的采样数据。

7.根据权利要求5所述的一种超高速交织采样ad芯片同步方法,其特征在于,所述非对称交织ad芯片的对外输出接口以内部数据帧为不可分割的基本单位进行传输。

8.根据权利要求5所述的一种超高速交织采样ad芯片同步方法,其特征在于,所述非对称交织ad芯片的ad核按顺序采样交织,数据输出到第一级缓冲寄存器,满足寄存器的建立保持时序要求,同时满足第二级寄存器的建立保持时序要求;数据传输到第二级数据寄存器,成为满足顺序稳定性的内部数据帧。

9.根据权利要求1所述的一种超高速交织采样ad芯片同步方法,其特征在于,还包括:

10.根据权利要求9所述的一种超高速交织采样ad芯片同步方法,其特征在于,对所述非对称交织ad芯片与时钟缓冲器进行温度闭环控制的方法包括:基于半导体温度致冷片进行温度闭环控制。

技术总结

本发明公开了一种超高速交织采样AD芯片同步方法,包括构建具备时序同步基准功能AD核的非对称交织AD芯片架构:基于对称交织AD芯片架构,将一个AD核采样孔径位置固定,作为交织架构的时序基准,即基准AD核;以基准AD核的采样孔径位置为准,通过反馈控制方法调节剩余AD核的采样孔径位置至预设距离,实现非对称交织AD芯片的内部孔径交织以及数据同步。本发明采用相对低速的基准AD内核同步来实现高速交织AD芯片同步,数量级的降低了高速交织AD芯片的同步难度。同时运用温度环控的方法,使高速交织AD芯片的同步精度有了数量级的提升,满足了宽带同步的性能需求。

技术研发人员:刘建高,孙盼杰,李侃

受保护的技术使用者:中国电子科技集团公司第二十九研究所

技术研发日:

技术公布日:2024/5/10

- 还没有人留言评论。精彩留言会获得点赞!