一种外部时钟同步和内部时钟双向软切换电路及方法与流程

本发明涉及半导体锁相环,具体地,涉及一种外部时钟同步和内部时钟双向软切换电路及方法。

背景技术:

1、电源管理芯片广泛应用于便携电子、汽车、照明led、家电等领域,其中,开关电源dc-dc因其高效率,占据主要份额。现代开关电源更加集成化、系统化,经常要与外部的系统控制,如mcu等协同工作;同时也追求高功率,需要多芯片并联。这些复杂的控制要求通常需要在开关电源内集成可同步外部时钟的锁相环pll。

2、如图1所为一款内置pll的开关电源芯片简图。开关电源内置的pll&inter_clk模块负责接收、同步外部系统mcu或主并联芯片master产生的时钟信号;若没有外部时钟信号,则内部自己产生时钟,送到pwm发生器,再通过驱动器,驱动功率mos管,不断地导通、关断,为负载输出恒压或者恒流。

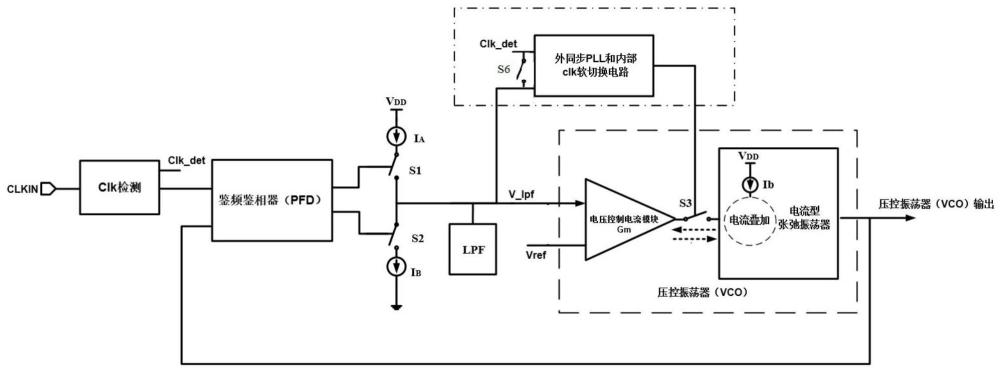

3、传统的pll&inter_clk模块电路如图2所示,clkin引脚用于接收外部时钟输入,clk检测模块检测外部有无时钟信号,产生clk_det信号,比如:高电平代表此时有外部时钟输入,低电平代表此时没有外部时钟输入。鉴频鉴相器pfd、电荷泵cp、电容低通滤波器lpf、压控振荡器vco组成经典的电荷泵锁相环cppll。其中,压控振荡器vco经常由电压控制电流模块gm和电流型张弛振荡器构成。

4、当系统或者主并联芯片发出特定频率的时钟信号,送到clkin引脚和clk检测模块后,产生clk_det=1,外部时钟信号会进一步被送到鉴频鉴相器pfd,开关s3闭合,鉴频鉴相器pfd比较外部时钟信号和压控振荡器vco由原本的内部工作频率之间的频率、相位差,调整开关s1、s2通断时间,改变v_lpf电压,该电压与vref之间产生正负的电压差,从而改变电压控制电流模块gm流出或抽取的电流,最终改变电流型张弛振荡器的频率,使压控振荡器vco输出频率快速同步、锁相外部时钟信号;当系统或者主并联芯片停止发出特定频率的时钟信号,clk检测模块检测不到时钟信号,则产生clk_det=0,立即断开开关s3,从芯片slave停止同步功能,电压控制电流模块gm原本流出或流入的电流被快速切断,转由内部固定的偏置电流ib产生内部时钟信号。

5、但是,原本的内部时钟频率和外部频率往往相差几百khz到上mhz,这种硬切换会使pll&inter_clk模块产生频率陡变,如图3所示,驱动功率mos管的pwm频率、恒压或恒流输出也会剧烈变化,对负载产生不利的影响。例如,恒压输出时,可能有电压过冲,超过负载耐压,系统控制长期这样硬切换,容易使负载产生可靠性问题,甚至损坏负载;恒流驱动led时,可能出现明显的亮度变化,甚至闪频,影响led使用寿命或客户使用体验。

技术实现思路

1、针对现有技术中存在的问题,本发明提供了一种外部时钟同步和内部时钟双向软切换电路及方法,来消除这种外同步频率和内部固定工作频率之间的硬切换,且过渡区时长可调,使dc-dc恒压或恒流输出变化缓和,提高开关电源芯片整体的可靠性和寿命。

2、为实现上述技术目的,本发明采用如下技术方案:一种外部时钟同步和内部时钟双向软切换电路,设置于pll&inter_clk模块上,包括:电压比较器、计数锁存器、开关控制逻辑电路、上电流源i4、下电流源i5、第四开关s4和第五开关s5,所述电压比较器的输出端分别与计数锁存器的输入端、开关控制逻辑电路连接,所述计数锁存器的输出端与电压比较器的使能端连接,所述开关控制逻辑电路的输出端分别与第四开关s4、第五开关s5连接,所述第四开关s4还与上电流源i4连接,所述第五开关s5还与下电流镜i5连接;

3、外部时钟信号撤离后,所述电压比较器不断检测输入电压信号v_lpf,并将输入电压信号v_lpf与vref比较,若输入电压信号v_lpf<vref,通过开关控制逻辑电路控制第四开关s4导通,使上电流源i4给输入电压信号v_lpf充电;若输入电压信号v_lpf>vref,通过开关控制逻辑电路控制第五开关导通,使下电路源i5给输入电压信号v_lpf放电,实现软切换过程;

4、所述计数锁存器用于记录压控振荡器vco输入电压信号v_lpf趋近vref调整的次数。

5、进一步地,所述pll&inter_clk模块包括:clk检测模块、鉴频鉴相器pfd、第一开关s1、第二开关s2、第一偏置电流ia、第二偏置电流ib、电容低通滤波器lpf、压控振荡器vco,所述clk检测模块的clkin引脚用于接收外部时钟输入,所述clk检测模块的输出端与鉴频鉴相器pfd的第一输入端连接,所述鉴频鉴相器pfd的第一输出端与第一开关s1的一端、第一偏置电流ia的输出端串联,所述第一偏置电流ia的输入端与工作电压vdd连接,所述鉴频鉴相器pfd的第二输出端与第二开关s2的一端连接,所述第二开关s2的一端还与第一开关s1的另一端、电容低通滤波器lpf、压控振荡器vco的输入端连接,所述第二开关s2的另一端与第二偏置电流ib的输入端连接,所述第二偏置电流ib的输出端接地;所述压控振荡器vco的输出端分别与开关电源dc-dc中的驱动器、鉴频鉴相器pfd的第一输入端连接。

6、进一步地,所述压控振荡器vco包括:电压控制电流模块gm、第三开关s3、电流型张弛振荡器,所述电压控制电流模块gm的输出端与第三开关s3的一端连接,所述第三开关s3的另一端与电流型张弛振荡器的输入端连接,所述电流型张弛振荡器的输出端分别与开关电源dc-dc中的驱动器、鉴频鉴相器pfd的第一输入端连接。

7、进一步地,还设有第六开关s6,所述电压比较器的第一输入端分别与第一开关s1的另一端、第二开关s2的一端、电容低通滤波器lpf的输入端、第六开关s6的一端、电压控制电流模块gm的第一输入端、第四开关s4的输入端、第五开关s5的输出端连接,所述电压比较器的第二输入端与第六开关s6的另一端连接;所述电压比较器的clk_det信号端与clk检测模块的clk_det信号端连接。

8、进一步地,所述计数锁存器的输出端还分别与第三开关s3、第六开关s6连接。

9、进一步地,所述开关控制逻辑电路包括:第一反相器inv1、第二反相器inv2、或门or2和与门and2,所述第一反相器inv1的输入端与clk检测模块的clk_det信号端连接,所述第一反相器inv1的输出端分别与第二反相器inv2的输入端、与门and2的第一输入端连接,所述第二反相器inv2的输出端与或门or2的第一输入端连接,所述或门or2的第二输入端、与门and2的第二输入端均与电压比较器的输出端连接,所述或门or2的输出端与第四开关s4连接,所述与门and2的输出端与第五开关s5连接。

10、进一步地,所述第四开关s4为pmos晶体管,所述pmos晶体管的栅极与或门or2的输出端连接,所述pmos晶体管的源极与上电流源i4的输出端连接,所述上电流源i4的输入端与工作电压vdd连接;所述pmos晶体管的漏极与电压比较器的第一输入端连接。

11、进一步地,所述第五开关s5为nmos晶体管,所述nmos晶体管的栅极与与门and2的输出端连接,所述nmos晶体管的源极与下电流源i5的输入端连接,所述下电流源i5的输出端接地;所述nmos晶体管的漏极与电压比较器的第一输入端连接。

12、进一步地,本发明还提供了一种所述外部时钟同步和内部时钟双向软切换电路的双向软切换方法,具体过程如下:

13、当外部时钟信号撤离后,clk检测模块产生clk_det=0的信号,外部时钟同步和内部时钟双向软切换电路使能,开始不断检测并调整输入电压比较器的电压信号v_lpf,具体地,当电压信号v_lpf<vref时,电压比较器的输出结果通过开关控制逻辑电路内的或门or2控制第四开关s4的导通,通过与门and2控制第五开关s5的断开,上电流源i4不断对电压信号v_lpf上挂的电容低通滤波器lpf充电,使电压信号v_lpf逐渐增大,趋近vref;当电压信号v_lpf>vref时,电压比较器输出结果通过开关控制逻辑电路控制第四开关s4的断开、第五开关s5的导通,下电流源i5不断对电压信号v_lpf上挂的电容低通滤波器lpf放电,使v_lpf不断减小,趋近vref;

14、最终电压信号v_lpf在vref附近来回调整,电压比较器输出高、低翻转,被计数锁存器计数,计数满之后锁存结果,并断开第三开关s3、第四开关s4、第五开关s5,关闭电压比较器,导通第六开关s6,此时,电压控制电流模块gm两端相等,使得pll&inter_clk模块产生的电路不会有频率陡变;

15、当外部时钟信号加载时,clk检测模块产生clk_det=1的信号,保持断开第六开关s6、第四开关s4、第五开关s5,关闭电压比较器,并清空计数锁存器的锁存,接通第三开关s3,进入同步外部时钟的锁相环pll过程。

16、与现有技术相比,本发明具有如下有益效果:本发明外部时钟同步和内部时钟双向软切换电路在外部时钟信号切换成内部时钟时,不断检测调整压控振荡器vco的输入电压信号v_lpf,使其趋近目标电压,实现外部时钟同步锁相和内部clk之间平稳的过渡切换,且通过电容低通滤波器lpf的电容大小,调节上电流镜i4、下电流镜i5的大小,实现软切换的切换速度、过渡区时长可调,可以大幅改善硬切换带来的开关电源芯片工作频率陡变,实现dc-dc恒压或恒流输出的平稳变化,提高开关电源芯片的可靠性。

- 还没有人留言评论。精彩留言会获得点赞!