一种系统同步方法与流程

[0001]

本发明涉及一种系统同步方法,特别是一种用于复杂系统需要同步控制或同步测量等场合的系统同步方法。

背景技术:

[0002]

在机械、电子、电气、电力、计算机、化工、测控等控制等领域,通常需要对复杂系统进行同步。例如:ups系统需要对逆变器输出进行同步控制;在并联传动系统中,需要对多个传动控制器进行同步调节控制;在仪器仪表领域,需要对输出的多个信号进行同步;在测控领域,需要进行同步测量,以获取同一时刻某个被测量在不同空间位置的分布。同步性能直接关系到系统的性能,甚至关系到系统的安全可靠运行。

技术实现要素:

[0003]

本发明的目的在于,提供一种系统同步方法。本发明具有结构简单,成本低、可靠性高和实用性好的特点。

[0004]

本发明的技术方案:一种系统同步方法,其特征在于,通过同步总线将若干个装置的同步模块连接在一起,所述同步模块包括信号发生模块、开关控制模块、同步总线侦听模块和开关s1;信号发生模块的信号输出端连接开关s1的一端,信号发生模块的定时溢出段连接用于控制开关s1的开关控制模块,开关控制模块连接同步总线侦听模块,开关s1的另一端与信号发生模块、同步总线侦听模块连接。

[0005]

前述的系统同步方法中,所述同步模块包括:

[0006]

信号发生模块,其输入与电源power相连,输出信号pwm

i

与开关s1的输入相连,定时溢出信号ov_i与开关控制模块的使能en相连;接通电源时,信号发生模块延时定时器开始工作。延时t

d

后,信号发生模块启动一个周期定时器,产生一个周期信号pwm

i

及周期溢出脉冲信号ov_i;pwm

i

由开关控制模块确定是否将其输出到同步总线称为同步信号syn,ov_i用于使能开关控制模块工作;

[0007]

开关s1,其输入与pwm

i

相连,输出与同步总线相连,由开关控制模块ctl

i

控制,起到pwm

i

接通或断开同步总线的功能;默认状态下s1是断开的;

[0008]

开关控制模块,其使能端en与信号发生模块的ov_i相连,锁死端lock与同步总线相连,复位端rst与同步总线侦听模块的reset相连,输出ctl

i

与开关s1相连;开关控制模块在reset为低时,根据ov_i与同步总线的同步信号syn之间的关系控制开关s1的接通或断开,一旦reset为高,则将开关控制模块复位为初始通电时状态;

[0009]

同步总线侦听模块,其输入与同步总线相连,输出reset与开关控制模块的rst相连,同步总线侦听模块用于监测同步总线的信号丢失时间是否超出设定时间。一旦超出设定时间,则reset输出高电平,否则输出低电平。

[0010]

与现有技术相比,具有以下优势:

[0011]

一、较基于通信方式实现同步的方案相比,本发明给出的同步方法具有结构更简

单;

[0012]

二、本发明的同步方法支持热插拔,以及能有效抑制因接触不良、元件失效或者干扰等原因导致syn丢失,具有很强的抗干扰能力和稳定可靠性;

[0013]

三、较基于通信方式实现同步方案,本发明无需数据交换,同步信号的频率无需太高,对同步总线的阻抗要求很低;

[0014]

四、本发明给出的同步方法不需要通信协议,不会影响模块内部软件的运行,可以对不同型号,不同厂家的模块进行同步,因而具有广泛的兼容性;

[0015]

五、本发明的同步方法所需电子元件均为常用元件和模块,具有更低的成本和更高的性价比。

附图说明

[0016]

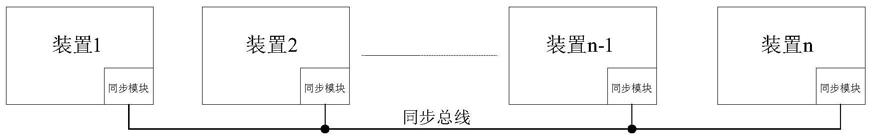

图1是本发明的结构图;

[0017]

图2是同步模块的结构图;

[0018]

图3a是运行时序图;

[0019]

图3b是热插入模块条件下运行时序图;

[0020]

图3c是热拔出非syn模块运行时序图;

[0021]

图3d是热拔出原syn模块运行时序图;

[0022]

图3e是syn丢失时间小于设定值时序图;

[0023]

图3f是syn丢失时间大于等于设定值时序图;

[0024]

图3g是不同时间段拔出两个原syn模块时序图。

具体实施方式

[0025]

下面结合附图和实施例对本发明作进一步的说明,但并不作为对本发明限制的依据。

[0026]

实施例。一种系统同步方法,构成如图1所示,系统一般由n个装置组成,通过同步总线将若干个装置的同步模块连接在一起,如图2所示,所述同步模块包括信号发生模块、开关控制模块、同步总线侦听模块和开关s1;信号发生模块的信号输出端连接开关s1的一端,信号发生模块的定时溢出段连接用于控制开关s1的开关控制模块,开关控制模块连接同步总线侦听模块,开关s1的另一端与信号发生模块、同步总线侦听模块连接。同步总线上的信号即为同步信号syn

[0027]

具体的是,所述同步模块包括:

[0028]

信号发生模块,其输入与电源power相连,输出信号pwm

i

与开关s1的输入相连,定时溢出信号ov_i与开关控制模块的使能en相连;信号发生模块实现功能为:系统通电时,信号发生模块启动内部上电延时功能。延时结束后,内部周期为t的定时器开始工作,输出占空比为0.5的pwm

i

和周期性溢出脉冲信号ov_i,pwm

i

和ov_i具有相同的周期。开关控制模块的输出信号ctl

i

,控制开关s1的接通或断开,进而控制pwm

i

与同步总线的接通或断开,起到总线控制开关作用,实现同步信号syn的产生。

[0029]

开关s1,其输入与pwm

i

相连,输出与同步总线相连,由开关控制模块ctl

i

控制,起到pwm

i

接通或断开同步总线的功能;开关s1由ctl

i

控制,起到pwm

i

接通/断开同步总线的功能。

[0030]

开关控制模块,其使能端en与信号发生模块的ov_i相连,锁死端lock与同步总线相连,复位端rst与同步总线侦听模块的reset相连,输出ctl

i

与开关s1相连;开关控制模块基本功能为:在输入端lock不存在上升沿及reset为低时,如果ov_i出现上升沿,则ctl

i

由低电平变换为高电平,并锁存。此时开关s1闭合,信号pwm

i

输出到同步总线上,产生syn。syn一经产生,一方面开关控制模块lock出现上升沿,开关控制模块对en锁死,不再接收ov_i,ctl

i

保持为高电平。另一方面同步总线侦听模块内部的定时器的当前定时值清零。由于syn为周期性信号,只要syn周期小于同步总线侦听模块定时器的周期,则同步总线侦听模块的输出reset就不会为高。

[0031]

同步总线侦听模块,其输入与同步总线相连,输出reset与开关控制模块的rst相连,同步总线侦听模块用于监测同步总线的信号丢失时间是否超出设定时间。同步总线侦听模块的基本功能为:用于监测同步总线上的同步信号syn是否丢失。如果丢失超过侦听模块内部设定的定时值,则输出复位信号reset为高,否则为低。定时器的当前定时值采用单增模式,当定时值达到设定值时,定时值保持为设定值,并且reset保持为高。一旦监测到syn出现上升沿,则定时器的当前定时值立即复位为零,reset复位为零。

[0032]

默认初始状态时,所有信号发生模块的输出为低,也就是pwm

i

、ctl

i

、ov_i和reset均为低电平,开关s1为断开。同步模块工作过程如下:

[0033]

一、由于模块运行时间先后差异,导致n个周期性溢出脉冲信号ov_i出现时间不同。最早出现的ov_i使能开关控制模块将ctl

i

锁存为高,s1闭合,pwm

i

输出到同步总线,syn信号出现。syn一经出现,lock必然会检测到上升沿,开关控制模块的en被锁死,不受ov_i的控制,ctl

i

保持不变。同样的,syn一经出现,则同步总线侦听模块当前定时值和reset清零,总线侦听模块不动作。上述开关控制模块和同步总线侦听模块的运行实现syn一经产生,所以同步模块的开关控制模块均被锁死,进而实现系统能自动竞争出有且唯一的同步信号syn;

[0034]

二、系统已经存在syn的情况下,在某时刻插入新的装置进入系统时,由于新装置的同步模块从上电到输出pwm

i

和ov_i信号需要延时。在此延时时间内,新装置的同步模块的开关控制模块一定会接收到syn,进而锁死开关控制模块的en,ctl

i

始终为零,s1保持断开状态。同理,新装置的同步总线侦听模块也一定会在此时间内接收到syn,将同步总线侦听模块定时器的当前定时值清零,reset保持为低。上述过程说明,新插入装置不影响现有的syn信号;

[0035]

三、存在syn的情况下,在某时刻从系统中拔出装置,则存在以下两种不同情况:

⑴

拔出的装置不产生syn信号,由功能图及分析可知,其对系统的syn信号不产生影响;

⑵

拔出的装置是产生syn信号,则系统中syn信号丢失。在syn信号丢失期间,系统中所有同步总线侦听模块的定时器值均持续增加。当同步总线侦听模块的定时器值达到设定值时,reset信号为高电平,此时系统中所有开关控制模块均被复位到默认状态,其en接收ov_i。由于系统中所有信号发生模块的ov

i

并没有被同步复位,因而ov_i同样存在时间上的差异,进而再次竞争出新的syn信号。

[0036]

四、因短时间强烈振动导致接触不良等因素,导致syn丢失时间没有超过同步总线侦听模块定时器设定值时,同步总线一定会出现syn。只要出现syn,同步总线侦听模块的定时计数器被清零,不输出reset信号,pwm输出控制模块不被复位,系统正常工作。

[0037]

已知相关参数为:

①

t

s

=0.1s;

②

pwm信号占空比为0.5;

③

上电延时t

d

=1s;

④

syn连续丢失定时设定时间0.5秒。下面针对图3所示a、b、c、d、e、f、g七种不同情况,结合图3所示时序图对其进行详细分析。

[0038]

(a)假定在t=0时刻给5个同步模块上电,5个同步模块运行时间存在差异,其对应pwm溢出中断信号出现时间存在先后关系(或者同时给5个同步模块上电,由于线路阻抗、元件参数不一致等因素必然导致5个同步模块运行时间存在差异)。由图3a可知,序号为1的同步模块在经过0.1秒延迟之后,其pwm溢出信号ov_1出现时间最早,开关控制模块电路的en出现上升沿跳变,触发ctl从0翻转为1,开关s1闭合,pwm1输出到syn,即pwm1竞争成为syn。在syn出现之后,开关控制模块电路的lock出现上升沿跳变,锁死en功能,系统中所有开关控制模块电路不接收ov_i信号,其他同步模块电路的ctl

i

保持为0,开关s1保持断开,实现pwm2~pwm5与syn断开。与此同时,syn的出现将同步总线侦听模块的定时值清零;

[0039]

(b)在上述(a)的条件下,在0.4秒时刻热插入了序号为6的同步模块。由于序号为6的模块在上电延迟的1秒钟内syn信号没有丢失(即在0.4秒~1.4秒之间一直存在syn信号),所以序号为6的模块在1.4秒之前必然收到了syn信号,从而将序号为6的模块的en锁死和同步总线侦听模块的定时值清零。由于en锁死,所以序号为6的模块ctl保持为0,s1断开,不影响同步信号syn;

[0040]

(c)在上述(a)的条件下,在1.3秒、1.5秒、1.6秒和2.2秒分别热拔出了序号为3、序号为5、序号为2和序号为4的同步模块。由于这些电路非syn信号提供模块,因而不影响syn;

[0041]

(d)在上述(a)的条件下,在1.9秒热拔出了序号为1的同步模块。由于为syn信号提供模块,因而syn信号丢失。当syn连续丢失5个周期(即处于2.4秒时)时,同步总线侦听模块的reset会出现一个高电平。reset高电平复位开关控制模块,重新开放en,接收ov_i信号。在2.4秒之后,序号2的信号发生模块溢出信号ov_2出现时间最早,所以开关控制模块输出的控制信号ctl从0翻转为1,s1接通,pwm2输出到syn,即pwm2竞争成为新的syn。在新的syn出现之后,系统中所有开关控制模块的lock再次出现上升沿,禁止所有开关控制模块接收ov_i信号,保证其他同步模块的ctl

i

保持为0,开关s1保持断开,实现pwm

i

(i≠2)与syn断开。与此同时,syn的出现再次将同步总线侦听模块的定时值清零;

[0042]

(e)在上述(a)的条件下,由于短时间剧烈振动导致接触不良等原因,pwm1在1.9秒~2.3秒丢失了信号,即syn没有信号。由于syn连续丢失的个数小于5个,因而不会触发竞争新的syn。所以,当2.3秒时刻pwm1再次出现,syn信号还是pwm1;

[0043]

(f)在上述(a)的条件下,因接触不良、干扰或元件失效等原因,pwm1在1.9秒~2.7秒丢失了信号,即syn没有信号。由于syn连续丢失的个数大于或等于5个,因而触发竞争新的syn。此时,序号为2的同步模块的pwm溢出中断ov_2距离2.4秒最近,因而pwm2竞争为新的syn信号。其详细工作过程与(d)一致,不再赘述。

[0044]

(g)在上述(a)的条件下,在1.5秒热拔出了序号为1的同步模块。由于为syn信号提供模块,因而syn信号丢失。当syn连续丢失5个周期(即2.0秒)时,系统会在pwm2~pwm5内重新竞争出新的syn。由于序号为2的同步模块其pwm溢出中断ov_2距离2.0秒最近,因而pwm2竞争为新的syn信号。在新的syn出现之后,在2.3秒热拔出了序号为2的同步模块。由于为新的syn信号提供模块,因而syn信号再一次丢失。当syn连续丢失5个周期(即2.8秒)时,系统会在pwm3~pwm5内重新竞争出新的syn,又因为序号为3的同步模块的pwm溢出中断ov_3距

离2.8秒最近,因而pwm3竞争为更新的syn信号。在更新的syn出现之后,其详细工作过程与(d)一致,不再赘述。

[0045]

综上所述,本发明提供的一种直流高压逆变系统具有结构简单,成本低和实用性好等特点。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1